#### **DOCTORAL THESIS**

# Fault-Tolerant Galvanically Isolated DC-DC Converters with Zero Redundancy

Abualkasim Ahmed Ali Bakeer

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2023

#### TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 18/2023

## Fault-Tolerant Galvanically Isolated DC-DC Converters with Zero Redundancy

ABUALKASIM AHMED ALI BAKEER

#### TALLINN UNIVERSITY OF TECHNOLOGY

School of Engineering

Department of Electrical Power Engineering and Mechatronics

This dissertation was accepted for the defence of the degree 12/05/2023

**Supervisor**: Dr. Andrii Chub

Department of Electrical Power Engineering and Mechatronics

Tallinn University of Technology

Tallinn, Estonia

**Co-supervisor**: Dr. Dmitri Vinnikov

Department of Electrical Power Engineering and Mechatronics

Tallinn University of Technology

Tallinn, Estonia

**Opponents**: Prof José Antonio Cobos

Center of Industrial Electornics Technical University of Madrid

Madrid, Spain

Prof Sheldon Williamson

Department of Electrical, Computer and Software Engineering

Ontario Tech University

Oshawa, Canada

Defence of the thesis: 13/06/2023, Tallinn

#### **Declaration:**

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted for doctoral or equivalent academic degree.

Abualkasim Bakeer

Signature

Copyright: Abualkasim Bakeer, 2023 ISSN 2585-6898 (publication)

ISBN 978-9949-83-979-7 (publication)

ISSN 2585-6901 (PDF)

ISBN 978-9949-83-980-3 (PDF)

Printed by Auratrükk

#### TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 18/2023

# Null-liiasusega veatolerantsed galvaanilise isolatsiooniga alalispingemuundurid

ABUALKASIM AHMED ALI BAKEER

#### Contents

| List of Publications                                                                                                                                                                                                                                                                                           | 7                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Author's Contribution to the Publications                                                                                                                                                                                                                                                                      | 8                                |

| Abbreviations                                                                                                                                                                                                                                                                                                  | 9                                |

| Symbols                                                                                                                                                                                                                                                                                                        | 10                               |

| 1 Introduction                                                                                                                                                                                                                                                                                                 | 12                               |

| 1.3 Aims, Hypotheses, and Research Tasks                                                                                                                                                                                                                                                                       | 13<br>14                         |

| 1.6 Experimental Setup and Equipment                                                                                                                                                                                                                                                                           | 15<br>16                         |

| 2 Literature Review                                                                                                                                                                                                                                                                                            | 18<br>19                         |

| 2.2.2 Topologies with Redundant Capacitors                                                                                                                                                                                                                                                                     | 20<br>21                         |

| 3 Proposed Fault-Tolerant Zero-Redundancy Series Resonant Converter                                                                                                                                                                                                                                            | 23<br>25<br>27<br>29             |

| 4 Reliability-Oriented Design of the SRC-Based Fault-tolerant DC-DC converter wi Redundancy                                                                                                                                                                                                                    | 31<br>32<br>34<br>34<br>35<br>35 |

| 5 Self-Healing Fault-Tolerant PV Microconverter 5.1 Design Guidelines for PV Applications 5.2 Fault Diagnosis and Detection Methods 5.2.1 SCF of the Primary-Side MOSFETs 5.2.2 OCF of the Secondary-side MOSFETs 5.2.3 SCF of the Secondary-Side MOSFETs 5.3 PV Power Curtailment during Post-Fault Operation | 38<br>40<br>41<br>42<br>43       |

| 5.4 Experimental Results                                                                                                                                                                                                                                                                                       |                                  |

| 5.6 Summary                   | 51  |

|-------------------------------|-----|

| 6 Conclusions and Future Work | 53  |

| List of Figures               | 55  |

| List of Tables                | 57  |

| References                    | 58  |

| Acknowledgments               | 62  |

| Abstract                      | 63  |

| Lühikokkuvõte                 | 64  |

| Appendix                      | 65  |

| Curriculum vitae              | 152 |

| Elulookirjeldus               | 153 |

#### **List of Publications**

A list of the author's publications, based on which the thesis has been prepared:

- [PAPER-I] A. Bakeer, A. Chub, and D. Vinnikov, "Full-Bridge Fault-Tolerant Isolated DC-DC Converters: Overview of Technologies and Application Challenges," in IEEE Power Electronics Magazine, vol. 9, no. 3, pp. 45–55, Sept. 2022, doi: 10.1109/MPEL.2022.3196565.

- [PAPER-II] **A. Bakeer**, A. Chub, and D. Vinnikov, "Study of MOSFET Post-Fault Operation in Fault-Tolerant DC-DC Converters," in proc. IEEE 7<sup>th</sup> International Energy Conference (ENERGYCON), 2022, pp. 1–5, doi: 10.1109/ENERGYCON53164.2022.9830216.

- [PAPER-III] **A. Bakeer**, A. Chub, and D. Vinnikov, "Short-Circuit Fault Detection and Remedial in Full-Bridge Rectifier of Series Resonant DC-DC Converter Based on Inductor Voltage Signature," in proc. IEEE 61<sup>st</sup> International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), 2020, pp. 1–6, doi: 10.1109/RTUCON51174.2020.9316482.

- [PAPER-IV] A. Bakeer, A. Chub, A. Blinov, and J.-S. Lai, "Wide Range Series Resonant DC-DC Converter with a Reduced Component Count and Capacitor Voltage Stress for Distributed Generation," in Energies, vol. 14, no. 8, MDPI AG, p. 2051, Apr. 07, 2021. doi: 10.3390/en14082051.

- [PAPER-V] A. Bakeer, A. Chub, D. Vinnikov, and F. Blaabjerg, "Effect of Mission Profile Resolution on Photovoltaic Energy Yield Prediction in Python and MATLAB," in proc. IEEE 15<sup>th</sup> International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), 2021, pp. 1–5, doi: 10.1109/CPE-POWERENG50821.2021.9501222.

- [PAPER-VI] **A. Bakeer**, A. Chub, and Y. Shen, "Reliability Evaluation of Isolated Buck-Boost DC-DC Series Resonant Converter," in IEEE Open Journal of Power Electronics, vol. 3, pp. 131–141, 2022, doi: 10.1109/OJPEL.2022.3157200.

- [PAPER-VII] **A. Bakeer**, A. Chub, and D. Vinnikov, "Self-Healing Photovoltaic Microconverter with Zero Redundancy and Accurate Low-Cost Fault Detection," in IEEE Transactions on Industrial Electronics, accepted for publication, 2023, doi: 10.1109/TIE.2023.3250836.

#### **Author's Contribution to the Publications**

Contribution to the papers in this thesis are:

- [PAPER-I] Abualkasim Bakeer, as the primary author, was responsible for the methodology and preparing the survey of topologies. He also developed the reliability part associated with the faulty state of the converter with and without the power curtailment. He wrote the first draft and prepared the response to the editor and reviewers during the peer-review process.

- [PAPER-II] Abualkasim Bakeer, as the primary author, was responsible for the methodology, software, and experimental validation. He wrote the paper's first draft and drew all the paper's figures. He was responsible for submitting and contacting the conference during the publication step. He prepared the PowerPoint presentation and presented the article physically at the Latvian conference in May 2022.

- [PAPER-III] Abualkasim Bakeer, as the primary author, was responsible for the methodology, software, and simulation validation. He wrote the first draft of the paper. He was responsible for submission and contacting the conference during the publication step. He prepared the PowerPoint presentation and presented the paper online at the virtual conference event in Latvia.

- [PAPER-IV] Abualkasim Bakeer, as the primary author, was responsible for the main idea, methodology, software, and experimental validation. He wrote the first draft of the paper. He was also responsible for preparing the response to the editor and reviewers during the peer-review process.

- [PAPER-V] Abualkasim Bakeer, as the primary author, has developed the methodology of the paper and prepared the required software based on Python and MATLAB. In addition, he wrote the first draft and prepared the presentation for the conference.

- [PAPER-VI] Abualkasim Bakeer, as the primary author, was responsible for the main idea, methodology, software, and experimental validation. He wrote the first draft of the paper and drew all the figures. He was responsible for submission and contacting the journal during the publication step. He was also responsible for preparing the response to the editor and reviewers during the peer-review process.

- [PAPER-VII] Abualkasim Bakeer, as the primary author, was responsible for the main idea, methodology, software, and experimental validation. He wrote the first draft of the paper and drew all the figures. He was responsible for submission and contacting the journal during the publication step. He was responsible for preparing the response to the editor and reviewers during the peer-review process.

#### **Abbreviations**

AC Alternating current

APWM Asymmetric pulse width modulation

DC Direct current

FFT Fourier fast transform

FHR Forced half resonance

FT Fault-tolerant

GND Ground IB Input bridge

IBBC Isolated buck-boost converter

IEEE Institute of Electrical and Electronics Engineers

IGBT Insulated-gate bipolar transistor

LLC Inductor-Inductor-Capacitor resonant converter

MG Microgrid

MIL-HDBK-217F Military Handbook: Reliability Prediction of Electronic Equipment

MOSFET Metal-oxide-semiconductor field-effect transistor

MPP Maximum power point

MPPT Maximum power point tracking

MTTF Mean time to failure

OB Output bridge

OCF Open-circuit fault

P&O Perturb and observe

PCB Printed circuit board

PSM Phase-shift modulation

PV Photovoltaic

PWM Pulse width modulation

RESs Renewable energy sources

SRC Series resonant converter

SCF Short-circuit fault

Si Silicon

SiC Silicon carbide

TMC Topology morphing control

UPS Uninterrupted power supply

VDR Voltage doubler rectifier

ZR Zero-redundancy

ZVS Zero voltage switching

#### **Symbols**

$I_{PV}$  PV current (A)  $V_{PV}$  PV voltage (V)  $V_{in}$  Input voltage (V)

$I_{Lr}$ Resonant inductor current (A) $Z_r$ Resonant impedance ( $\Omega$ ) $F_{sw}$ Switching frequency (Hz) $T_{sw}$ Switching period (s) $F_r$ Resonant frequency (Hz)

P<sub>out</sub> Output power (W)

n Transformer turns ratio

QQuality factorRLoad resistance  $(\Omega)$  $L_r$ Resonant inductance (H) $C_r$ Resonant capacitance (F) $C_b$ Blocking capacitance (F) $C_{in}$ Input capacitance (F) $C_o$ Output capacitance (F)

$V_p$  Voltage of the primary winding of the transformer (V)  $V_s$  Voltage of the secondary winding of the transformer (V)

V<sub>1</sub> Output voltage of the inverter bridge (V)

V<sub>2</sub> Input voltage of the rectifier bridge (V)

*i*<sub>m</sub> Magnetizing current (A)

V<sub>Cr</sub> Resonant capacitor voltage (V)V<sub>Cb</sub> Blocking capacitor voltage (V)

$V_{Q2}$  Drain-source voltage of the switch  $Q_2$  (V)  $V_{Q4}$  Drain-source voltage of the switch  $Q_4$  (V)  $V_{g5,Q1}$  Gate-source voltage of the switch  $Q_1$  (V)  $V_{g5,Q2}$  Gate-source voltage of the switch  $Q_2$  (V)  $R_{d5,on}$  MOSFET drain-source resistance ( $\Omega$ )

$\lambda$  Item random failure rate (failure/10<sup>6</sup> hours)

$egin{array}{lll} \lambda_b & & {

m Basic failure \ rate} \ & & & & & & & & & \\ \pi_T & & & & {

m Temperature \ stress} \ & & & & & & & & \\ \pi_A & & & & {

m Application \ stress} \ & & & & & & \\ \pi_Q & & & {

m Quality \ stress} \ \end{array}$

$\pi_E$  Environmental stress  $\pi_C$  Capacitance stress Voltage stress

$\Pi_{PM}$  Technical and quality during manufacturing of the item

$\Pi_{Process}$  Stages of the item processes

$\lambda_{Phv}$  The physical failure rate of the item

N Number of converter components

$R_n$  Reliability of an item  $\lambda_{IBBC}$  IBBC failure rate

V<sub>IN,Nom</sub> Nominal input voltage (V)V<sub>MG</sub> DC microgrid voltage

B Peak-to-peak flux density in the core (Wb/m²)

*N<sub>p</sub>* Primary turns

$A_c$  The effective cross-section area of the core (cm<sup>2</sup>)

V<sub>IN,min</sub> Minimum input voltage (V) I<sub>IN,max</sub> Maximum input current (A)

$\omega_r$  Resonant angular frequency (rad/s)  $C_{oss}$  Parasitic output capacitance (F)

$T_{DT}$  Dead-time (s)

$\Delta V_{Cr}$  Peak-to-peak voltage ripple across the resonant capacitor (V)

V<sub>MPP</sub> PV voltage at maximum power point (V)

#### 1 Introduction

#### 1.1 Background

The leading cause of climate change in the world is the significant greenhouse gas emissions from human activities. In recent years, state and regional governments have proposed many incentives to curb climate change. With climate change becoming increasingly evident worldwide, electrification is considered a viable solution for the energy transition. Furthermore, the electrification of commonplace systems in industrial and residential sectors is expected to increase rapidly. One of the renewable energy sources is photovoltaic (PV) energy, which is considered environmentally friendly. Its use has increased significantly due to modern technologies that lead to lower prices. However, there are challenges associated with operating residential PV systems under partial shade conditions due to the accumulation of snow or leaves, shading from trees or rooftop structures, and partial shade from neighboring trees. Partial or opaque shading conditions could result in the wide variation of a photovoltaic module's global maximum power point voltage during the day and intermittent variations in daily solar irradiance. In addition, the PV module's input voltage decreases with shadow due to varying surrounding conditions.

With critical applications such as medical devices, aircrafts, and data centers, the conception of the reliability of the power converters has a high priority level when selecting the power converter from among the available ones on the global market [1]. In these cases, the power converter should provide continuity to feed the different services with existing faults despite the low performance, such as a high voltage/current ripple and low efficiency. Therefore, using fault-tolerant (FT) DC-DC converters in mission-critical applications is increasingly popular in order to defer after-fault maintenance [2]. Thus, the architecture of the interface DC-DC converter must have the following characteristics: the ability to control the input voltage in a wide range, galvanic isolation, high power density, and reliability so that high efficiency is ensured [3].

The isolated flyback and forward converters are usually employed for low-power applications. Despite these topologies being simple and cost-effective, they do not allow post-fault operation and can not regulate the wide range of input voltage variations. One possible way to overcome this is by adding (N+1) conventional redundancy, increasing the implementation and maintenance costs [PAPER-I]. The series resonant converter (SRC) is a promising isolated DC-DC converter topology that could regulate the wide input voltage variation with voltage buck or boost capability. In addition, it has the feature of direct power transfer into the load during most of the switching period. The basic concept of FT zero-redundancy SRC (ZR-SRC) is based on topology reconfiguration, allowing the converter to continue operating after a fault without adding more components.

#### 1.2 The Motivation of the Thesis

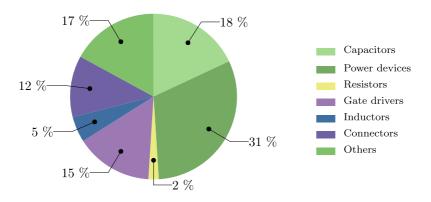

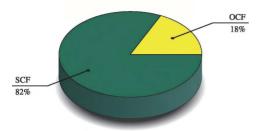

Power electronics converters are considered the most vulnerable to failure in the power conversion systems for renewable energy sources (RESs) compared to the other components. According to industrial statistics, power semiconductors represent approximately 31% of power electronic converter failures [4], as shown in Figure 1.1. Fault-tolerant implementation approaches can help to improve the reliability of power electronics converters. These approaches ensure the system remains operational even if a few components fail. A power electronics converter for PV module-level applications is usually rated to operate for at least 25 years. This duration corresponds to the expected lifetime of a PV module. A converter could employ fault tolerance to increase its lifetime towards this goal. The primary attention should be on the semiconductors fault, particularly the open- and short-circuit faults.

The research work in this thesis was conducted according to one of the research directions of the Power Electronics Group of Tallinn University of Technology. This thesis gathers knowledge and develops fault-tolerant zero-redundancy implementation techniques and corresponding fault diagnosis and detection methods for an SRC-based microconverter aimed at residential PV applications connected to the DC microgrid (MG). As a result, it should achieve minimum redundancy and, consequently, low implementation cost acceptable in residential applications. The Estonian Research Council supported the current work under the grant of PSG206 "DC-DC Converters with Ultra-Wide Regulation Range and Post-Fault Operation Capability" and PRG1086 "Future-Proof Power Electronic Systems for Residential Microgrids."

Figure 1.1 Distribution of faults in power electronics converter's components.

#### 1.3 Aims, Hypotheses, and Research Tasks

The main aim of the Ph.D. research project is to develop and experimentally confirm the concept of fault-tolerant zero-redundancy galvanically isolated DC-DC converters with a wide input voltage range and post-fault operation capability for interfacing PV modules into the residential DC microgrid. The proposed solution enables post-fault operation using low-cost techniques. As a result, a new generation of residential DC-coupled PV systems could be designed to provide satisfactory performance over the lifetime expectancy of the PV module. Furthermore, residential photovoltaic applications will be more affordable due to the lower lifecycle costs of the technology used.

#### **Hypotheses:**

- 1. The fault tolerance could be achieved in a galvanically isolated buck-boost DC-DC converter with zero redundant components.

- 2. Post-fault operation of DC-DC converters with reconfigurable switching cells could be achieved by utilizing the short-circuited switch as a current conducting path.

- 3. Taking into account the influence of the application-specific mission profile on the random failure rate of the converter's components would allow the possibility for application-tailored design and estimation of pre- and post-fault converter lifetime.

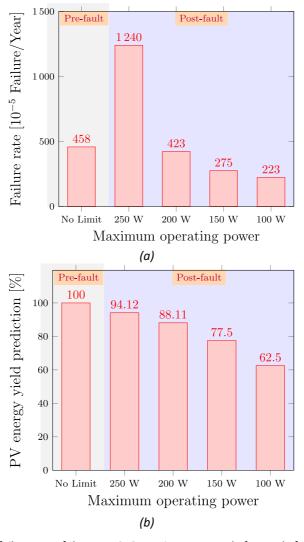

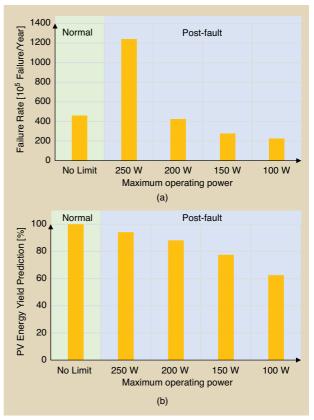

- 4. Applying an FT converter with input power curtailment in the PV applications would allow maintaining the same converter failure rate after the faulty state while reducing the annual energy yield by no more than 20%.

#### Research tasks:

- To review the FT isolated converters based on the SRC, showing the pros and cons

of each.

- 2. To investigate the feasibility of using the faulty switch as a current conduction path in the case of a short-circuit fault.

- 3. To compare the fault detection and diagnosis methods in terms of the complexity and cost of the implementation.

- 4. To synthesize the random failure rate estimation method for DC-DC converters, considering application-specific mission profiles.

- 5. To develop accurate and fast fault detection methods capable of localizing a faulty semiconductor component.

- 6. To develop a low-cost interface converter for residential PV modules that can maintain the failure rate as normal after the semiconductor's fault.

#### 1.4 Research Methods

The research methods used in the thesis are based on mathematical analysis of electronic circuits in the time domain using volt-second and ampere-second balance, numerical simulation models in PLECS and PSIM software, and experimental prototype verification. The converter loss model is built in the PLECS software using the datasheet parameters of the component used in the prototype. This allows us to synthesize thermal models that could be further used to investigate the reliability of the studied isolated buck-boost converter (IBBC) under the yearly mission profile of solar irradiation and ambient temperature. Computer simulations are generally performed in Python, MATLAB, PLECS, and PSIM software packages, most of which are available at the Tallinn University of Technology (TalTech). Altium Designer was used for the design of electric circuits and PCB development. Cloud software evaluating the reliability of the IBBC was developed in Python to achieve high execution speed resulting from using scientific and numerical libraries based primarily on optimized C-code. Finally, the experimental assessment was performed using laboratory prototypes of the studied converters to corroborate the theoretical predictions. The Power Electronics Research Laboratory of TalTech provides cutting-edge facilities for numerical simulations, hardware prototyping, and firmware development: laboratory DC power supplies, programmable DC electronic loads, solar array simulators, digital oscilloscopes, and corresponding probes with a wide bandwidth (>100 MHz), precision power analyzer, microprocessor development tools, PCB prototyping, soldering tools, and all other essential equipment.

#### 1.5 Contributions and Disseminations

The research results are presented through scientific publications, conferences, symposiums, doctoral schools, and presentations. During his Ph.D. studies, the author contributed to seven publications. Among them, four articles have been published in peer-reviewed journals of the IEEE. The conference papers were reported at international events after undergoing a peer-review process. This thesis is written based on seven scientific publications, including four journal and three conference papers.

#### Scientific novelties:

- Development, justification, and demonstration of the zero-redundancy fault tolerance concept in galvanically isolated DC-DC converters.

- The methodology for predicting the lifetime of the DC-DC converters, which is taking into account the influence of the application-specific mission profile on the random failure rate of components.

- The fault detection method for PV microconverters reusing the existing current and voltage sensors, which can provide fast, low-cost, and accurate localization of a faulty semiconductor device.

- Applications of the PV power curtailments technique to the fault-tolerant zero-redundancy DC-DC converters to maintain the same failure rate in post-fault conditions and methodology of its design.

#### Practical novelties:

- Experimental analysis of post-fault resistance of low-voltage Si and high-voltage SiC MOSFETs.

- Design of the PV microconverter with zero redundancy for residential applications with fault-tolerant capability.

- Demonstration of the lifetime underestimation for the PV microconverters resulting from using the MIL-HDBK-217F handbook.

- Recommendations for designing PV power curtailment algorithm for the case of post-fault operation of the FT zero-redundancy PV microconverter with 60-cell Si PV module.

- Measuring and providing an open-source yearly mission profile of solar irradiance and ambient temperature for Tallinn, Estonia.

#### 1.6 Experimental Setup and Equipment

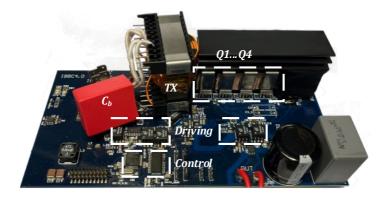

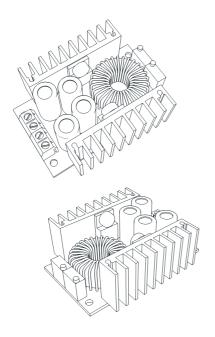

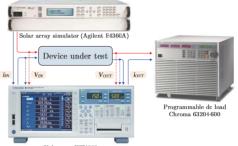

The experimental setup was assembled in the power electronics laboratory of Tallinn University of Technology. The tested prototype is shown in Figure 1.2. The waveforms of voltages and currents have been captured with the Tektronix MDO4034B-3 oscilloscope. Voltage and current waveforms were measured using differential voltage probes Tektronix P5205A and current probes TCP0030A, respectively. The firmware for STM32 microcontrollers was developed in the Keil µVision integrated development environment. Precision power analyzer Yokogawa WT1800 was employed to measure converter efficiency using the software application WTViewer for remote equipment access. The Agilent E4360 series modular solar array simulator was used as an input power

source for the experimental prototype while testing under the daily mission profiles. The Chroma 63205A-600-350 DC electronic load was employed to emulate the DC microgrid at the output of the IBBC.

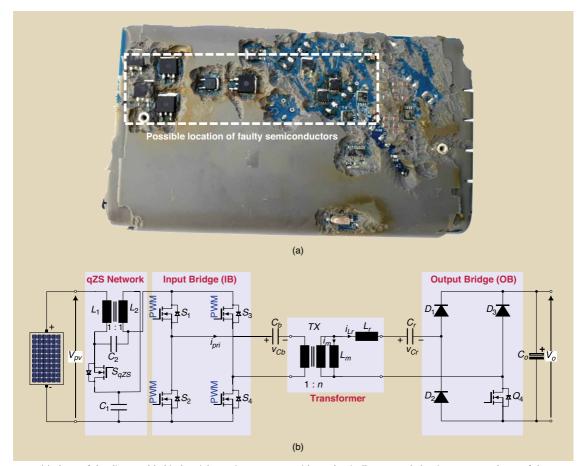

Figure 1.2 Prototype of the fault-tolerant PV microconverter.

#### 1.7 Recording of the Solar Mission Profile in Tallinn

The mission profile of solar irradiance and ambient temperature was recorded in Tallinn, Estonia, to share openly with the research community. The complete setup is installed on the rooftop of the NRG building, Tallinn University of Technology. A low-cost solution based on the Arduino platform is used as the main component for the data logger. The total installed system is shown in Figure 1.3. The DS1307 serial real-time lock is utilized to record real-time measurements. The solar irradiance is measured using three small PV cells connected in parallel to increase the total current. Following this, the short-circuit current is measured by the ACS70331 current sensor, which has a range of 2.5 A. A low-cost digital temperature sensor DS18B20 was used to measure the ambient temperatures with up to 12-bit resolution in centigrade. It can transfer readings to a microprocessor using a 1-Wire bus that only needs one data line for communication and two more for power supply and ground (GND) signals. It has an accuracy of ±0.5 °C when the temperature is between -10 °C and +85 °C. It has been installed in the shade outside the main box. The data are stored in an SD card using the SD card shield for Arduino [5].

Figure 1.3 Weather station recording solar irradiance and ambient temperature – installed on the roof of NRG building, Tallinn University of Technology, Tallinn, Estonia.

#### 1.8 Thesis Outline

The remaining part of the thesis starts with Chapter 2, which discusses the state-of-the-art isolated FT topologies based on the SRC. Following this, Chapter 3 explains the proposed isolated FT ZR-SRC and the fault detection issues. Chapter 4 introduces the proposed methodology for evaluating the IBBC reliability under a yearly PV mission profile based on the FIDES Guide. The modulation technique and the design guidelines are given in Chapter 5 based on the proposed methodology to diagnose and identify the IBBC fault on the input/output sides. Finally, Chapter 6 concludes the thesis and provides future work directions.

#### 2 Literature Review

#### 2.1 Introduction

It is typical for high step-up DC-DC applications to require galvanic isolation to step up the voltage efficiently. Therefore, several DC-DC converters have been proposed to address voltage variation [1],[6]. Various topologies provide different complexity, efficiency, implementation cost, and other aspects. Isolated buck-boost converters are suitable for wide-range applications requiring high voltage step-up. Usually, they have active switches on both sides of the converter to implement voltage buck and boost functionalities. Among these topologies, series resonant converters (SRCs) have demonstrated high performance in the target PV applications. The SRC topology provides soft-switching of semiconductor components, good isolation transformer utilization, and similarity to the LLC converter topology investigated in many industrial applications [7]. However, the ratio between the magnetizing and the resonant inductances is several times higher in the SRC than in the LLC converter.

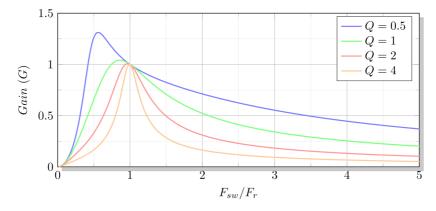

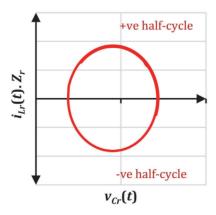

The resonant frequency  $(F_r)$  of the resonant converters can be given as in (2.1), where  $L_r$  is the resonant inductance, and  $C_r$  is the resonant capacitance. Resonant converters primarily depend on the quality factor (Q) that is affected by the parameters of the resonant tank and the load value (R) as in (2.2). The quality factor refers to the peak stored energy in the circuit to dissipate energy into the load.

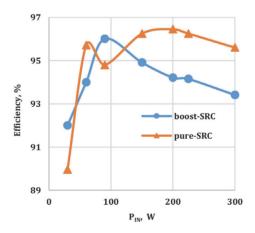

Figure 2.1 describes the relationship between the quality factor and the circuit parameters, where  $F_{SW}$  is the switching frequency. Notably, the DC voltage conversion gain of the converter can be controlled by changing the switching frequency, i.e., frequency modulation. However, this design results in low voltage regulation performance at light loads, making the design of magnetic components more challenging. Therefore, operating SRC at fixed switched efficiency is more efficient.

$$F_r = \frac{1}{2\pi\sqrt{L_r C_r}} \tag{2.1}$$

$$Q = \frac{1}{R} \sqrt{\frac{L_r}{C_r}} \tag{2.2}$$

Figure 2.1 Conversion gain of SRC with frequency modulation at different quality factor (Q) values.

#### 2.2 Classifications of SRC Fault-Tolerant Topologies

This subchapter discusses three possible implementations of fault-tolerant galvanically isolated full-bridge DC-DC converters and their pros and cons based on [PAPER-I]. The main concern of SRC failure is semiconductor failure. For these converters, the reported statistics show that primary semiconductors are the most vulnerable components [8].

Converter semiconductors generally have two possible fault states depending on the failure mechanism: open-circuit fault (OCF) and short-circuit fault (SCF). There are three main approaches to achieving fault tolerance in full-bridge galvanically isolated DC-DC converters for semiconductor faults, as summarised in Table 2.1. Using redundant components to overcome converter failure conditions is considered the most common and straightforward way to prevent power outages in mission-critical applications such as data centers and smart transformers [14], [15]. This allows the converter to extend its useful lifetime and increase its availability. The mentioned redundancy refers to the component level within a single converter. This requires additional hardware in the converter design, such as semiconductor or electromechanical switches, capacitors, bypass switches, and fuses, to isolate the defective component.

Table 2.1 Comparison between implementation approaches of the DC-DC FT-SRC.

| Item                                 | Redundant active leg [9]                                                   | Redundant capacitors leg [10],[11]                                         | Zero redundancy<br>[12], [13]                                                          |  |

|--------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| Example                              | Figure 2.2                                                                 | Figure 2.3                                                                 | Figure 2.4                                                                             |  |

| IB/OB<br>switch type                 | IGBT                                                                       | MOSFET/IGBT                                                                | MOSFET/IGBT                                                                            |  |

| Reported power range                 | > 350 W                                                                    | > 350 W                                                                    | < 350 W                                                                                |  |

| Post-fault overloading of components | No                                                                         | Yes                                                                        | Yes                                                                                    |  |

| Power curtailment                    | Not Needed                                                                 | Needed                                                                     | Needed                                                                                 |  |

| Additional components                | <ul><li>4 Aux. switches</li><li>4 Semiconductors</li><li>8 Fuses</li></ul> | <ul><li>4 Aux. switches</li><li>0 Semiconductors</li><li>0 Fuses</li></ul> | <ul><li> 0 Aux. switches</li><li> 0 Semiconductors</li><li> 0 Fuses</li></ul>          |  |

| Power density                        | XXX                                                                        | xx                                                                         | X                                                                                      |  |

| Cost                                 | \$\$\$                                                                     | \$\$                                                                       | \$                                                                                     |  |

| Reported applications                | <ul><li>Uninterruptable power supply</li><li>Data centers</li></ul>        | <ul><li>Uninterruptable power supply</li><li>Data centers</li></ul>        | <ul><li>Residential PV</li><li>Battery charger</li><li>Light-emitting diodes</li></ul> |  |

- X is the smallest, XXX is the largest

- \$ is the cheapest, \$\$\$ is the most expensive

#### 2.2.1 Topologies with Redundant Semiconductors

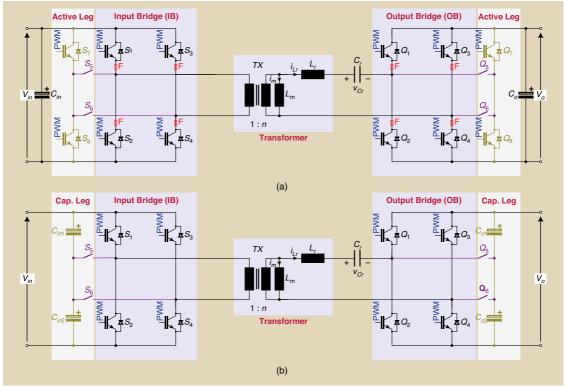

This FT implementation approach uses redundant switching legs (i.e., active legs) on the input and output sides. It requires a fuse in each semiconductor in the converter to convert the SCF to OCF after a thermal breakdown [9], as shown in Figure 2.2, in which  $V_{in}$  is the input voltage,  $V_{o}$  is the output voltage,  $i_{im}$  is the magnetizing current,  $i_{i,tr}$  is the resonant inductor current, and  $v_{Cr}$  is the resonant capacitor voltage. By doing this, the short-circuited faulty switch is isolated. To completely isolate the faulty leg, the healthy switch of the faulty leg should be turned off continuously. However, one of the drawbacks of using the fuses is that they consume power as they are connected in series during normal operation and thus affect the converter efficiency [8]. In addition, the presence of the fuse will increase parasitic inductance in the circuit [9].

Moreover, the auxiliary leg in such an FT converter implies additional costs for the auxiliary switches, gate drives, and auxiliary power supply. On the other hand, with this FT implementation approach, the converter component can handle the same power before and after the fault occurrence without overloading, as they are generally designed in the same way as the main inverter legs. This FT implementation approach typically utilizes IGBTs that can handle the short-circuit current long enough to burn the fuse. This ruggedness is unavailable with generic MOSFETs essential in low-power applications. An IGBT can easily withstand a short-circuit current for 10 µs, while some detection methods require less than one switching period to detect the fault [16].

Figure 2.2 A fault-tolerant isolated DC-DC converter using redundant semiconductor components on the input and output sides.

#### 2.2.2 Topologies with Redundant Capacitors

This FT implementation approach has two split capacitors with midpoints on the input and output sides, as shown in Figure 2.3 [10]-[11]. It requires four bypass switches to connect the faulty leg to these midpoints. Unlike the previous FT approach based on the active redundant leg, the IB/OB can be realized using IGBTs or MOSFETs, and the fuses are not required. The key to this FT approach is to keep the converter running after a failure but as a half-bridge SRC instead of a full-bridge SRC on the input side. In contrast, the output side will be reconfigured into a voltage doubler rectifier (VDR). The IB or OB should be reconfigured using the additional bypass switches to obtain an entire FT-SRC operation. In the case of an SCF, the damaged switch is used as a current conduction path, while another switch on the same leg is disconnected to prevent a short circuit across the power supply terminals. Since the power going to the load is the same before and after the fault, the converter on the opposite side will be over-stressed.

Figure 2.3 A fault-tolerant isolated DC-DC converter using redundant capacitors on the input and output sides.

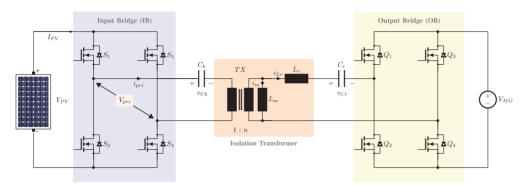

#### 2.2.3 Topologies with Zero Redundancy

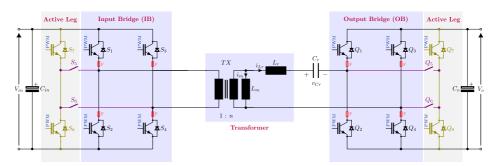

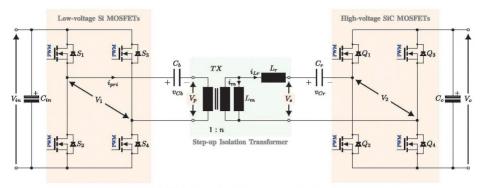

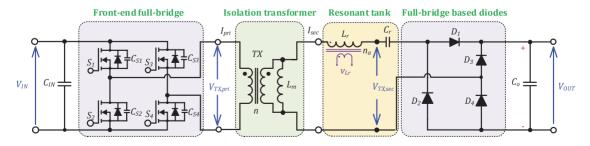

The fault-tolerant zero-redundancy SRC (FT ZR-SRC) is shown in Figure 2.4 [12], where  $V_1$  is the output voltage of the input inverter,  $V_2$  is the input voltage of the output rectifier,  $V_P$  is the primary winding voltage,  $V_S$  is the secondary winding voltage, and  $V_{Cb}$  is the voltage across the blocking capacitor  $C_b$ . This converter features buck and boost operation modes using special modulation techniques for its IB and OB, respectively. This concept is an alternative realization of the bidirectional SRC to ensure the post-fault operation in the case of SCF or OCF in any of its semiconductors. This topology has unique FT capabilities. The proposed FT implementation approach can be referred to as topology reconfiguration, which provides self-sufficiency without adding additional components to the circuit. This concept has been applied industrially in the photovoltaic (PV) microconverter named Optiverter [13]. The FT ZR converter can withstand a single fault (OCF or SCF) of its IB/OB semiconductors with up to two semiconductor faults without adding additional components. This is achieved by reconfiguring the faulty bridge as a half-bridge if the other bridge has an SCF.

Similarly to the FT implementation with redundant capacitors, the output voltage of the FT-SRC remains constant after a fault, and the RMS current of the transformer and the semiconductor becomes twice the RMS current in the normal state in the case of constant loading conditions. As a result, the thermal load on the converter components increases. In addition, this FT implementation approach does not require an additional fuse in series with each semiconductor to isolate the SC semiconductor, where the SC semiconductor is used as the current path. For any fault type in the IB (OCF/SCF), the OB must be reconfigured from the full-bridge rectifier to the Greinacher voltage doubler rectifier using different possible sequences [12]. The FT ZR implementation features thermal loading of components similar to the FT implementation with redundant capacitors but does not use any auxiliary switches.

Currently, this concept was implemented for an SRC-based DC transformer converter. At the same time, its application in IBBC based on quasi-Z-source topologies shows overall efficiency deterioration and possible thermal cycling issues, as described in [14].

Figure 2.4 A fault-tolerant isolated DC-DC converter with zero-redundant components on the input and output sides.

#### 2.3 Summary

The fault-tolerant implementation approaches have been discussed in the chapter to overcome semiconductor faults in galvanically isolated DC-DC converters based on SRC as the reference topology. Among them, the FT ZR SRC shows low implementation costs but requires power curtailment control if a fault occurs. It must be noted that there is a trade-off between adding additional components to the converter design and the associated increase in the converter size and initial cost needed to maintain the same converter performance before and after a fault. On the other hand, an FT ZR converter could suffer from overloading healthy remaining components after a fault occurs if no power curtailment algorithm is implemented. The FT implementation approach based on topology reconfiguration with zero redundancy is beneficial in cost-sensitive applications. The performance of the proposed FT ZR implementation provides the same post-fault stress of the components as the FT implementation with redundant capacitors. However, the reconfigurable FT ZR-SRC does not need auxiliary switches. Therefore, it can achieve a better cost-performance trade-off in FT converters.

This chapter shows the research gap in FT IBBCs with zero redundancy, which was solved in this work. In addition, it establishes the need for power curtailment control techniques and appropriate methodology for lifetime analysis of the galvanically isolated DC-DC converters.

### 3 Proposed Fault-Tolerant Zero-Redundancy Series Resonant Converter

#### 3.1 Topology Description

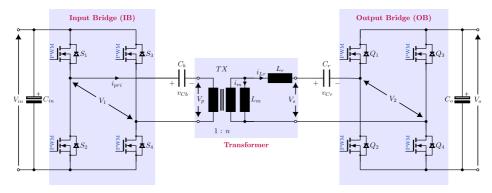

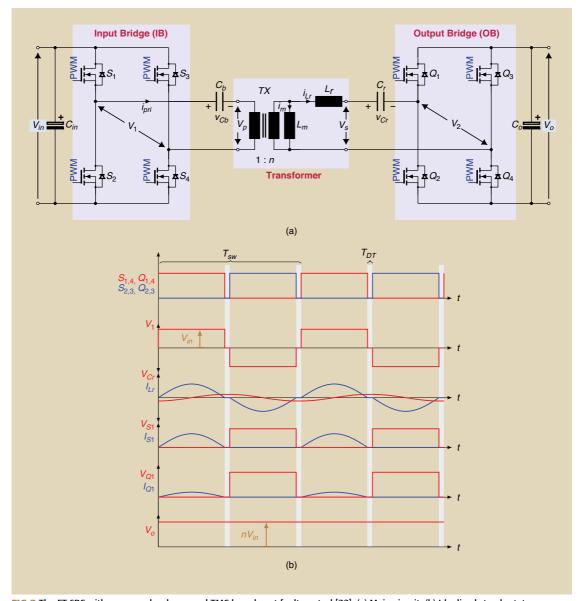

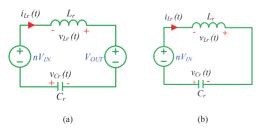

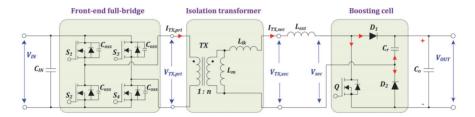

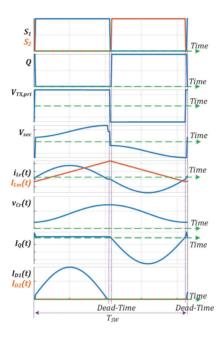

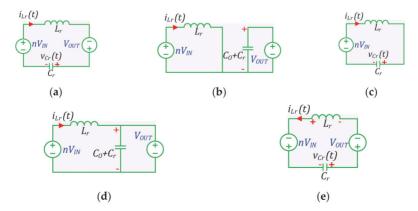

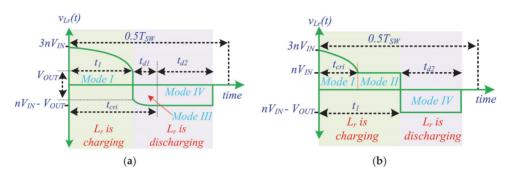

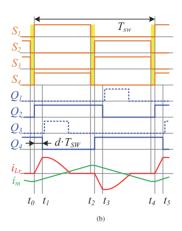

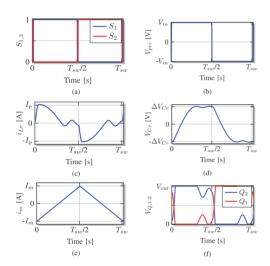

The basic structure of the proposed isolated buck-boost converter is provided in Figure 3.1(a). It contains only two hybrid switching bridges at the input and output and can be reconfigured from full- to half-bridge after a fault is detected. The blocking capacitor  $C_b$  contributes to avoiding the DC bias in the transformer current, which helps to avoid saturation of the transformer core after reconfiguration. In addition,  $C_b$  has a high capacitance value not to affect the IBBC resonant frequency. The idealized steady-state waveforms of the IBBC during the normal state are depicted in Figure 3.1(b), in which the IBBC is operating as a typically full-bridge SRC in the IB with a synchronous rectifier in the OB.

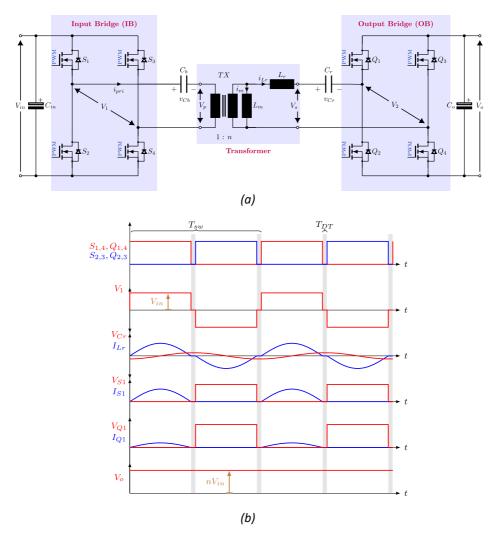

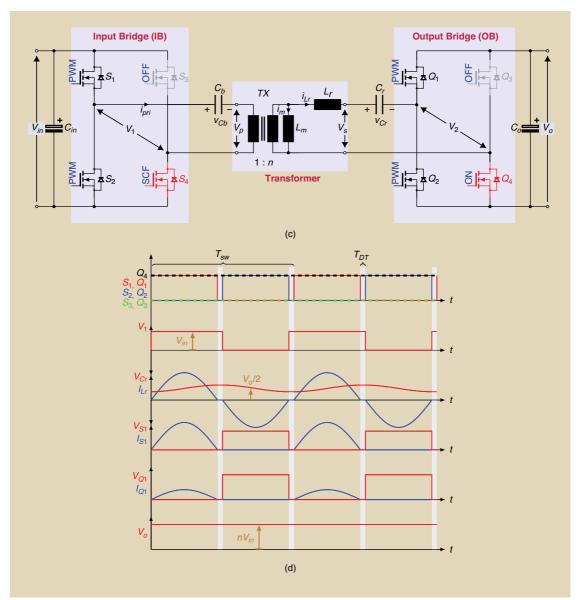

During the post-fault operation, for example, SCF at  $S_4$ , as shown in Figure 3.2(a), the average voltage across  $C_b$  and  $C_r$  equals half of the input and output voltages, respectively (see Figure 3.2(b)). Therefore, the total gain of the converter before and after the failure and consequent topology reconfiguration remains unchanged. It features direct power transfer into the load during most of the switching period. The primary side of the isolation transformer is coupled with an active full/half-bridge inverter. The semiconductors of the primary side bridge in the same leg are complementary and turned on with a short dead time in order to avoid a supply short-circuit. With this pulse width modulation (PWM) for the IB, the circulating current and conduction losses are minimized, and the primary side semiconductors are turned on with zero voltage switching (ZVS). With proper magnetic integration, the SRC utilizes the leakage inductance of the transformer, TX, as a part of the resonance tank to reduce the cost and size of the target converter.

One of the main drawbacks of SRC-based converters is the high voltage stress of the resonant capacitor in case of overloads, short-circuited output terminals, SCFs on the output side, or fast load transients. Depending on applications, this topology could be implemented with a slightly modified rectifier circuit that clamps the voltage of the resonant capacitor at the expense of somewhat higher losses, as was demonstrated in [PAPER-IV].

Figure 3.1 The FT ZR-SRC: primary circuit (a) and idealized steady-state waveforms during normal operation (b).

Figure 3.2 Post-fault operation of the FT ZR-SRC: an example of a possible reconfiguration after the fault in the MOSFET switch  $S_4$  (a) and idealized steady-state waveforms during post-fault operation (b).

#### 3.2 Modulation Techniques

As mentioned earlier, the studied FT ZR-SRC belongs to the IBBC family and can regulate the input voltage in a wide range. It operates at a fixed switching frequency and maintains its buck-boost voltage regulation functionality after a fault. This thesis considers it in low-power PV applications, where its compact design with a small (integrated) resonant inductor is beneficial. Although such an implementation results in low values of the quality factor of the resonant tank, the dc voltage gain can be controlled using pulse width modulation at a fixed switching frequency, simplifying the converter design.

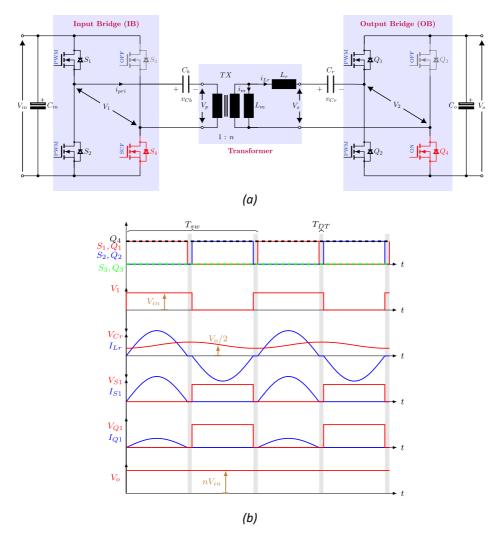

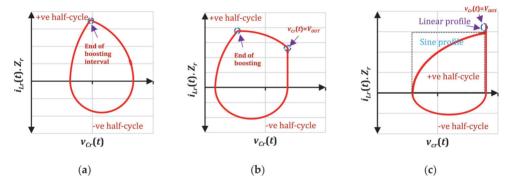

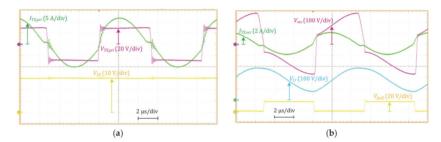

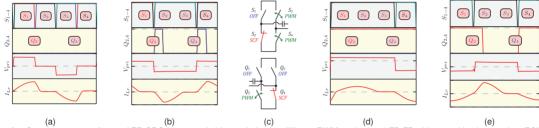

In the literature, there are different PWM techniques for the SRC operating with a low-quality factor at a fixed switching frequency, such as phase-shift modulation (PSM) [17], asymmetric PWM (APWM) [18], interleaved PWM [19], and forced half resonance (FHR) [20]. The steady-state waveforms of the FT ZR-SRC using these PWM techniques

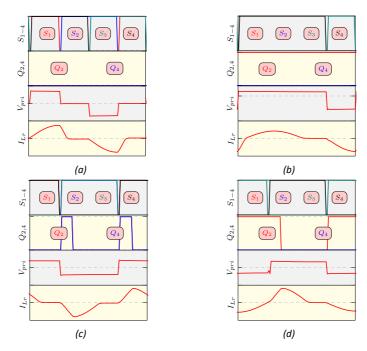

are depicted in Figure 3.3. The two former PWM techniques are used for buck operation when the PV voltage exceeds the nominal value by adjusting the phase shift between the two legs of the IB inverter. The PSM in Figure 3.3(a) is applied in the case of the full-bridge operation of the IB inverter. The APWM in Figure 3.3(b) is employed in the case of the half-bridge operation of the IB inverter.

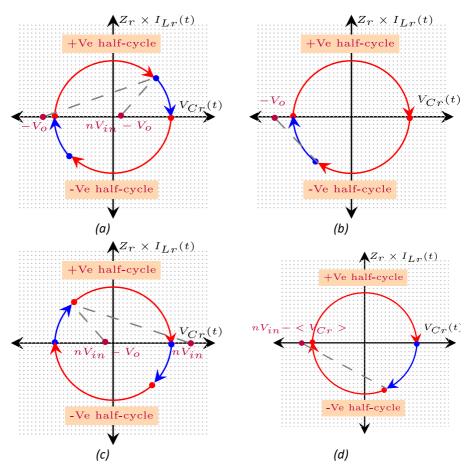

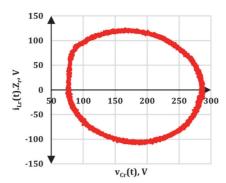

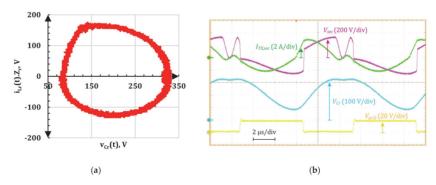

On the other hand, the OB transistors need to short-circuit the secondary winding to step up the voltage when the PV voltage is below the nominal value. Two PWM techniques are employed: interleaved modulation from Figure 3.3(c) to implement a full-bridge boost rectifier and forced half-resonance modulation from Figure 3.3(d) to implement a boost voltage doubler rectifier. After the resonant inductor is charged with additional energy from the input side, it releases this stored energy to the load. The corresponding state-plane trajectories of these four PWM techniques are shown in Figure 3.4, in which  $V_0$  is the converter output voltage, and  $Z_r$  is the resonant impedance.

Figure 3.3 Steady-state waveforms of ZR-SRC in normal operation for one switching period at different PWM methods: FB-FB with buck operation (PSM) (a), HB-HB with buck operation (APWM) (b), FB-FB with boost operation (Interleaved modulation) (c), and HB-HB with boost operation (Forced half-resonance) (d).

Figure 3.4 State-plane trajectory of the resonant tank variables at different PWM techniques: PSM (a), APWM (b), Interleaved PWM (c), and forced half-resonance PWM (d).

#### 3.3 Characteristics at Post-Fault Operation

As discussed in previous chapters, the FT ZR-SRC employs a faulty short-circuit switch as a current conducting path to reconfigure the faulty bridge from full-bridge to half-bridge operation. Consequently, laboratory tests were3 conducted to investigate the performance of the short-circuited faulty switches and the resulting converter efficiency. The test results are given in [PAPER-II].

This part investigates the distribution of the fault types in MOSFETs in the FT ZR-SRC. To this end, several defective MOSFETs are eventually soldered into actual prototypes operating at the fixed switching frequency close to 100 kHz. The selected batch considers Si MOSFETs for the IB and SiC MOSFETs for the OB. One phenomenon that has been observed is that surface-mounted Si devices maintain mechanical integrity after a fault. Contrary to this, SiC devices working at the high-voltage side could explode, destroying the case integrity and evaporating the semiconductor crystal inside, as demonstrated in Figure 3.5. An explosion of SiC devices results in OCF in all observed cases. On the other hand, the SiC MOSFETs maintain mechanical integrity without any visible damage in the case of an SCF.

Figure 3.5 Example of case damage to a SiC MOSFET featuring OCF.

The obtained results demonstrated that the SCF stands for 100% of the collected samples of low-voltage Si MOSFETs, and the main reason behind this could be the high current stress on the low-voltage side. Additionally, an 18/82% distribution between OCF and SCF was found for the high-voltage SiC MOSFETs in the OB of the ZR-SRC topology. This necessitates detecting and identifying both fault types in the OB but only SCFs in the IB of the proposed FT ZR-SRC converter.

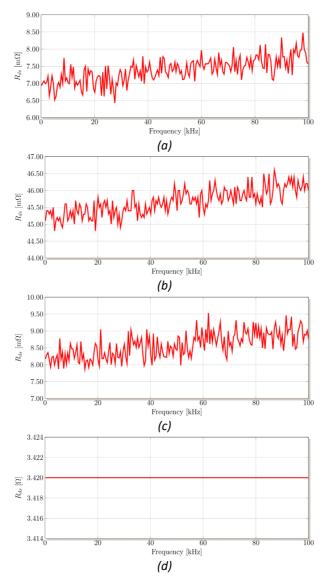

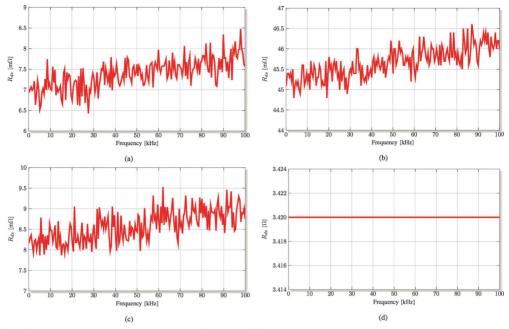

Short-circuited MOSFETs must be analyzed regarding impedance behavior to prove the feasibility of using a short-circuited MOSFET as a current conduction path after a fault. Different faulty MOSFETs were subjected to maximum current stress and fixed-switching operation for 40 hours, and their resistance remained unchanged. The post-SCF resistance of Si MOSFETs is usually below  $100~\text{m}\Omega$ . One of the tested samples with a post-fault resistance of  $7~\text{m}\Omega$  is shown in Figure 3.6(a) as a typical case. A few samples showed post-SCF resistance in the range of 30-90 m $\Omega$ . For example, the measurement results for one such device are shown in Figure 3.6(b). Hence, Si MOSFETs, the most fragile component in the converter according to the survey in [8], could be used as a conduction path with negligible resistance after an SCF.

A somewhat different situation was observed in the case of SiC MOSFETs featuring an SCF. Most cases show nearly ideal short-circuit with post-SCF resistance values of much below normal  $R_{ds,on}$  as shown in Figure 3.6(c). On the other hand, as exemplified in Figure 3.6(c), several cases show post-SCF resistances that are one order of magnitude higher than normal  $R_{ds,on}$ . This faulty switch with high post-SCF resistance was tested under load conditions for 30 hours at 2 A. Its resistance changed from 36.8  $\Omega$  to 41.20  $\Omega$ . The literature indicates that such a MOSFET would eventually converge to SCF or OCF.

Figure 3.6 Post-SCF drain-source resistance measurement results of four failed MOSFETs: low-resistance Si (a), high-resistance Si (b), low-resistance SiC (c), and high-resistance SiC (d).

#### 3.4 Fault Detection Issues

To address power converter failures, the fault must first be detected using an appropriate signature signal that adequately describes the converter's operation in every state. In addition, the fault location may need to be defined in order to decide whether to reconfigure the converter after the signature signal triggers the failure mode. The diagnosis signal, i.e., the signature signal, should provide enough information about the converter operation during both the normal and faulty state. When dealing with the fault in the converter, it comprises the fault diagnosis and the fault remedial, i.e., fault-tolerance, to ensure that the converter continues operation even in the faulty state. The fault diagnosis stage includes detecting that the converter enters an abnormal

condition, and sometimes it provides localization of the defective component in the converter. The primary purpose of the fault remedial is to make the converter operation continue despite the possibility of reduced performance.

Generally, diagnosis methods can be broken into signal and model-based methods [21]-[22]. With the model-based methods, the actual values of the converter diagnosis signals are measured and then compared with the observed values based on approximators. The most well-known approaches for estimation are the Kalman filter [23], extended Kalman filter [24], slide mode observer [25], and Luenberger observer [26]. The converter state, i.e., normal or faulty, can be identified based on the deviation between the measured and estimated values. On the other hand, the signal-based methods can be classified into time-domain and frequency-domain analysis of the diagnosis signal. The time-domain methods use a simple and low-cost analog implementation to compare the diagnosis signals with a threshold level [27]-[28]. The latter analysis depends on using Fourier Fast Transform (FFT) to extract the primary information from the diagnosis signal to define the converter status [29]-[30]. On the other hand, the frequency-domain analysis has the drawback of high computational effort and complexity.

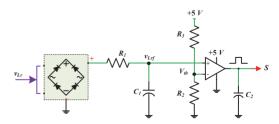

The voltage of the resonant inductor could be used as a signature signal for short-circuit detection, as proposed in [PAPER-III]. The method does not require expensive components as it can utilize a small tertiary winding for sensing this voltage. The high speed of detection achieved results from the operation of the resonant tank, which experiences much higher stress of components after a fault.

#### 3.5 Summary

This chapter addressed two hypotheses set forth in this thesis. First, the ZR FT IBBC was proposed based on the SRC topology. The proposed converter is capable of input voltage regulation in a wide range, both before and after a semiconductor fault. This concept creates new opportunities in cost-sensitive applications, where fault tolerance is typically avoided as it penalizes the implementation cost. Second, it was demonstrated that using a defective switch as a current conducting path in a reconfigurable FT DC-DC converter has proven feasible. This makes the ZR fault tolerance concept feasible and practical. As a result, it is possible to tolerate the failure of one of the DC-DC converter switches without affecting the overall operation of the converter. However, a converter of this type must be thermally engineered to withstand possible high ohmic losses in short-circuited MOSFETs. High ohmic losses can cause the converter to heat up and fail again if the thermal design does not consider this issue. As an alternative, its control system could include a power curtailment algorithm that limits the stresses on the remaining healthy components after a fault. This approach also diminishes the risk of overheating a short-circuited switch that serves as a current conductor in a reconfigured DC-DC converter.

### 4 Reliability-Oriented Design of the SRC-Based Fault-tolerant DC-DC converter with Zero Redundancy

#### 4.1 Converter Lifecycle and Reliability

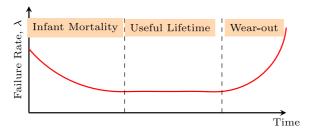

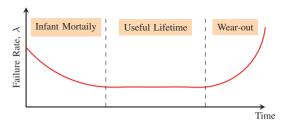

The most well-known definition of reliability from an engineering point of view is "the probability that an item will perform a required function without failure under the stated conditions for a stated period of time" [31]. To quantify the reliability, the component's hazard rate (i.e., failure rate)  $\lambda$  denotes the conditional likelihood that the component fails in a time interval. There are three main regions in the lifetime of electronic devices: early infant mortality failure, constant random failure, and wear-out failure, as shown in the classical life cycle bathtub curve in Figure 4.1 [32]. To prevent early life failures, burn-in or screening tests may be used.

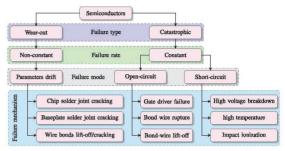

Random failures of components play a vital role in determining the probability of a system failure. The wearing out of components dominates over the probability of random failures as the service life increases, particularly at the late stages of useful life. Generally, power semiconductors fail in two ways: catastrophically with constant failure rates and wear out with variable failure rates over time. Both have different failure mechanisms, as shown in Figure 4.2. Since power electronic converters are typically long-lived in practice, they are assumed to operate in the useful lifetime range in many engineering applications [33]-[35]. Due to the lack of 100/120 Hz power ripple in the considered DC-coupled applications, the wear-out failures are ignored in this case study, and only random failures are considered [PAPER-VI], [33].

Figure 4.1 The typical lifecycle bathtub curve of an item.

Figure 4.2 The modes and mechanism of power device failures [34]-[35].

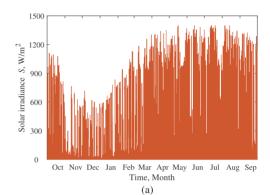

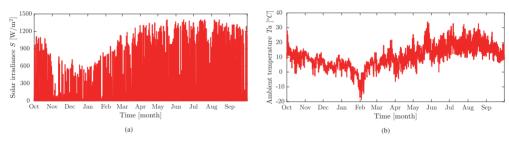

#### 4.2 Synthesis of High-Resolution Application-Specific Mission Profile

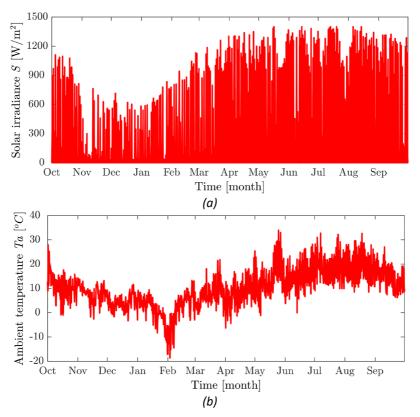

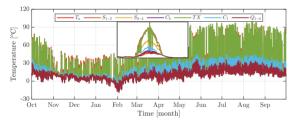

The reliability of installed photovoltaic systems has become a significant problem as the use of renewable energy in utility services has increased, causing concerns about possible power outages. The mission profile of incident solar irradiance and ambient temperature significantly affect solar PV output power. In addition, the mission profile of the operating conditions is required to analyze the PV system behavior for reliability prediction and system-level availability or to forecast the energy yield for a specific long-term horizon. The time step or resolution of the mission profile dataset depends on several elements, including the installation environment, the capacity of the dataset, and the implementation costs [PAPER-V]. Data loggers are required to capture the environmental data with appropriate precision to collect the mission profile at a high resolution, which could be costly [36]. In [37], it was examined how the resolution of the mission profile affected the reliability forecast and the lifetime consumption of PV inverter semiconductors. The findings of this study indicated that the low resolution of a mission profile could lead to an overestimation of the PV inverter lifetime. The mission profile resolution significantly impacts the prediction of the accumulated damage, particularly in cloudy environments. Figure 4.3 shows the yearly mission profile used in this study. It is captured for Northern Denmark (Aalborg) with a resolution of one second and a total of 31'863'123 records. The mean solar irradiance between November and February is low, impacting the temperature profiles of the IBBC components.

Figure 4.3 The yearly mission profile for Aalborg, Denmark, solar irradiation (a) and ambient temperature (b).

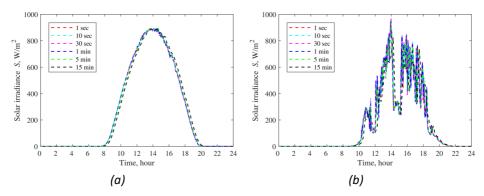

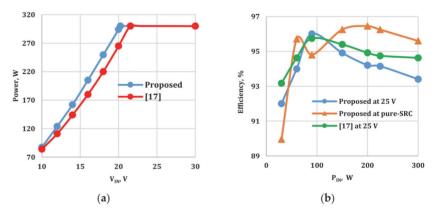

Figure 4.4 shows the solar irradiance for a clear and cloudy day at various resolutions of the mission profile. It is evident that the resolution of the solar irradiance profile has little impact on the clear-day mission profile when the solar irradiance has a minimal dynamic change. On the other hand, the dynamic change in solar irradiance deviates slightly from the mission profile resolution, particularly for a cloudy environment.

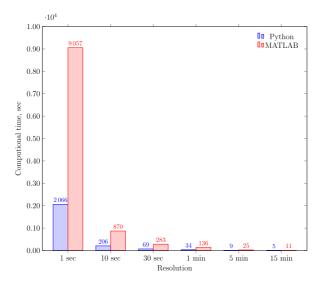

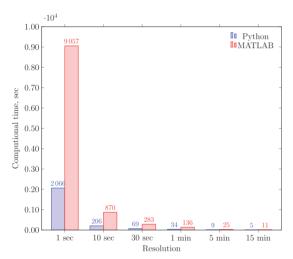

Figure 4.4 The daily solar irradiation at different mission profile resolutions, clear day (a) and cloudy day (b).

Table 4.1 provides the annual energy yield estimation results for a 60-cell Si PV module at different resolutions. The PV module's overall energy (kWh) is roughly the same for any resolution considered. Less than 0.5% separates the predicted energy yield values. The effectiveness of Python and MATLAB, the two popular software frameworks used to solve this kind of computational problem, were compared. For various mission profile resolutions, the computing time for both the Python and MATLAB scripts is displayed in Figure 4.5. The algorithm was executed on a personal computer with an Intel® Core™ i5-8265U CPU running and 16 GB of random access memory. The Python environment with C-based libraries offers an advantage in computation speed over MATLAB of between two and over four times. Therefore, the Python environment was used to implement the reliability estimation methods in this thesis to achieve an acceptable execution speed. The advantage of code development in Python becomes even more apparent for the analysis of more complicated converters, like the IBBCs, where a higher number of components should be modeled.

Table 4.1 Prediction of the annual energy yield at different mission profile resolutions.

| Resolution | 1 s   | 10 s  | 30 s  | 1 min | 5 min | 15 min |

|------------|-------|-------|-------|-------|-------|--------|

| E, kWh     | 314.0 | 314.5 | 314.5 | 314.6 | 314.8 | 315.1  |

Figure 4.5 Comparison between Python and MATLAB environments regarding execution speed of computational tasks employing high-resolution mission profile.

#### 4.3 Reliability Analysis Frameworks

#### 4.3.1 MIL-HDBK Reliability Handbook

Since the 1990s, the United States Navy has established the MIL-HDBK-217F Handbook, which is regarded as a standard for the reliability prediction of electronic systems [38]. It has been empirically verified that the models of the items inside it are accurate. With the MIL-HDBK-217F handbook, the random failure rate  $\lambda$  of the item can be expressed as a multiplicative form as

$$\lambda = \lambda_b(\prod_{i=1}^n \pi_i) \,, \tag{4.1}$$

where  $\lambda_b$  is the basic failure rate, and n denotes the number of  $\pi$ -factors of the item, which depends on the item's category. The unit of the resulted  $\lambda$  in this reliability approach is failures/(10<sup>6</sup> hours). The failure rates based on MIL-HDBK-217F associated with the MOSFETs ( $\lambda_{MOSFET}$ ) can be defined as in (4.2). For the isolation transformer, its failure rate ( $\lambda_{Transformer}$ ) can be given as in (4.3), while the failure rate of the capacitor ( $\lambda_{Capacitor}$ ) is calculated using (4.4), in which  $\pi_C$  denotes the capacitance stress factor and  $\pi_V$  denotes the voltage stress factor.

$$\lambda_{MOSFET} = \lambda_b \pi_T \pi_A \pi_O \pi_E , \qquad (4.2)$$

where  $\pi_T$  is the temperature stress,  $\pi_A$  is the application stress,  $\pi_Q$  denotes the quality factor, and  $\pi_E$  is environmental stress.

$$\lambda_{Transformer} = \lambda_b \pi_T \pi_O \pi_E \tag{4.3}$$

$$\lambda_{Capacitor} = \lambda_b \pi_T \pi_V \pi_C \pi_O \pi_E \tag{4.4}$$

#### 4.3.2 FIDES Reliability Guide

Eight French companies created the FIDES dependability manual guideline in its initial form in 2004 and revised it in 2009 [38][39]. The 2022 updated version is scheduled for publication in 2023. In the FIDES Guide, the component's random failure rate represented by the unit of FIT (i.e., failure per 10<sup>9</sup> hours) is predicted by considering the physics of failures. Here, the failure rate is expected to remain constant throughout the product's useful life, and the wear-out phase will not begin while the mission profile exists [39]. Since the component's useful lifetime is being modeled, it is not possible to assess the component's reliability during startup by using the FIDES Guide [40].

In contrast to the MIL-HDBK-217F reliability handbook, the FIDES reliability guide considers device technology, the impact of the extrinsic failure rate, and the sensitivity to quality parameters from design to usage. It employs the yearly mission profile for the item under consideration. Each mission profile can be subdivided into a series of phases, each with a time limit of hours [41]. With this reliability approach, the item failure rate can be expressed in the general form as

$$\lambda = \prod_{PM} \prod_{Process} \lambda_{Phy} \,, \tag{4.5}$$

where  $\Pi_{PM}$  is the technical and quality while manufacturing the item,  $\Pi_{Process}$  includes all the stages of the item processes starting from the setting of the specification to the operation in the field and maintenance, and  $\lambda_{Phy}$  is the physical failure rate related to the item that can be calculated using the mission profile. More details can be found in the paper [PAPER-VI].

#### 4.4 Analytical Results of Reliability Prediction

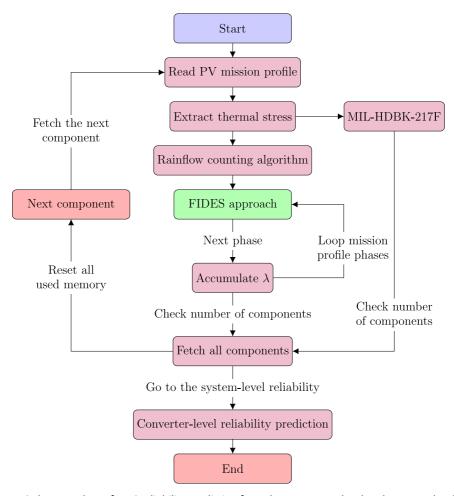

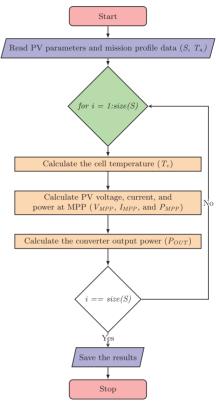

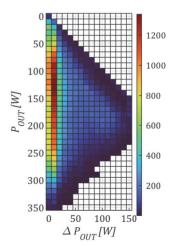

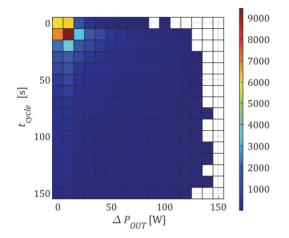

The prediction of n-th component reliability over the time t can be evaluated after determining its failure rate according to (4.6). The mean time to failure (MTTF), which indicates the time the component takes from the beginning to work until the first failure occurrence, can be computed using (4.7). The complete flowchart for the reliability evaluation of the studied IBBC FT ZR-SRC is shown in Figure 4.6. After reading the photovoltaic mission profile comprising the solar irradiance S and the ambient temperature  $T_a$ , the thermal stress of the IBBC components could be determined using the look-up table synthesized from the simulation of power losses in PLECS. The complete mathematical thermal analysis for each component of the SRC-based IBBC is detailed in Section III of [PAPER-VI]. The rainflow counting algorithm is used to manage the non-uniform thermal profile of the IBBC components and define the peak-to-peak thermal cycle, the mean temperature of the cycle, and the cycle duration [42]. In the current case study, the reliability block diagram is examined in a series connection, whereby if one component fails, the IBBC converter enters the faulty state. As a result, the IBBC failure rate can be expressed as in (4.8), where N = 11 denotes the number of IBBC key components considered. The reliability of the IBBC can therefore be determined by taking into account the product of the reliability of the system components as in (4.9).

$$R_n(t) = e^{\lambda_n t} \tag{4.6}$$

$$MTTF = 1/\lambda_n \tag{4.7}$$

$$\lambda_{IBBC} = \sum_{n=1}^{N} \lambda_n \tag{4.8}$$

$$R_{IBBC}(t) = \prod_{n=1}^{N} R_n(t) = e^{\lambda_{IBBC}t}$$

(4.9)

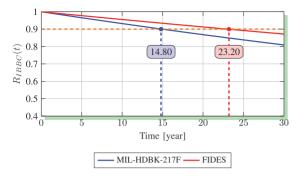

Figure 4.6 The procedure of IBBC reliability prediction from the component level to the system level.

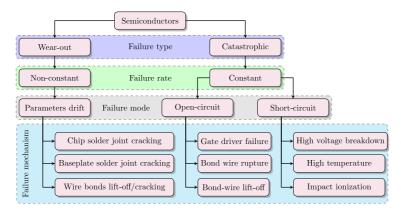

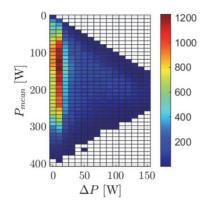

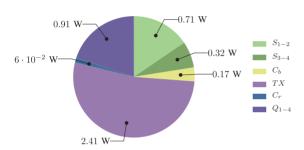

The failure rate from the two reliability analysis approaches for each IBBC component is shown in Figure 4.7(a). For MIL-HDBK-217F, it is clear that the  $S_{1-2}$  features the highest failure rate among the FT ZR-SRC components. On the other hand, the transformer has the highest failure rate for the FIDES Guide-based analysis due to the relatively high basic failure rate of 0.125 FIT defined in the FIDES Guide 2009. Therefore, the total failure rate of FT ZR-SRC expressed in failures per year equals 0.0071 and 0.0045 for MIL-HDBK-217F Handbook and FIDES Guide, respectively. Figure 4.7(b) illustrates the reliability prediction of the IBBC over time. The converter starts with 100% reliability, which degrades gradually over time with differing results for the 10% reliability reduction time (B<sub>10</sub>) of 14.80 and 23.20 years for the MIL-HDBK-217F Handbook and FIDES Guide, respectively. According to the results, the IBBC-based PV system is 83% and 89% reliable after 25 years of operation under the Aalborg mission profile when using MIL-HDBK-217F Handbook and FIDES Guide for analysis, respectively. This asserts that the MIL-HDBK-217F Handbook yields an overdesigned converter with a higher cost due to considering constant worse-case random failure rates.

Figure 4.7 Reliability analysis results for IBBC, the annual failure rate of components (a), and reliability prediction of the IBBC over time (b) [PAPER-VI].

#### 4.5 Summary

The main finding in this chapter is the reliability analysis methodology based on the FIDES Guide that considers the actual mission profile discovered in the field. This is important because it ensures that the mission profile is optimally executed, while it is not considered in the method described in the MIL-HDBK-217F Handbook. As a result, it could be concluded that the FIDES Guide, based on established empirical models for the PV converter based on the IBBC, offers a more accurate lifetime forecast and enables the application-tailored design of the DC-DC converter. The results support the fundamental hypothesis that the system random failure rate is primarily caused by the primary-side semiconductors, with the output-side switches having little bearing. The transformer is the least reliable passive component in the IBBC for PV applications because of the high basic failure rate introduced by the FIDES Guide, which cannot be diminished by control or transformer design. In contrast to the reliability analysis, the PV energy forecast does not need a high-resolution mission profile. Finally, the Python environment is regarded as the ideal choice for high-speed execution to examine the reliability of DC-DC converters when using a high-resolution mission profile.

The results obtained prove the third hypothesis of this thesis.

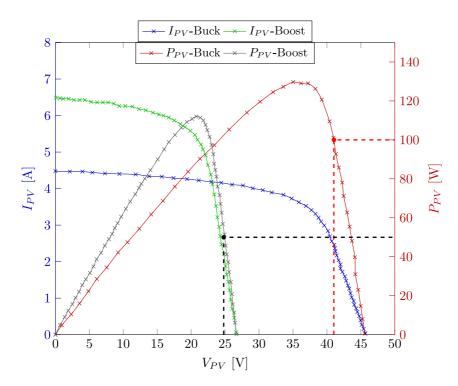

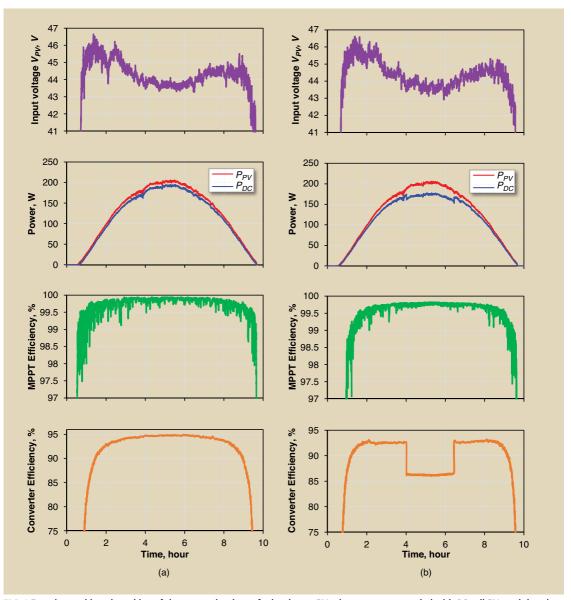

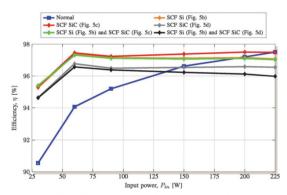

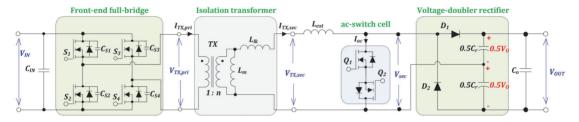

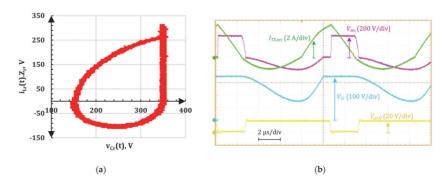

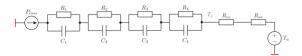

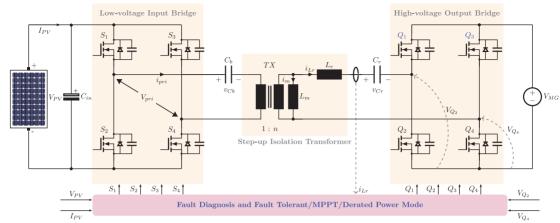

## 5 Self-Healing Fault-Tolerant PV Microconverter

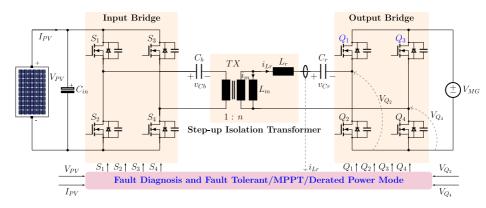

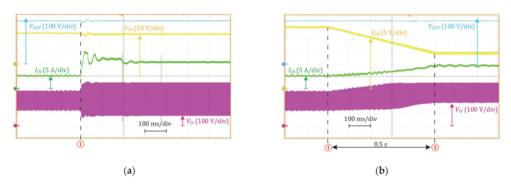

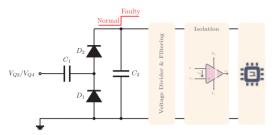

Self-healing FT ZR-SRC aimed at residential PV module-level applications was proposed in [PAPER-VII]. The complete configuration of the converter considering the fault diagnosis signals is shown in Figure 5.1. It employs a maximum power point tracking algorithm to ensure PV module performance at the maximum power point. The studied converter can achieve the global MPPT. Due to its simplicity, the perturb and observe (P&O) algorithm was utilized for MPPT near the global maximum. The FT ZR-SRC interfaces a residential PV module with a dc microgrid with high capacitance and stiff-voltage  $V_{MG}$ . In the normal operation of the converter, the body diodes of the top switches ( $Q_1$  and  $Q_3$ ) are used as rectifiers.

Moreover, these MOSFETs are used to restore converter operation in the case of an OCF or SCF in the bottom MOSFETs ( $Q_2$  or  $Q_4$ ). The synchronous rectification is not applied here to avoid degradation of the gate oxide layer in the top MOSFETs  $Q_1$  and  $Q_3$ , which strongly depends on the gate voltage stress. In addition, when the converter is operating in the normal state with boost mode, non-overlapping PWM is used to drive the bottom switches of the OB because it provides the best voltage regulation performance at the cost of a slightly lower efficiency [46]. The IBBC design guidelines are provided in this chapter, and the new fault diagnosis and detection methods are discussed.

Figure 5.1 Topology of the self-healing ZR-SRC for residential PV coupled with a stiff MG on the output side, considering the measurement signals for MPPT and fault diagnosis.

## 5.1 Design Guidelines for PV Applications

This subchapter explains how the design guildies for ZR-SRC described in [PAPER-VII] provide good buck-boost voltage regulation performance under all operating conditions. The main goal of the design guidelines is to produce self-healing converters possible with adequate efficiency while still meeting the cost and power requirements.

First, the transformer turns ratio (n) is selected so that the FT ZR-SRC can generate the desired output voltage of 350 V, which is the most common dc-bus voltage for the residential DC MGs (i.e.,  $V_{MG}$ ), at the nominal input voltage of 30 V ( $V_{IN,Nom}$ ) that is typical for 60-cell Si PV modules as in (5.1). This is the most probable operating point of the converter. The converter must provide the best performance at this point. To select the number of turns of the primary winding (that is to say, the low voltage side here), the maximum flux density of the core must be lower than 120 mT at the maximum input voltage according to (5.2), which ensures an acceptable level of losses in ferrite cores.

$$n = \frac{V_{MG}}{2V_{IN,Nom}},\tag{5.1}$$

$$\Delta B = \frac{V_{IN}}{2N_{p}A_{c}},\tag{5.2}$$

where  $\Delta B$  denotes the peak-to-peak flux density in the transformer core,  $N_p$  is the number of primary winding turns, and  $A_c$  is the cross-sectional area of the magnetic core.

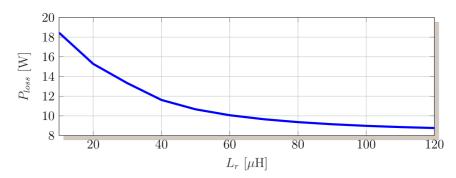

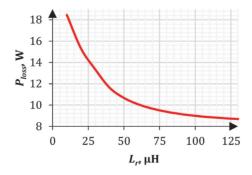

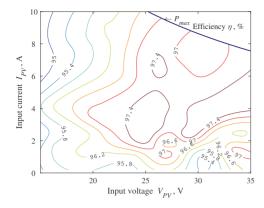

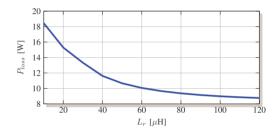

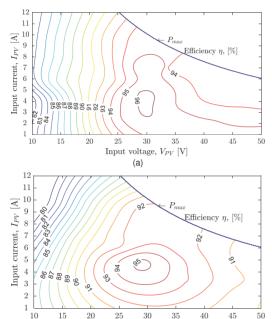

The resonant inductance of the SRC should be sufficiently large to minimize the converter losses and thus improve efficiency [43]. The relationship between the resonant inductance  $L_r$  and the ZR-SRC power losses must be considered when designing the resonant tank, as shown in Figure 5.2. Increasing the resonant inductance can reduce the converter losses. On the other hand, the ZR-SRC should operate in the discontinuous resonant current mode with a resonant tank quality factor of below one. Hence, the design of  $L_r$  is considered a trade-off that should be satisfactory (5.3). To account for losses and non-modeled dynamics in the converter, it might be recommended that  $L_r$  is selected in the range of 60-70% of the critical value in (5.3). The value of the resonant inductance in the current thesis is selected at 100  $\mu$ H.

$$L_r < \frac{2n^2 V_{IN,min} F_{SW}}{I_{IN,max} \omega_r^2}, \tag{5.3}$$

where  $V_{IN,min}$  is the minimum input voltage,  $I_{IN,max}$  is the maximum input current, and  $\omega_r$  is the resonant angular frequency.

Figure 5.2 The effect of the resonance inductance value on the total power loss of the FT ZR-SRC.

The peak value of the magnetizing current is achieved during the dead-time. It is reflected to the primary winding and recharges the parasitic output capacitance of the semiconductors in the IB. The magnetizing inductance  $L_m$  should be designed to allow the magnetizing current to fully charge and discharge the parasitic output capacitances ( $C_{oss}$ ) of the primary semiconductor during the dead-time ( $T_{DT}$ ) in the gating signals of the primary switches [PAPER-IV], as

$$L_m \le \frac{n^2 T_{DT}}{8F_{SW}C_{ASS}}. (5.4)$$

The resonant inductance can be implemented as a discrete inductor or integrated into the isolation transformer. The use of the magnetic integration concept has the merit of reducing the converter size and the cost, but on the other hand, the design becomes a challenging task. An isolation transformer with integrated magnetic elements was implemented in this work Using the guidelines given in [44].

The parameters of the resonant tank determine the resonance frequency. To obtain the best conversion efficiency of the converter, it is essential to design the FT ZR-SRC to operate close to the resonant frequency. The resonant capacitor  $C_r$  can be directly defined using the specified value of  $L_r$  and the resonant frequency  $F_r$  using (2.1). According to the circuit configuration, the average voltage of the resonant capacitor equals zero in the full-bridge rectifier for normal operation. It has a dc bias in the half-bridge rectifier configuration for the post-fault operation. The peak-to-peak ripple across  $C_r$  ( $\Delta V_{Cr}$ ) is only affected by the output power of the converter  $P_{\text{out}}$  and the input voltage equal to the voltage of the PV module  $V_{\text{PV}}$ , as

$$\Delta V_{Cr} = \frac{P_{out}T_{SW}}{2nV_{PV}C_r},\tag{5.5}$$

where  $T_{sw}$  is the switching period.

For the semiconductors of the FT ZR-SRC, the maximum voltage stress of the MOSFETs in the IB equals the maximum open-circuit voltage of the PV module. In contrast, the voltage stress of the OB MOSFETs equals the maximum DC microgrid voltage. Considering expectations of low implementation cost for residential PV converters, the current stress of the IB/OB MOSFETs is designed for normal operation, as provided in [45].

## 5.2 Fault Diagnosis and Detection Methods

Irrespective of the failure mechanism that leads to a catastrophic failure, the failure mode of the semiconductors (Si MOSFETs in the IB and SiC MOSFETs in the OB) is considered as either OCF or SCF. Generally, resonant topologies are more promising DC-DC converters for the industry. They are widely adopted in many industrial applications, such as data centers and battery chargers, due to their soft switching and high-efficiency features [46]. A recent survey regarding the failure of these converters [8] was conducted among scientists working in the industrial sector and academic positions related to applied power electronics. This provides some variety in the replies collected worldwide and thus increases the accuracy of survey results. Around 72% of the participating companies have more than ten years of market experience. The summary of this detailed survey indicates that the primary semiconductors of the SRC/LLC converters are regarded as the primary source of converter failure. It contributes approximately half (i.e., 47.6%) of the damage source of the converter. Moreover, the survey shows that primary semiconductors fail in the form of SCFs, according to the participant's experience.

Furthermore, several tens of random samples of low-voltage switches that failed while testing high step-up DC-DC converters were collected [PAPER-II]. The quantitative results prove that the SCF fits 100% of the collected dataset. Thus, the resulting statistical analysis of the collected dataset is consistent with the statistical results collected for the SRCs in industrial applications [8]. Hence, in line with the previous discussion, this study only considers the SCF of the primary semiconductors during fault diagnosis and detection. OCF and SCF are considered for the OB rectifier to provide a comprehensive fault study on the FT ZR-SRC topology.

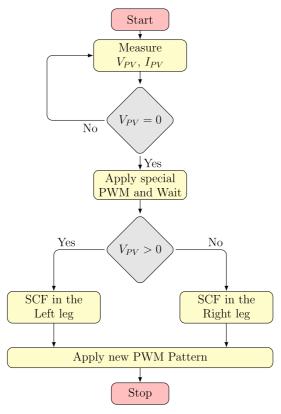

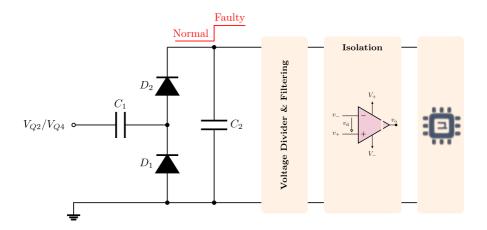

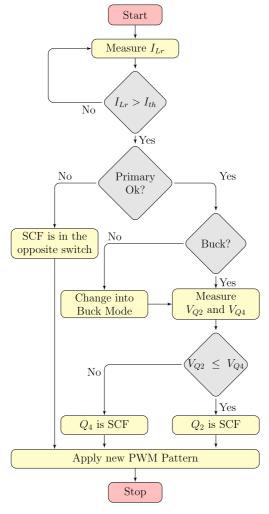

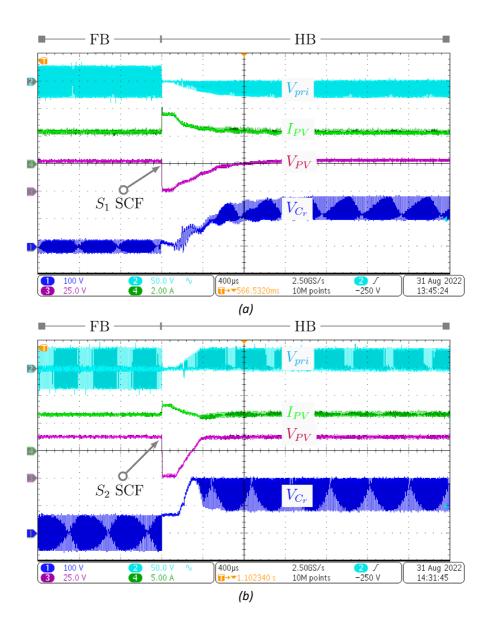

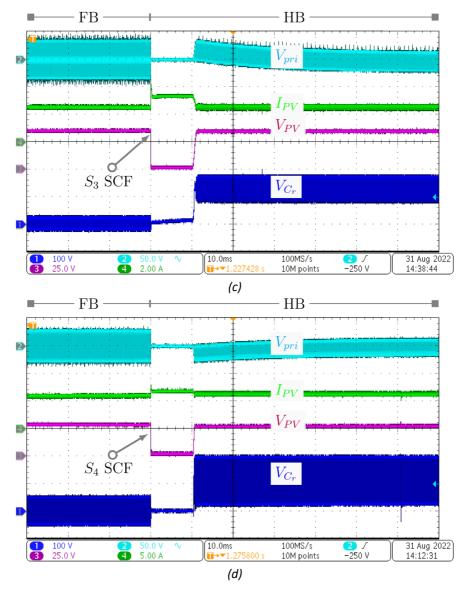

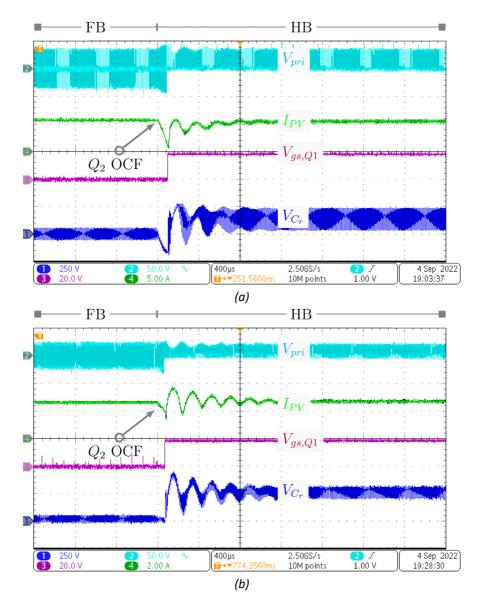

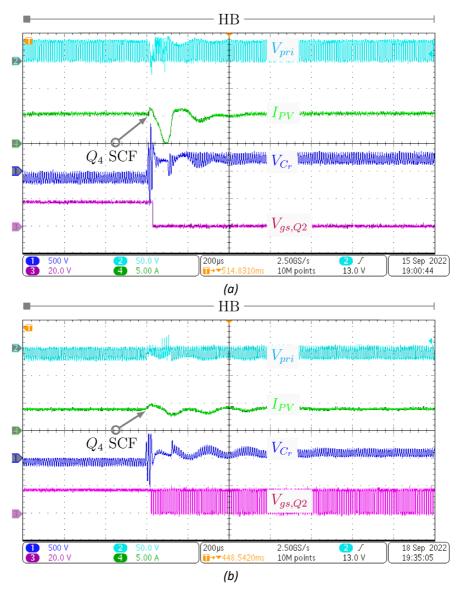

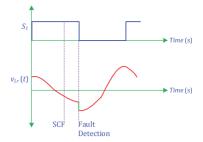

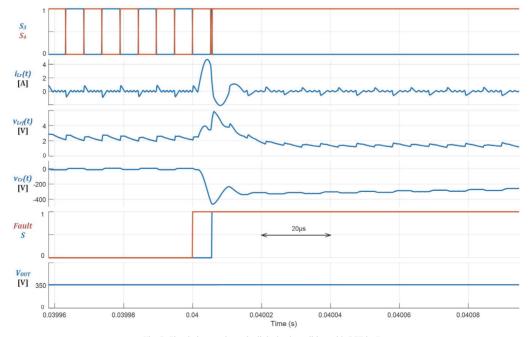

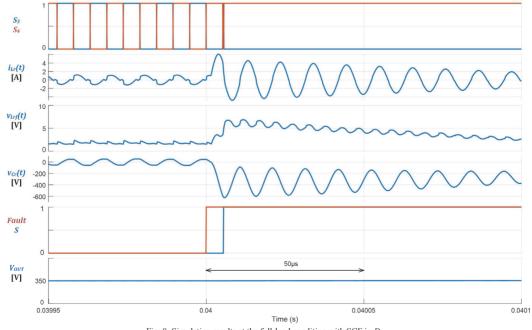

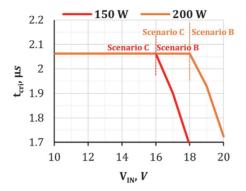

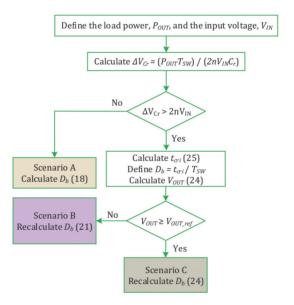

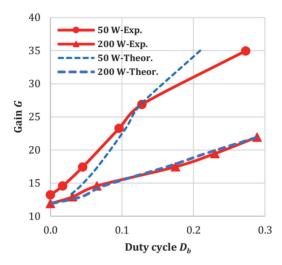

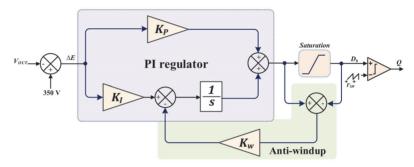

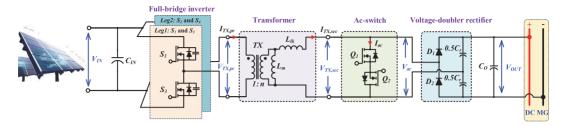

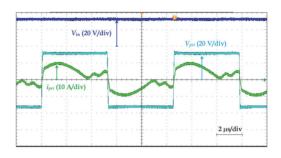

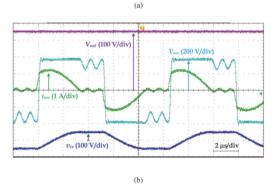

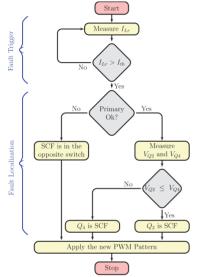

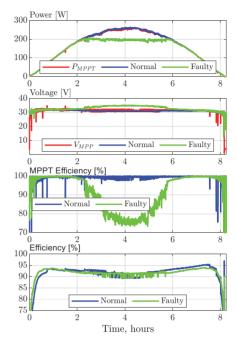

## **5.2.1 SCF of the Primary-Side MOSFETs**