THESIS ON INFORMATICS AND SYSTEM ENGINEERING C46

# **Fault Simulation of Digital Systems**

SERGEI DEVADZE

## TALLINN UNIVERSITY OF TECHNOLOGY Faculty of Information Technology Department of Computer Engineering

Dissertation was accepted for the defence of the degree of Doctor of Philosophy in Computer and Systems Engineering on July 27, 2009.

Supervisors: Prof. Raimund Ubar, D.Sc. Prof. Peeter Ellervee, Ph.D.

Opponents: Prof. Heinrich Theodor Vierhaus, Brandenburg University of Technology Cottbus, Germany

> Prof. José Manuel Martins Ferreira, University of Porto, Portugal

Defence: August 24, 2009

Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted for any academic degree.

/Sergei Devadze/

Copyright: Sergei Devadze, 2009 ISSN 1406-4731 ISBN 978-9985-59-928-0 INFORMAATIKA JA SÜSTEEMITEHNIKA C46

## Digitaalsüsteemide rikete simuleerimine

SERGEI DEVADZE

To my family

## Abstract

The current thesis addresses issues in the field of digital testing. The presented work is focused on improving the efficiency of fault simulation methods that are widely used in the flow of designing tests for digital devices. Although the primary goal of fault simulation is assessment of quality of prepared test program, many test-related problems are strongly dependent on fault analysis. The tasks of test generation, fault diagnosis, optimization of built-in self test and test set compaction incorporate fault simulation as a part of process. Therefore the efficiency of fault analysis algorithm is an essential condition for solving the abovementioned tasks.

The main contribution of the research is the improvement of stuck-at fault simulation. The thesis presents several approaches for conducting fault analysis of a circuit represented by a special class of binary decision diagrams. The simulation is performed on macro-level but with gate-level accuracy. In particular, novel single-pattern and parallel-pattern simulation algorithms are introduced. Finally, the application of fault simulation for the hierarchical analysis of dependability is studied. The performed experiments confirm that the efficiency of the proposed methods overcomes the state-of-the-art approaches.

The thesis is based on the selected scientific papers published in journal and the proceedings of several international conferences.

## Kokkuvõte

Antud väitekirja teematika on seotud digitaalsüsteemide projekteerimisega ja testimisega. Doktoritöö peaeesmärgiks on rikete simuleerimise meetodite parandamine.

Rikete simuleerimine ehk rikete analüüs on üks tähtsamaid ülesandeid digitaaltestimise valdkonnas, mille eesmärgiks on kindlaks teha, milliseid rikkeid on võimalik avastada etteantud testide abil. Kuna rikete analüüs kujutab endast sisuliselt protsessi, mis on aluseks paljude teiste testimisprobleemide lahendamisel (nt. testide kvaliteedi analüüsil, rikete diagnoosil, testide genereerimisel ja tihendamisel, süsteemide testkõlblikkuse hindamisel, isetestivate arhitektuuride projekteerimisel jne.), siis simulatsiooni kiirus on muutunud otsustavaks faktoriks loetletud ülesannete lahendamise ehk testide projekteerimise efektiivsuse tõstmisel.

Käesoleva doktoritöö tulemusena on välja töötatud efektiivsed meetodid ja algoritmid konstantrikete simuleerimiseks digitaalseadmetes. Erinevalt teistest meetoditest töötavad väljaarendatud simulaatorid kõrgemal abstraktsel tasandil kui loogikalülituste tase (tagades samal ajal loogikalülituste taseme täpsuse) ning kasutavad originaalset struktuurselt sünteesitud otsustusdiagrammide (OD) teooriat skeemide analüüsil.

Töö põhitulemused võib formuleerida järgmiselt. Esiteks on loodud OD teoorial põhinev deduktiivne algoritm rikete levimise analüüsiks skeemis ning selle algoritmi alusel ka vastav rikete simulaator. Teiseks on loodud uus ülikiire simulatsioonimeetod, mis võimaldab analüüsida rikkeid terve grupi testvektorite jaoks paralleelselt. Nimetatud meetodi uudsus seisneb erilise hargnemisanalüüsi meetodi väljatöötamises ning optimeeritud arvutusmudeli koostamises Boole'i diferentsiaalvõrrandite paralleelseks lahendamiseks. Eksperimendid näitasid, et võrreldes olemasolevate professionaalsete rikkesimulaatoritega, tõstab uus meetod tunduvalt rikete analüüsi kiirust. Rikete simulaatori rakendusena on väitekirjas välja töötatud originaalne hierarhiline meetod veakindluse hindamiseks, mis on üheks tsentraalseks ülesandeks usaldatavate süsteemide projekteerimisel.

Väitekirja aluseks on võetud neli teadusartiklit, mis on publitseeritud ühes ajakirjas ja kolme rahvusvahelise tippkonverentsi kogumikus.

## Acknowledgements

I would like to thank everybody who helped me with advice and support during my Ph.D. studies.

First of all, I would like to sincerely thank my supervisor Prof. Raimund Ubar for guiding and consulting me through my studies and also encouraging me to finish this thesis. I am thankful to my other advisors, especially to Dr. Aleksander Sudnitson for helping me to make the first steps in my research activity and also Dr. Peeter Ellervee for giving valuable comments and remarks about this thesis.

Special thanks to Dr. Margus Kruus, the head of department of Computer Engineering for creating outstanding environment for productive work and study.

Furthermore, I want to thank Dr. Artur Jutman for his countless advises and interesting discussions. Also I would express my appreciation to my other colleagues, in particular Dr. Maksim Jenihhin, Dr. Jaan Raik and Uljana Reinsalu. The same holds for the group of young researches from the room IT231, Anton Tsertov, Igor Aleksejev, Sergei Kostin and Anton Tsepurov.

I am grateful to Dr. Dieter Wuttke from Technical University of Ilmenau for his hospitality and organizing fruitful summer projects that helped to seamlessly combine great vacation time with the fascinating work.

Moreover, I would like to acknowledge the organizations that have supported my Ph.D. studies: Tallinn University of Technology, Enterprise Estonia (project ELIKO), EU Regional Development Fund (project CEBE), National Graduate School in Information and Communication Technologies (IKTDK) and Estonian IT Foundation (EITSA).

Finally, I'd like to express my gratitude to my family and especially to my parents who were motivating and supporting me in all my undertakings. I am also indebted to my beloved wife Alla for her care and support throughout the time of my work and studies.

## **List of Publications**

#### Fault simulation and fault analysis

- S. Devadze, R. Ubar, J. Raik, A. Jutman, "Parallel Exact Critical Path Tracing Fault Simulation with Reduced Memory Requirements", *Proc. of* 4th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era, Cairo, Egypt, 2009.

- R. Ubar, S. Devadze, J. Raik, A. Jutman, "Parallel Fault Backtracing for Calculation of Fault Coverage", *Proc. of 13th Asia and South Pacific Design Automation Conference (ASPDAC'08)*, Seoul, Korea, 2008, pp. 667-672.

- R. Ubar, S. Devadze, M. Jenihhin, J. Raik, G. Jervan, P. Ellervee, "Hierarchical Calculation of Malicious Faults for Evaluating the Fault Tolerance", *Proc. of 4<sup>th</sup> IEEE International Symposium on Electronic Design, Test & Applications (DELTA'08)*, Hong Kong, China, 2008, pp. 222-227.

- R. Ubar, S. Devadze, J. Raik, A. Jutman, "Parallel Fault Backtracing for Calculation of Fault Coverage", Proc. of 43<sup>rd</sup> International Conference on Microelectronics, Devices and Materials and the Workshop on Electronic Testing (MIDEM'07), Bled, Slovenia, September 12-14, 2007, pp. 165-170.

- R. Ubar, S. Devadze, J. Raik, A. Jutman, "Ultra Fast Parallel Fault Analysis on Structurally Synthesized BDDs", *Proc. of 12<sup>th</sup> IEEE European Test Symposium (ETS'2007)*, Freiburg, Germany, May 20-24, 2007, pp. 131-136.

- S. Devadze, R. Ubar, "Parallel Fault Analysis on Structurally Synthesized BDDs", *Proc. of 2<sup>nd</sup> IKTDK Conference*, Viinistu, Estonia, 2007, pp. 47-50.

- S. Devadze, J. Raik, A. Jutman, R. Ubar, "Fault Simulation with Parallel Critical Path Tracing for Combinational Circuits Using Structurally Synthesized BDDs", *Proc. of 7<sup>th</sup> IEEE Latin-American Test Workshop* (*LATW'2006*), Buenos Aires, Argentina, 2006, pp.97-102.

- S. Devadze, "Efficient Fault Simulation Method on Structurally Synthesized BDDs", *Proc. of 1<sup>st</sup> IKTDK Conference*, Estonia, 2006, pp. 123-126.

- J. Raik, R.Ubar, S.Devadze and A.Jutman, "Efficient Single-Pattern Fault Simulation on Structurally Synthesized BDDs", *Proc. of 5<sup>th</sup> European Dependable Computing Conference (EDCC'2005)*, Budapest, Hungary, 2005, pp.332-344.

#### Board and system level test optimization

- S. Devadze, A.Jutman, I. Aleksejev, R. Ubar, "Fast Extended Test Access via JTAG and FPGAs", accepted for publishing in Proc. of 40<sup>th</sup> International Test Conference (ITC'2009).

- S. Devadze, A. Jutman, I. Aleksejev, R. Ubar, "Turning JTAG Inside Out for Fast Extended Test Access", *Proc. of 10<sup>th</sup> Latin-American Test Workshop (LATW'2009)*, Rio de Janeiro, Brazil, 2009.

- S. Devadze, A. Jutman, A. Tsertov, M. Istenberg, R. Ubar, "Microprocessor-based System Test using Debug Interface", Proc. of 26<sup>th</sup> IEEE Norchip Conference (NORCHIP'2008), Estonia, 2008.

- A. Jutman, V. Rosin, S. Devadze, R. Ubar, "Trainer 1149.1: A Boundary-Scan Simulator", 5th IEEE International Board Test Workshop (BTW'2006), Fort Collins, Colorado, Sept 13-15, 2006.

#### *Finite State Machine decomposition*

- S. Devadze, A. Sudnitson, "Software Environment for Synthesis of Testable FSM through Decomposition", *Proc. of 26<sup>th</sup> International Conference on Microelectronics (MIEL'08)*, Nis, Serbia, 11-14 May 2008, vol. 2, pp. 433-436.

- S. Devadze, A. Sudnitson, "Synthesis of Testable FSM through Decomposition", *Proc. of 3<sup>rd</sup> IKTDK Conference*, Voore, Estonia, 2008, pp. 101-104.

- A. Sudnitson, S. Devadze, "Web-Based Computer Aided Design Support of Finite State Machine Additive Decomposition for Low Power", *Proc. of* 5<sup>th</sup> IEEE East-West Design & Test International Symposium (EWDTS'07), Yerevan, Armenia, 2007, pp. 494-498.

- A. Sudnitson, S. Devadze, "Computer Aided Design Support of FSM Multiplicative Decomposition" *Proc. of IEEE East-West Design&Test International Workshop (EWDTW'06)*, Sochi, Russia. 2006, pp. 241-246.

- S. Devadze, A. Sudnitson, "FSM Decomposition Software for Education and Research", *Proc. of IEEE EUROCON 2005 International Conference* on 'Computer as a Tool', Belgrade, Serbia and Montenegro, 2005, pp. 839-842.

- S. Devadze, "Web-Based System for Finite State Machines Decomposition", M.Sc. thesis, Tallinn University of Technology, 2004.

S. Devadze, E. Fomina, M. Kruus, A. Sudnitson, "Web-Based System for Sequential Machines Decomposition", *Proc. of IEEE EUROCON 2003 International Conference on 'Computer as a Tool'*, Slovenia, 2003, vol. 1, pp. 57-61.

#### HW-SW co-design

U. Reinsalu, S. Devadze, A. Jutman, A. Chertov, P. Ellervee, "Hardware/Software co-design in practice: MEMOCODE'08 contents experience", *Proc. of 3<sup>rd</sup> IKTDK Conference*, Voore, Estonia, 2008, pp. 55-58.

#### Laboratory environment for education and research of design and test

- R. Ubar, A. Jutman, S. Devadze, H.-D. Wuttke, "Bringing Research Issues into Lab Scenarios on the Example of SOC Testing", *ICEE Proceedings*, University of Coimbra, Portugal, 2007.

- R. Ubar, A. Jutman, M. Kruus, E. Orasson, S. Devadze, H.-D. Wuttke, "Learning Digital Test and Diagnostics via Internet", *International Journal* of Online Engineering, 3(1), 2007, pp. 1–9.

- W. Pleskacz, A. Jutman, R, Ubar, S. Devadze, "DefSim the defective IC", *In University Booth section of Design Automation and Test in Europe (DATE 2007)*, France, 2007.

- R. Ubar, A. Jutman, M. Kruus, E. Orasson, S. Devadze, H.-D. Wuttke, "Learning Digital Test and Diagnostics via Internet", *International Journal* of Computing and Information Sciences, 7(4), 2006.

- S.Devadze, "Web-Based Training System for Teaching Digital Design and Test", Proc. of 7<sup>th</sup> International Student Conference on Electrical Engineering (POSTER2003), Prague, Czech Republic, May, 2003.

- S.Devadze, R.Gorjachev, A.Jutman, E.Orasson, V.Rosin, R.Ubar, "E-Learning Tools for Digital Test", *Proc. of 3<sup>rd</sup> International Conference* '*Distance learning – educational sphere of XXI century*', Minsk, Republic of Belarus, 2003, pp. 336-342.

- S. Devadze, A. Jutman, A. Sudnitson, R. Ubar, and H.-D. Wuttke, "Teaching Digital RT-Level Self-Test Using a Java Applet", *Proc. of 20<sup>th</sup> IEEE NORCHIP Conference 2002*, Denmark, 2002, pp. 322-328.

- S. Devadze, A. Jutman, A. Sudnitson, R. Ubar, and H.-D. Wuttke, "Java Technology Based Training System for Teaching Digital Design and Test", *Proc. of 8<sup>th</sup> Biennial International Baltic Electronics Conference* (*BEC*'2002), Tallinn, Estonia, 2002, pp. 283-286.

- S. Devadze, A. Jutman, M. Kruus, A. Sudnitson, and R. Ubar, "Web Based Tools for Synthesis and Testing of Digital Devices", *Proc. of International Conference on Computer Systems and Technologies (CompSys'2002)*, Sofia, Bulgaria, 2002, vol.1, pp. 91-96.

- S. Devadze, A. Jutman, A. Sudnitson, and R. Ubar, "Web-Based Training System for Teaching Basics of RT-level Digital Design, Test, and Design for Test", *Proc. of 9<sup>th</sup> International Conference Mixed Design of Integrated Circuits and Systems (MIXDES'2002)*, Wroclav, Poland, 2002, pp.699-704.

- S. Devadze, M. Kruus, and A. Sudnitson, "Web-Based Software Implementation of Finite State Machine Decomposition for Design and Education", *Proc. of International Conference on Computer Systems and Technologies (CompSys'2001)*, Bulgaria, 2001, vol.4, pp. 1-7.

# **List of Abbreviations**

| ASIC  | Application Specific Integrated Circuit   |

|-------|-------------------------------------------|

| ATPG  | Automatic Test Pattern Generation         |

| BDD   | Binary Decision Diagram                   |

| BIST  | Built-In Self Test                        |

| CAD   | Computer-Aided Design                     |

| СРТ   | Critical Path Tracing                     |

| CPU   | Central Processing Unit                   |

| CUT   | Circuit Under Test                        |

| DD    | Decision Diagram                          |

| DFT   | Design-For-Testability                    |

| DUT   | Device Under Test                         |

| FFR   | Fanout-Free Region                        |

| FPGA  | Field Programmable Gate Array             |

| FSM   | Finite-State Machine                      |

| HDL   | Hardware-Description Language             |

| HLDD  | High-Level Decision Diagram               |

| IC    | Integrated Circuit                        |

| I/O   | Input Output                              |

| PI    | Primary Input                             |

| РО    | Primary Output                            |

| PPSFP | Parallel-Pattern Single Fault Propagation |

| PRPG  | Pseudo-Random Pattern Generator           |

|       |                                           |

| RTL   | Register-Transfer Level                          |

|-------|--------------------------------------------------|

| SA    | Stuck-At                                         |

| SAF   | Stuck-At Fault                                   |

| SSA   | Single Stuck-at model                            |

| SSBDD | Structurally Synthesized Binary Decision Diagram |

| SoC   | System-on-Chip                                   |

| VHDL  | VHSIC Hardware Description Language              |

| VHSIC | Very High Speed Integrated Circuit               |

| VLSI  | Very-Large Scale Integration                     |

## Contents

| CHAP  | FER 1    | INTRODUCTION                                | 1  |

|-------|----------|---------------------------------------------|----|

| 1.1   | Motiva   | tion                                        | 1  |

| 1.2   | Probler  | n formulation                               | 2  |

| 1.3   | Thesis   | contribution                                | 3  |

| 1.4   | Thesis   | structure                                   | 4  |

| CHAP  | FER 2    | BACKGROUND                                  | 5  |

| 2.1   | Introdu  | ction to digital test                       | 5  |

| 2.2   | Fault o  | odeling                                     | 6  |

| 2.3   | Fault si | mulation                                    | 10 |

| 2.4   | Applica  | ability of fault simulation                 | 22 |

| 2.5   | Chapter  | r summary                                   |    |

| CHAP  | FER 3    | <b>OVERVIEW OF RESEARCH RESULTS</b>         |    |

| 3.1   | Represe  | entation of circuit on macro-level          |    |

| 3.2   | Single-  | pattern fault simulation                    | 31 |

| 3.3   | Parallel | l-pattern fault simulation                  |    |

| 3.4   | Hierarc  | chical calculation of fault injection sites | 50 |

| 3.5   | Overall  | experimental results                        | 51 |

| 3.6   | Chapter  | r summary                                   |    |

| CHAP  | ΓER 4    | CONCLUSIONS                                 | 53 |

| 4.1   | Contrib  | putions                                     | 53 |

| 4.2   | Future   | work                                        | 55 |

| REFEI | RENCES   |                                             | 56 |

| RESEA | ARCH PA  | APERS                                       | 63 |

| Paper | · I      |                                             | 65 |

| Paper | · II     |                                             |    |

| Paper | · III    |                                             |    |

| Paper | · IV     |                                             | 97 |

# Chapter 1 INTRODUCTION

This introductory chapter gives an overview of the area addressed by current thesis. At first, the motivation for the work is given followed by the formulation of the problem and the outline of main contributions. The last part of the chapter describes the organization of the thesis.

## 1.1 Motivation

It is not an overstatement to designate the microelectronics as the one of the most rapidly developing industries in the world. The only half of the century has been passed since the first integrated circuit had been invented in sixties and already billions of ICs stuffed with millions of transistors are produced nowadays. The trend in the digital device development that has been held in accordance with the famous Moore' law [1], [2] for past forty years gives the clear signals: the tendency is not going to stop since the microelectronic market constantly demands new devices with richer functionality, smaller dimensions and better performance.

The success of digital electronics has made a deep impact on the society. The world of digital devices become tightly tied with the everyday life and made people be much more dependent on the correct functioning of surrounding electronics. The last statement brings the problems of reliability of digital devices in a front place, causing dependability to be even more vital than the added value of novel functionality: having a new feature in a mobile phone is certainly very desirable but only if this innovation will not lead to the failures in the basic functionality.

The one of the solutions for the reliability issues is to perform comprehensive testing of the microelectronic product before the shipping it to end customer.

However the development of high quality tests had never been a simple task in digital world, is now turned into a real challenge because of the drastically grown complexity of integrated circuits. According to International Technology Roadmap for Semiconductors [3] increasing integration of microelectronic devices remains the key driver for enhancing the technology of manufacturing test.

The well-known example illustrates that the straightforward test of functionality of a 32-bit adder by exhaustive verification of the correct operation for any combination of the operands will require at least  $2^{64}$  test steps to be executed. Indeed, even using a high-end test equipment, this operation will turn into several hundreds years of testing. However the development of advanced methods had allowed much more sophisticated devices such as microprocessors, ASICs, Systems-on-Chip, etc to be thoroughly tested. Nevertheless the permanent advances in the field of microelectronics demands continuous development of the test technology in order to cope with the increasing complexity of digital devices.

The current thesis is focused on improving of fault simulation technique that is the one of the major issues in the area of digital test. Many test-oriented tasks solved during the digital device design flow are heavily relying on fault analysis. For instance test generation, test quality assessment, fault diagnosis, test set compaction, optimization of built-in self test controller and others problems typically incorporate fault simulation as an intermediate step. Certainly this gives a very clear motivation for the attempts to raise the efficiency of fault simulator: the more accelerated fault analysis is – the more comprehensively the aforementioned tasks could be performed.

Although the successfulness of the designed device is influenced by very many different factors, but the availability of the efficient fault analysis tool could make a significant impact on reliability of the final product.

## **1.2 Problem formulation**

Testing of microelectronic device is a special procedure that aims to check whether the device is working correctly or not. Typically test is conducted after device fabrication in order to ensure that no defects have been appeared in the device during this process.

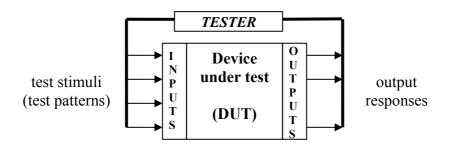

In general, testing procedure consists of set of test stimuli (also referred as *test patterns*) that are being applied to primary inputs of the device under test (DUT). At the same time the output responses are recorded and compared with the expected ones. If the output response mismatches with the reference, then it is said that a failure has occurred. The reason for the failure could be the presence of defect inside the manufactured device.

However the real defects typically are not considered directly during the preparation of test but rather their behavior is simulated by fault models. The

subtask of fault simulation (also referred as fault analysis) has a goal of determining the effectiveness of test patterns in terms of the detectability of faults. For each of test patterns in the test set fault simulator is capable to determine which faults could be detected by applying the given test stimuli.

Obviously the fault simulation can require a lot of CPU and memory resources. In contrast with logic (fault-free) simulation that is done in a one pass and has linear time complexity to the number of gates in the circuit under simulation, the fault analysis requires many copies of the same circuit (that imitate presence of different faults) to be simulated. Thus the straightforward approach to fault simulation is unfeasible in case of large circuits (or large test set).

In this thesis the problem of stuck-at fault simulation of combinational (or scanpath) circuits is addressed. In particular, the presented work attempts to improve the efficiency of the fault analysis methods in terms of time and memory required for the fault simulation of circuit.

## **1.3** Thesis contribution

The main contributions of the current thesis are outlined below.

- The thesis introduces several techniques to perform fault simulation on Structurally Synthesized Binary Decision Diagrams (SSBDD). The usage of SSBDDs gives an opportunity to represent a gate-level design on a slightly higher abstraction level that immediately results in a higher speed of circuit evaluation.

- An efficient single-pattern fault simulation method is proposed [I]. The algorithm is essentially based on the introduced technique of deductive fault list propagation through SSBDD graphs. A reconvergency analysis carried out prior to the simulation determines the most efficient way for simulating each part of the circuit. Besides this, fault-free simulation on SSBDD is used for reducing the list of potential faults.

- The thesis introduces an efficient parallel-pattern fault analysis method. Two novelties are proposed here: the exact parallel critical path tracing algorithm on SSBDD model [II],[V] and the extension of the results of exact critical path tracing beyond the fanout-free regions [II], [III]. The latter uses a special calculation model to determine the detectability of fanouts.

- The approach of construction of optimized calculation model was proposed [III], [VII]. The usage of optimized calculation model lessens the number of unnecessarily repeated computations thus results in a higher analysis speed of parallel-pattern fault simulator.

- The problem of the memory requirements for fault simulation was studied.

A novel approach for reducing amount of memory for simulation is presented together with the results of experiments [III].

- An approach for hierarchical dependability analysis is proposed [IV]. The method uses high-level Decision Diagrams for representation of circuit on register-transfer level and SSBDDs for lower-level description in order to determine the list of malicious faults.

## 1.4 Thesis structure

The presented thesis is organized in a form of overview of the research results that have been published in four scientific papers. The thesis has the following structure.

Chapter 2 forms a background on the discussed topic and makes a review of the state-of-the-art in the corresponded area. Chapter 3 presents an overview of the research results based on the selected publications presented in the last part of the thesis. The conclusions and the perspectives for future work are drawn in Chapter 4. In the last part, the selected papers that lay in the basis of current thesis are presented.

# Chapter 2 BACKGROUND

This chapter presents background information on the topics related to current research. The chapter begins with the brief introduction to the digital test concept followed by the review of the fault modeling technique. The notion of stuck-at faults is described since the fault simulation methods proposed in the thesis are intended to work with stuck-at fault model. Next, the classical fault simulation methods are considered and the review of state-of-the-art in this area is given. At the end of the chapter the various applications of fault simulators in the flow of digital design are analyzed.

## 2.1 Introduction to digital test

The ultimate goal of digital test is to ensure that the device under test (DUT) is functioning according to its specification. In contrast to the verification that checks the correctness of the model of a circuit, testing is performed after the device is physically manufactured. Test program is typically developed during the design cycle with the assumption that the design itself was already verified and is correct.

During the test procedure a special test stimuli are applied to the primary inputs of DUT and the responses of the device outputs are analyzed (Figure 2.1). Because the fabrication process is not perfect, unintendent defects could incidentally appear in the DUT. As the result of defectiveness, the actually recorded responses could differ from the expected ones. In the latter case, it is said that the defect has manifested itself by a failure. Generally speaking, testing helps to discriminate good devices from the faulty ones. In addition, a diagnosis of the failing device can be performed in order to identify the location and type of the defect.

Figure 2.1: The concept of testing

## 2.2 Fault o odeling

By a term *defect* an unacceptable physical deviation of digital circuit from the normal case is assumed [5], [6]. As it was mentioned before, the presence of defect in a circuit could manifest itself by a *failure* (i.e. erroneous behavior of device). However the wide diversity of physical defects that could lead to malfunction of digital devices makes it almost impossible to exactly classify and evaluate them. The list of some sorts of defects in digital circuits could include [6],[4]:

- defects due to imperfection of manufacturing process (e.g. photolithographic errors, missing contact windows, parasitic transistors, incorrect spacing, misalignment, etc)

- material defects (e.g. insufficient purity of surface, contamination)

- age defects (e.g. electromigration)

- package-related defects

In view of the fact that working with large variety of physical defects is impractical, the *fault models* were introduced to offer simplified mathematical description of erroneous behavior. Hence, the term *fault* refers to the representation of a defect using a kind of abstraction.

Although most of fault models neither provide direct correspondence between faults and defects nor exact description of erroneous behavior of circuit, they are very useful for generating and evaluating quality of tests. A good fault model needs to reflect the presence of defects inside circuit precisely enough and be efficient for usage with computational algorithms.

Depending on their nature the fault models have been categorized by several levels of abstraction [4]. Defect-oriented fault models [10] are targeted to describe

the behavior of the defects of specific types, such as open and shorts between transistor lines. As result, defect-oriented fault models usually provide better conformity with the reality but demand sophisticated algorithms for processing. On the other hand, logical-level fault models that deal with the description of circuit at the level of logical signals are easier in processing. They are also independent on physical implementation of design. These facts have been made this class of models be commonly used in VLSI testing.

Unfortunately there is no single model that is sufficient enough for modeling all the possible sorts of physical defects. In spite of this fact, many fault models were proposed so far [5]: stuck-at model, bridging fault models (dominant, wired-AND/-OR, dominant-AND/-OR), delay fault models (gate-delay, path-delay), transistor-level fault models (stuck-opens, stuck-shorts [6]), models dealing with crosstalk faults [7], parametric fault models, etc. Indeed, there exist attempts to create generalized concepts (e.g. faults tuples [8]) that aim to incorporate several types of faults in a single model.

In general every fault model falls into one of two classes: the class of *multiple-fault models* and the class of *single-fault models*. When using single-fault model it is assumed that the only sole fault could exist in a circuit at a time. On the contrary, multiple fault models permit combinations of different faults to occur simultaneously. Obviously, the multiple-fault assumption increases the number of possible combinations of faults exponentially in comparison with single-fault model. For instance, if a fault model permits *n* different types of faults occur at *m* different fault sites, then for single-fault assumption the total number of faults in the model is  $(n \times m)$ . In case of multiple-fault model is considered, there exist  $((n + 1)^m - 1)$  possible combinations of faults. Because the latter amount of faults is too large even for small values of *n* and *m*, the single-fault assumption is usually considered in practice. Fortunately, the experiments have shown that 100% coverage of single faults detects the most of multiple faults as well [4], [9].

#### 2.2.1 Stuck-at faults

The stuck-at fault model is the one most commonly used in digital testing. According to current prognosis made by [3] the stuck-at faults will remain to be the one of the fault models most utilized for the testing of microelectronics for next years.

The presence of stuck-at fault in a digital circuit permanently fixes the value of corresponded signal line to logic one (stuck-at 1, SA1) or logic zero (stuck-at 0, SA0). Although stuck-at faults can be straightforwardly interpreted as a short between signal net and ground (or power) line, many other defects manifest themselves as SA0 or SA1 [10].

In general, there could be  $3^n - 1$  various combinations of stuck-at faults in a circuit with *n* lines (each net could either be affected by presence of *SA0* or *SA1* or

do not contain any fault; the sole combination of totally fault-free circuit is excluded). However the single stuck-at model (SSA) that is commonly used in practice reduces this number to 2n faults. As the current work is focused on SSA-based fault simulation issues, the only single stuck-at model is considered from this point.

Even in case of single-fault assumption not all the faults need to be considered. For instance, two different faults could affect circuit in the exactly same way, i.e. be indiscriminate. Certainly the processing of both such faults is redundant, thus one of them could be dropped out of the list of faults to consider. The technique of reduction of the complete list of faults without losing the quality of defect coverage is called *fault collapsing*

The algorithms of fault simulation are usually very sensitive to the total number of faults need to be handled: the less faults has been included into source fault list, the less time is required for their evaluation. Hence the possible reduction of fault list is very important, because it offers a kind of "pre-optimization" prior to execution of an algorithm itself. Some of well-known techniques of SSA collapsing are discussed below.

### 2.2.2 Fault equivalence for SSA

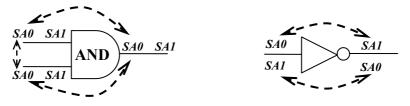

The reduction of fault list is possible by applying *equivalent fault collapsing* for SSA [5],[4],[11]. Assume we have single n-input AND gate to test. The presence of SA0 fault on any of gate I/O fixes the output of gate to logic zero (see Figure 2.2). This leads us to the conclusion that all SA0 faults for AND gate are *equivalent* (i.e. indistinguishable), and considering only one of them is enough. Strictly speaking, two faults are equivalent if their presence changes the output function of circuit in the exactly same way.

As for SA1 there are no equivalent faults for inputs and outputs of AND gate. As result, due to equivalent fault collapsing, the number of non-equivalent faults for n-input AND gate decreases to (n + 2) out of (2n + 2).

It could be shown [5],[11] that similar relations exist between faults for other types of gates, e.g. OR, NAND, etc. For inverter and buffer gates, each fault on input has the equivalent fault on gate output, i.e. the total number of collapsed fault 2 out of 4 uncollapsed.

Figure 2.2: Stuck-at fault equivalence

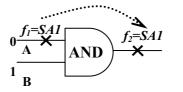

Figure 2.3: Example of fault dominance

### 2.2.3 Fault dominance for SSA

Let us consider two stuck-at faults  $f_1$  and  $f_2$  for 2-input AND gate in Figure 2.3. In order to detect  $f_1$  it is needed to apply the following stimulus for the gate inputs: A = 0 and B = 1 (this is the sole test vector for detection of  $f_1$ ). However, it is easily seen, that the same test vector detects the fault  $f_2$  as well. As result the following conclusion is drawn: the detection of fault  $f_1$  also detects the fault  $f_2$  (it is said that fault  $f_2$  dominates fault  $f_1$ ). However this statement is not reflexive because the detection of  $f_2$  will not necessarily indicate that fault  $f_1$  is also detected (e.g. in case of test pattern A=0 and B=0).

Similar to equivalent fault collapsing, the *dominant fault collapsing* helps to reduce fault list further. For example, by using both fault collapsing techniques for n-input AND gate, only (n + 1) faults need to be considered.

### 2.2.4 Single stuck-at fault collapsing for arbitrary circuit

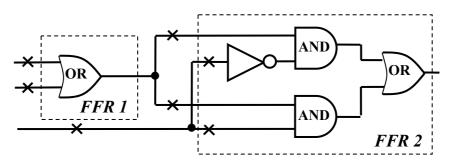

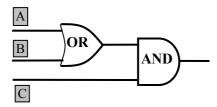

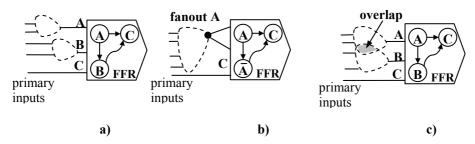

It has been proven that in case of fanout-free circuit the only fault sites on primary inputs need to be considered to test the circuit for all single stuck-at faults [11]. The example of such reduction is illustrated in Figure 2.4. Here the faults that can be removed are marked by a grayed background. The equivalence fault collapsing is illustrated by dashed lines, while the elimination of faults due to fault dominance is marked by dotted lines.

The *checkpoint theorem* [11] states that for an arbitrary circuit, the only faults at primary inputs and fanout branches need to be detected in order to achieve 100%

Figure 2.4: Fault collapsing in fanout-free circuit

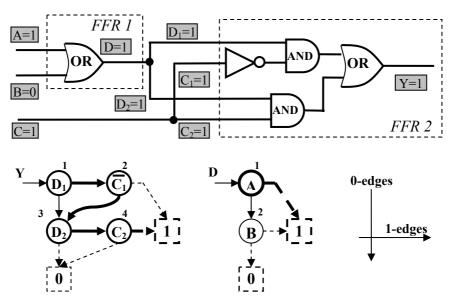

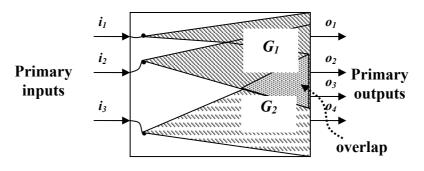

fault coverage of the circuit. In Figure 2.5, a sample circuit with two fanout points is illustrated and the fault sites mandatory for consideration are marked.

The proof of this theorem could be illustrated in the following way. If a circuit has fanouts, the fanout points split the circuit into several fanout-free regions (*FFR*). According to the previous statement, for each of the FFRs we need to test stuck-at faults at the inputs of the region. As the input of a FFR is either fanout branch (e.g. *FFR 2* in Figure 2.5) or primary input (e.g. *FFR 1*) it could be stated that considering stuck-at faults in those fault sites is enough for complete single stuck-at testing of arbitrary circuit. The proof of both theorems is given in [11].

Figure 2.5: Example of fault collapsing in the circuit with reconvergent fanout

### 2.2.5 Contributions of current thesis

Instead of performing explicit stuck-at fault collapsing on gate-level netlist, the fault simulation algorithms proposed in the thesis take advantage of usage of SSBDD graphs for circuit representation (see Section 3.1). Besides other features, SSBDD model provides automatic fault collapsing thus eliminates the procedure of checking whether a fault belongs to the collapsed list or not.

## 2.3 Fault simulation

In contrast with logic (fault-free, true-valued) simulation, the task of fault simulator is to evaluate the behavior of circuit in case of the presence of faults inside. In particular, fault simulator has to determine whether the output response of a circuit is changing due to the influence of a fault or not. A fault which effect propagates to primary outputs under current input stimulus is referred as detected by the current test pattern.

Fault simulator typically works with a specific fault model. The input data of fault simulator is a set of test patterns together with the model of a circuit. In general case, the result of the execution of fault simulator is a *fault table* that shows what of the modeled faults are detectable by each of the given test patterns. In

addition, *fault coverage* (i.e. number of detected faults with respect to the total number of faults) is calculated.

The sections below present the brief description of the traditional fault simulation approaches and the review of the state-of-the-art.

### 2.3.1 Serial fault simulation

Serial fault simulation is the most simple and straightforward way to obtain fault table for a set of patterns. For every test pattern serial fault simulator evaluates fault-free version of circuit at first. Next, the circuit is modified to imitate the presence of a fault (such modification is called *fault injection*). The simulation process is conducted for the fault injected version of the circuit and the outputs responses of both faulty and fault-free copies are compared. The result of the comparison determines whether the fault is detectable by the given test pattern or not. After that, the injected fault is removed and the next fault is inserted. The whole procedure is repeated until all faults in the fault list have been simulated for the given test pattern.

Obviously, serial fault simulation algorithm is very simple in implementation: the only capability to inject faults need to be added to any logic simulator for converting it to fault simulator. However, for *m* faults in circuit the pure serial implementation of fault simulation is at least (m + 1) times slower than just a true-valued simulation.

However there exist general optimizations that can be applied to overcome the inherited slowness of serial fault simulation. For instance, the *fault equivalence* and *fault collapsing* techniques that were discussed in the Sections 2.2.2 and 2.2.4 decrease the number of total faults thus results in the immediate speed gain.

Another optimization called *fault dropping* could be used for the situation when only overall fault coverage of the given test set is requested. For the simulation with fault dropping, the fault is excluded from the list of faults immediately after its detection. Because most of the faults are likely discovered by the first test patterns, the list of non-detected faults will shrunk very quickly and the simulation continues on small set of active faults. This property allows drastically speed-up fault simulation, however the capability to obtain fault table is lost in this case.

It is also possible to slightly decrease the algorithmic complexity of serial fault simulator by putting gates of a circuit in levelized order. In the ordered netlist, all the elements driving values to the inputs of a specific gate are placed prior to this gate. Consequently, the injection of fault can only influence the gates located after the fault insertion point while the I/O values of preceding gates remain unaffected. For this reason, fault simulator has to evaluate only part of the faulty copy of the circuit instead of processing the whole gate list. Usage of compiled-code simulation instead of evaluation of gate-level model is another well-known technique for increasing the simulation speed. In the latter case, the simulator produces a special program (or machine code directly) that is executed on host computer. The purpose of this program is to use native set of CPU instructions for emulation of the behavior of the circuit. Although direct execution is faster than evaluation of circuit model, this approach lacks the flexibility. The compiled program requires complete execution even if the states of the most of nets did not changed, thus making this approach inefficient for the circuits with a small part of signals changing at a time. In addition, this method has portability issues (the simulator needs to work in combination with external compiler or be able to synthesize machine code for different platforms).

In spite of the speed inefficiency of serial fault simulators their simplicity allows to easily adapt them for usage with any kind of fault model. This is the main benefit of serial fault simulation in comparison with more complicated methods (the vast majority of fault simulators are not very flexible in handling different types of faults). However this approach lacks the efficiency on carrying out simulation on stuck-at fault model.

#### 2.3.2 Parallel fault simulation

The fundamental idea of parallel fault simulation is to fully utilize the width of processor data word in order to reduce fault simulation time. For example, if host computer has 32-bit architecture then a logic operation on 32 binary variables can be performed simultaneously by execution of just one CPU instruction (e.g. AND, XOR, etc). The two types of parallel fault simulation are distinguished: *parallel fault simulation* (simulates many faults in parallel) and *parallel pattern simulation* (processes many patterns in parallel).

The only small overhead of parallel simulation is introduced by the demand in conversion (*packing*) of several integer values into bits of a single data word (*packet*). However the additional CPU resources needed for packing and unpacking data are rather insignificant and can be neglected because of overall speed gain.

All the optimization techniques that were discussed in the previous section are also applicable for parallel fault simulator. However the effectiveness of fault dropping is less in case of analysis of many faults in parallel.

#### 2.3.2.1 Parallel fault simulation

An approach that utilizes the width of processor word for processing of multiple faults was firstly proposed in [13]. Assuming that each signal line can have either 0 or 1 value, w signals can be processed simultaneously on a w-bit CPU. The injection of fault to specific circuit line is made by altering of certain bit of w-bit data word associated with the signal. As result, w different copies of the same circuit can be processed simultaneously.

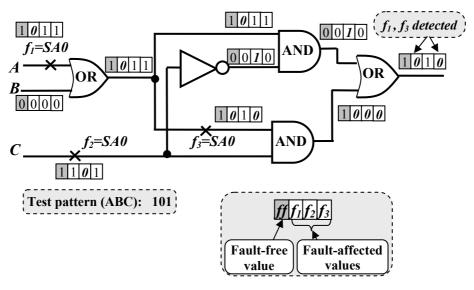

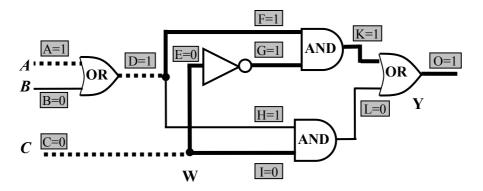

Figure 2.6: Parallel fault simulation example

The parallel fault simulation is illustrated in Figure 2.6 is performed for one test pattern (ABC=101) and three faults by using 4-bit packets: the first bit is used for fault-free simulation and the rest bits reflect the simulation results for injected faults  $f_1$ ,  $f_2$  and  $f_3$  respectively. The faults  $f_1$  and  $f_3$  are detected because the value of corresponded bit in the packet associated with the primary output differs from fault-free value.

Comparing to the serial fault simulator this approach will increase the fault simulation speed in approximately (w - I) times.

As was mentioned before, the fault dropping could be significantly less effective when using parallel fault simulation. While serial fault simulator is capable to exclude fault just at time of its detection, parallel fault simulator does not terminate the simulation of a packet until all the faults that belong to this packet become detected. For example, if a packet contains one hard-to-test fault, the whole packet is kept in simulation run even if the remaining faults in the packet have been already detected.

#### 2.3.2.2 Parallel-pattern fault simulation

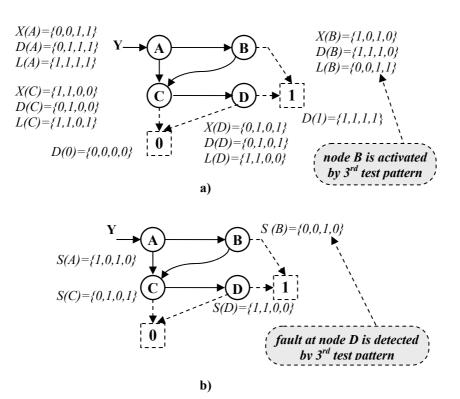

On the contrary to parallel fault simulation *parallel-pattern fault simulation* technique takes advantage of bitwise parallelism for evaluating many test patterns simultaneously. The parallel-pattern simulation (also called *Parallel Pattern Single Fault Propagation* or *PPSFP*) was introduced by Waicukauski et al. in 1985 [14].

In PPSFP a sequence of test patterns is packed into *w*-sized data word where each bit corresponds to a separate pattern. The packet is simulated on fault-free

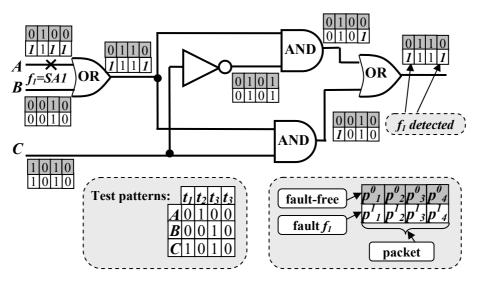

Figure 2.7: Parallel-pattern single fault propagation

circuit to obtain the values of primary outputs for the first *w* test patterns. Then for each fault in the fault list the following actions are repeated:

- 1. fault is injected into circuit;

- 2. parallel-pattern simulation is performed on faulty circuit;

- 3. output responses are compared with the results of true-valued simulation;

- 4. the fault is removed and the next fault is taken for consideration;

The whole procedure is executed until all test patterns become simulated.

The example depicted in Figure 2.7 conducts PPSFP simulation for 4 test patterns and a single fault. In the first run patterns are simulated in parallel for fault-free circuit, while the second run simulates the same patterns after injection of fault  $f_1$ .

Thanks to its parallelism, PPSFP method is almost w times more effective than serial fault simulation. Moreover, unlike parallel fault simulator, PPSFP does not have the effect of degradation of speed gain offered by fault dropping. The drawback of PPSFP approach is the limitation in use only with combinational circuits. For sequential design the state of the circuit should be computed before applying the next test pattern. However this condition is not held for test patterns that are simultaneously processed.

### 2.3.3 Concurrent fault simulation

Concurrent fault simulator [15] is essentially based on the idea of event-driven logic simulation. The simulator exploits the hypothesis that typical fault effect

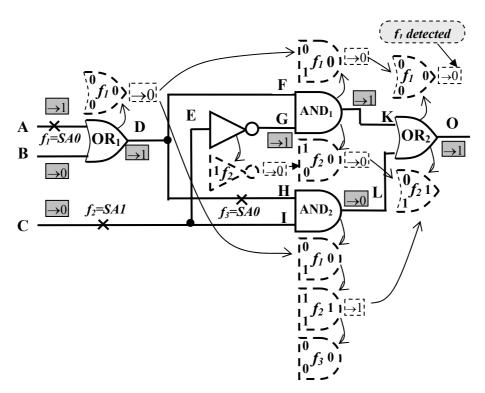

Figure 2.8: Concurrent fault simulation

results in differences for a small part of circuit. Consequently the only affected region need to be analyzed for fault detection.

In concurrent simulation each gate in a circuit has a set of associated *bad gates* (i.e. virtual copy of a gate in case of a presence of fault f). Besides the fault id, a bad gate also contains faulty signal values on its I/O. The bad gates in the sample circuit in Figure 2.8 are drawn by dashed lines.

Initially concurrent fault simulator creates bad gates for the faults with fault site in the same gate (such bad gate is called *fault origin gate*). In the example these are the bad gates created for faults  $f_1$  ( $OR_1$ ),  $f_2$  (INV,  $AND_2$ ) and  $f_3$  ( $AND_2$ ). With the fault effect propagation other bad gates could replicate from the original gates (these gates are called *fault effect gates*).

Concurrent simulation is performed pattern by pattern. A test pattern is applied by emerging events on primary inputs of circuit (e.g. *A*, *B* and *C*). The whole simulation process consists of consequent evaluation of events (changes of signals) on good and bad copies of gates.

Evaluation of events occurred at good gates computes fault-free values of signals. If an event on output of a fault origin bad gate causes signal to be different

from fault-free value, then this bad gate become *visible* (i.e. creates fault effect). The fault origin bad gates  $OR_1/f_1$ , INV/f<sub>2</sub> and  $AND_2/f_2$  in Figure 2.8 are visible.

And vice-versa, fault origin gate become *invisible* if presence of fault does not change its output value (e.g.  $AND_2$  gate with the fault  $f_3$  is invisible because its output coincides with fault-free value).

Propagation of the fault event by visible bad gate to the input of destination gate causes a new *fault effect gate* to be *diverged* and added to the list of bad gates (e.g.  $INV/f_2$  diverges a new fault effect bad gate  $AND_1/f_2$ ). Diverged gates propagate the effect further. On the contrary, a fault effect gate *converges* to its original good gate if signals on its inputs are indistinguishable of fault-free values. Finally, a fault becomes detected in case if the effect of this fault reaches the primary outputs of circuit ( $f_1$  in Figure 2.8).

Concurrent fault simulator is more flexible than other fault simulation methods because the rules of events evaluation, changing bad gate visibility, diverging and converging fault effect gates could be adapted to process the circuit description on different abstraction levels as well as for handling non-standard fault models. Moreover, the elimination of unneeded computation for the parts of circuit not affected by a fault considerably increases the efficiency of the method. However storing many copies of bad gates at run time is a potential memory problem, because the size of the lists is not known prior to the simulation.

A variation of concurrent fault simulation referred as differential fault simulator [16] utilizes the analogous event-driven technique but requires minimal amount of memory for implementation. Unlike the previous method, differential fault simulation deals with single fault at a time. There exists a parallel implementation of differential fault analysis algorithm [17] that speed-ups the fault detection process.

#### 2.3.4 Deductive fault simulation

Deductive fault simulation (firstly proposed in [18]) is completely different in comparison with the methods described above. Deductive algorithm relies on logic reasoning rather than pure simulation (however the simulation is still needed but only to compute fault-free values of signals).

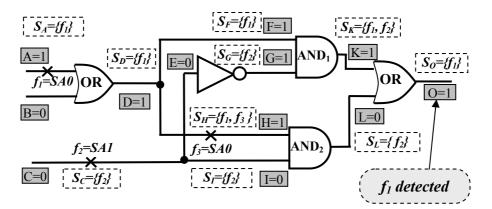

In deductive fault simulation a fault set  $S_x$  is associated with each signal line x. A fault f belongs to the fault set  $S_x$  if the presence of the fault f in circuit flips the state of signal line x. Thus a presence of fault f in the set associated with primary output indicates that f changes the output response of circuit. Therefore the ultimate goal of deductive simulator is to eventually construct fault sets for primary outputs of circuit and unite them into final set of detected faults  $R = \bigcup S_a, o \in PO$ .

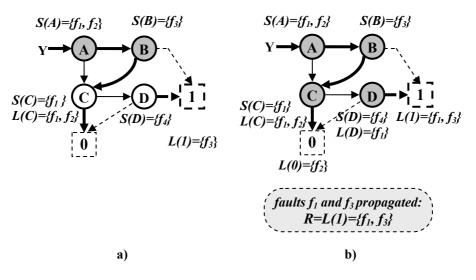

In Figure 2.9 the example of deductive fault simulation is given (with only active three faults:  $f_1$ ,  $f_2$  and  $f_3$ ).

Figure 2.9: Deductive fault simulation

A procedure of deducing  $S_x$  fault sets is conducted as follows. As the first step, the initial fault sets are formed for the primary inputs (e.g.  $S_A$  and  $S_C$ ) by the immediate inclusion of faults on the inputs of circuit. Next, the evaluation of gates begins in the direction from primary inputs to primary outputs. For the single gate with known fault sets on its inputs, deductive simulator derives a fault set for gate output (this process is referred as *fault propagation*). Then the fault at output is included (*activated*) in the propagated list of fault (*fault activation*).

Consider the procedure for propagation fault sets in general. During gate evaluation deductive fault simulator distinguishes between the gate inputs holding controlling values (set of gate inputs  $I_c$ ) and non-controlling values (set of gate inputs  $I_{nc}$ ). A controlling value of a gate is the value that defines the value of gate output: for example a controlling value for AND gate is 0 (because appearance of logic 0 at least on one of the inputs of AND gate forces its output to go into logic 0 state), a controlling value for OR gate is 1, etc. Then two cases are recognized:

I<sub>c</sub>∈Ø (i.e. all gate inputs hold non-controlling values). This means, that the fault effect observed on any of inputs will propagate to gate output (i.e. fault that belongs to any of fault sets of gate input is observable at gate output). For this case the target fault set S' is calculated using the following equation:

$$S' = \bigcup_{i \in I_{nc}} S_i$$

In the example in Figure 2.9 the fault set for the output of  $AND_1$  gate is constructed out of the sets  $S_F$  and  $S_G$  by using the formula above.

2.  $I_c \notin \emptyset$  (e.g. some inputs may hold controlling value). In this case, a fault propagates through the gate only if its effect was propagated to every controlling input while self-masking effect (the appearance of the same

fault effect at any non-controlling inputs of the gate) is absent. The respective fault set S' for gate output is derived as:

$$S' = \bigcap_{i \in I_c} S_i - \bigcup_{j \in I_{nc}} S_j$$

The application of this rule is illustrated by deriving fault set  $S_O$  from the sets  $S_K$  and  $S_L$ .

Finally, to obtain the complete fault set *S*, the potential fault at corresponded signal line (i.e. gate output) need to be activated, i.e. added to the fault set:

$$S = S' \cup f_{at \ current \ signal \ line}$$

The described procedure continues until the construction of fault sets for all primary outputs is finished. As the last step, fault sets associated with primary outputs are united into single set of detected faults  $R = \bigcup_{o \in PO} S_o$ .

The deductive fault simulation is extremely powerful in comparison with simulation-based approaches due to the fact that all faults are processed in a single run (for given test pattern) avoiding re-simulations of the same circuit. However during the simulation process deductive fault simulator spends most of CPU time on logic operations over fault sets (union, intersection and complementation).

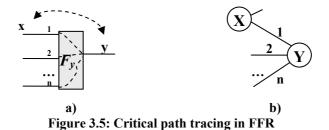

#### 2.3.5 Critical path tracing

As an alternative to the fault simulation, critical path tracing (CPT) algorithm [19] does not conduct any simulations except true-valued one. Instead of that, critical signal lines are traced starting from primary outputs towards inputs of circuit.

During path tracing, a signal line is considered as critical if change of its value causes a flip of the state of primary output. As result, a stuck-at fault that is associated with the critical line (SA0 if the value of signal line is logic 1, SA1 otherwise) should be immediately added to the list of detected faults.

Critical path tracing starts with the primary output. Since primary output is essentially critical, it is added to the list of critical nets and the tracing continues for gate that drives the output. The inputs of the gate are evaluated to determine whether they affect any of critical nets or not. By the result of such evaluation, the inputs of gate may be added to list of critical nets. The tracing continues until all the nets are evaluated (or until no critical nets under evaluation remained).

The process of critical path tracing is presented in Figure 2.10 (the critical nets are marked by bold lines). Note that for exact results, CPT need to be stopped by reaching fanout. Otherwise the *fault-masking* effect could spoil the results of simulation. In the example in Figure 2.10 critical path tracing discovers signal line

Figure 2.10: Critical path tracing technique

C to be critical in respect to primary output. However the fault effect diverges at fanout W continues to propagate by both fanout branches E and I. Finally, the phenomena of *fault masking* becomes apparent at reconvergency point Y, where fault effects on both lines K and L cancel (*mask*) each other hence stopping the fault propagation.

Critical path tracing algorithm provides linear complexity (in respect to the number of nets) within fanout free region of circuit. Unfortunately original implementation of critical path tracing cannot straightforwardly handle fanout reconvergencies hence providing only approximate fault coverage. In order to obtain exact results, critical path tracing algorithm should either be restricted by fanout free region or perform special handling of reconvergent fanouts.

## 2.3.6 Review of state-of-the-art

The methods presented in the previous sections can be characterized as basic types of fault simulation algorithms. However a number of sophisticated optimizations were proposed so far in order to achieve better efficiency of fault analysis. Below we will outline some of the attempts to build powerful algorithms for fault simulation.

Antreich and Schulz have proposed an accelerated parallel-pattern fault simulation method [20]. The key idea of the algorithm is to reduce the number of fanout stems to be unnecessarily re-simulated by identifying of independent fanout branches.

Harel et al. [21] suggested to use a *dominator concept* (in terms of graph theory) for improving the efficiency of PPSFP by the reduction of unnecessary simulated areas of circuit. Another proposed optimization of the paper is implementation of priority queues for maintaining the list of gates waiting for evaluation.

Another improvement of parallel fault simulation method proposed by Maamri and Rajski is based on *stem-region* analysis [22]. For each fault in reconvergent fanout the approach determines a stem-region which limits the simulation area. The stem-region is bounded by so-called *exit lines* that form a set of disjoint cones (from exit-line to primary outputs). If fault is detected on exit line and this line is critical the further simulation is not needed. For fault analysis inside fanout-free regions the method uses CPT technique.

Test-detect fault simulation algorithm proposed by Roth [23] requires faults on gate lines to be evaluated in a backward levelized order. Hence for each fault, the gates that occur later in the order are already considered. This gives the opportunity to stop the simulation of a fault if the propagation path of this fault is converged to a single gate. The further elaboration of this method [24], results in test-detect algorithm refined for parallel use.

Lee and Ha have proposed the efficient version of PPSFP-type simulator [25] that is exploits the idea of eliminating of unnecessarily simulated regions on early stages of fault simulation. This is achieved by examining the detectability of faults and exclusion the following regions out of simulation in case if no faults are detectable at the output of currently simulated FFR or stem region. The method also enhanced with usage of critical-path tracing inside FFRs and efficient implementation of stack of gates under evaluation.

Saab have presented parallel-concurrent fault simulator [26] that relies on the approach of concurrent simulation but simultaneously processes fault groups instead of single faults. The technique for partitioning faults into fault groups reduces time needed for processing of events in concurrent simulator.

Takahashi et al. have extended deductive fault simulation approach for the case of multiple stuck-at fault model [27]. Authors provide the solution for handling very large number of fault combinations by using Boolean functions (represented with the help of shared BDDs) thus cutting down the memory requirements.

Wu and Walker have proposed critical path tracing method [28] that allows to perform exact CPT on a circuit with reconvergencies in nearly-linear time. The method is based on traditional CPT supplemented with a special set of rules to handle various cases of reonvergencies.

The method of approximate fault analysis called fault sampling was proposed in [29] for reducing the efforts of fault simulation. The method works in conjunction with fault simulator to determine the detectability of randomly picked sample of faults (i.e. subset of fault list) and extrapolate these results by using means of probabilities theory.

Jain and Agrawal have proposed another approximate method of fault simulation. Statistical fault analysis [30] uses results of fault-free simulation for producing fault coverage estimation. During logic simulation the number of occurrences of 0- and 1-values for each signal line and number of cases when gate input is sensitized to the gate output are counted. Basing on these values, statistical fault analyzer computes the probability of each fault to be detected. However the both approximate methods cannot provide the exact data about fault detectability.

Besides the conventional approaches, many challenges have been made to increase the speed of fault simulation by delegating part of the process to specially developed hardware accelerators [31], [32]. Many of such attempts utilize reconfigurability of FPGA to emulate the whole circuit under test in reprogrammable logic [33], [34], [35]. However these techniques require additional devices to be attached to host computer thus narrowing their applicability.

Recently a new dimension in the area of accelerating fault simulation speed is being thoroughly explored [36], [37]. The key idea of the approach is to use standard off-the-shelf hardware that is capable for parallel processing to accelerate the well-known fault simulation algorithms. Typically, graphical processing units (which likely contain hundreds of separate processing cores) are programmed for concurrent execution of basic operations needed to run simple fault simulation algorithms (e.g. parallel fault simulation or PPSFP).

#### 2.3.7 Problems with fault simulation algorithms

Although the techniques considered in this section are equipped with sophisticated algorithms for fault simulation, they still have certain drawbacks that slow down the analysis speed. The major disadvantage of deductive fault simulation (Section 2.3.4) is the demand of complex operations on large fault sets that decrease the speed of deductive reasoning. However fault equivalence and fault dominance relationships (Section 2.2.4) can assist in reducing the total number of faults.

Straightforward implementation of parallel-pattern fault analysis (Section 2.3.2.2) results in unnecessary simulation of the parts of circuit that are not affected by a fault. Also re-simulation is performed for the regions that have already been simulated under the same conditions (for instance, if propagation of effect of a fault converges to a single signal line). However several approaches have been proposed to reduce this overlap ([20],[21],[22],[24],[25]), they cannot pretend to completely eliminate the unneeded simulation.

In the latter sense concurrent and differential simulators (Section 2.3.3) are more efficient since they simulate only "active" parts of circuit. However these methods are generalized for any types of circuit description and fault models and do not exploit the advantage of gate-level combinational stuck-at fault simulation. In addition, the parallel versions of concurrent and differential simulators do not provide speed gain comparable with the gain obtained by PPSFP simulators.

Although critical path tracing (Section 2.3.5) is very powerful technique because it offers linear-time complexity, it cannot handle fanout reconvergencies. The proposed exact critical path tracing for arbitrary circuit [28] is based on a set of sophisticated rules and cannot be applied for parallel processing of patterns.

#### 2.3.8 Contributions of current thesis

In this thesis we are attempting to improve deductive (Section 3.2) and parallelpattern (Section 3.3) fault simulation approaches. In contrast with the methods described above we propose to perform fault simulation on a network of macros instead of processing logic gates (see Section 3.1).

As it was mentioned before, the speed of deduction algorithm directly depends on the number of faults taken for consideration. In the thesis we propose fault list reduction technique (Section 3.2.1) as well as the method that is intended to avoid sophisticated fault list deduction for certain parts of circuit (Section 3.2.3).

Parallel-pattern fault analysis approach that is proposed in the current work essentially incorporates parallel critical path tracing technique. In comparison with traditional CPT, the proposed method has been accelerated by parallel processing and the use of macro-level description of circuit (Section 3.3.1). Moreover, the method of parallel critical path tracing is extended for circuit with reconvergencies using a special calculation model (Section 3.3.3 and 3.3.4) that helps to escape unnecessary re-simulations.

## 2.4 Applicability of fault simulation

In the following subsections the main test-related tasks that require intensive use of fault analysis are outlined. This helps to reveal the relevance of the problem of fault simulation performance. The speed of fault simulator is especially crucial while solving the tasks discussed in subsections 2.4.2, 2.4.4 and 2.4.5 since the process of fault analysis is required to be performed many times in a cycle.

#### 2.4.1 Test quality evaluation

An essential task of fault simulator is to evaluate quality of the supplied test program. The quality is measured in terms of *fault coverage* with respect to the specific fault model. Fault coverage indicates the ratio of faults discovered by test patterns in respect to the total number of faults in the model. Calculating the fault coverage and reporting the list of detected and undetected faults is the primary task of any fault simulator. In addition the fault simulators are capable to build a complete fault table with the lists of discovered faults for each test pattern. The latter is necessary for the task of diagnosis.

#### 2.4.2 Test generation

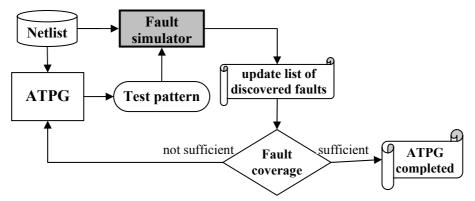

The fault simulator is often used in conjunction with Automatic Test Pattern Generation (ATPG) process in order to verify the generated test pattern (Figure 2.11). This is especially applicable to different types of random pattern

Figure 2.11: Fault simulator in conjunction with ATPG

generators (e.g. [38], [39], [40]) which typically cannot prove whether the produced test pattern detects any of new faults or not.

Genetic algorithms of ATPG ([41], [42]) use fault simulator to compute the fitness function that adjusts the generation process. There exist many other types of simulation-based ATPG (e.g. [43], [44]) that demand tight interaction with fault simulator to achieve the results.

Even in case of deterministic ATPG that target a specific fault (or faults), the fault simulation is applied as a kind of a post processing. In the latter case it helps to reveal the information about other faults (besides the targeted ones) possibly discovered by the test pattern.

#### 2.4.3 Fault diagnosis and fault dictionaries

Another area of applicability of fault simulators is the problem of *diagnosis*. The testing of a device helps to decide whether the DUT is functioning correctly or not. However if the device fails to pass the tests, there is still no information about the cause of malfunction or probable location of defects. Nevertheless such info could be vital in case of repairing the system or improving the production yield.

The diagnostic information assists to determine the source and location of fault thus narrowing the suspected area and type of defect. One of the well-known methods to perform diagnosis is to use *fault dictionary* (this technique is also referred as *cause-effect analysis* [5], [4]). The fault dictionary contains a list of symptoms (i.e. failed test patterns and their output responses) and a specific fault (or group of suspected faults) associated with each symptom.

Test patterns:  $t_1=101, t_2=001, t_3=011, t_4=100$

| Symptom               |                       |                       |                       | Suspected    |  |  |  |

|-----------------------|-----------------------|-----------------------|-----------------------|--------------|--|--|--|

| <i>t</i> <sub>1</sub> | <i>t</i> <sub>2</sub> | <i>t</i> <sub>3</sub> | <i>t</i> <sub>4</sub> | faults       |  |  |  |

| F                     | Р                     | Р                     | Р                     | SA0@A        |  |  |  |

| Р                     | F                     | Р                     | Р                     | SA1@A, SA1@B |  |  |  |

| F                     | Р                     | F                     | Р                     | SA0@C        |  |  |  |

| Р                     | Р                     | F                     | Р                     | SA0@B        |  |  |  |

| Р                     | Р                     | Р                     | F                     | SA1@C        |  |  |  |

Figure 2.12: Fault diagnosis via fault dictionary

In Figure 2.12 a fault dictionary is constructed for sample circuit under diagnosis. During diagnostic test, the information about failed test patterns is recorded by a tester together with the test result. Then a diagnostic program searches the fault dictionary for the corresponding symptom and reports with the diagnosed fault.

A fault dictionary is straightforwardly built out of the fault table: for every fault the test patterns that detect this fault need to be stored as a fault symptom. The fault table in its turn is built by fault simulation which needs to be conducted without usage of fault dropping.

#### 2.4.4 Test compaction

Usage of fault simulator can also help to optimize already available test program without decreasing the fault coverage. This is done for the sake of lessening the cost of test application time and the cost of storage of patterns in tester memory. The technique referred as *test compaction* is capable to achieve good results on reduction of initial test pattern set.

Test compaction exploits several fundamental ideas [11]. First, the method removes the test patterns that do not contribute into detection of new faults. In other words, if a test pattern detects faults that have been already detected by other test patterns, it can be removed without degradation of the test quality. The redundant test patterns can be identified by carrying out fault simulation of test set in reversed-order.

Another approach is based on the fact that ATPG typically targets a specific fault and thus lefts many of primary inputs undefined [45]. Hence by filling-in values for the unassigned inputs (don't care positions) test compaction algorithm attempts to increase the efficiency of the test pattern. Indeed the intelligent substitution of don't cares with the 0 and 1 can significantly raise the number of fault detected by single test pattern.

However the latter approach is heavily relied on fault simulator because it requires many runs of fault simulation over the different variations of test pattern set. This results from the fact that test compactor needs to choose the optimal substitution of undefined bits by zeros and ones.

#### 2.4.5 Built-in self test

Built-in Self Test (BIST) is a widespread DFT technique which enables a silicon device with the additional functionality of self-testing. BIST is very attractive because it provides a number of advantages [4] including excellent test access to the internal structures of device, native at-speed testing, instant test application, low testing cost, ability to test device over its lifespan, etc.

A typical Logic BIST controller consists of a special pseudo-random test pattern generator (PRPG) and response analyzer. A version of Logic BIST that combines PRPG together with the set of pre-defined deterministic patterns is called *Hybrid BIST* approach. However the latter requires additional memory to be allocated on the device.

In the process of design of BIST controller an engineer is faced with number of challenges, e.g. the selection of optimal parameters for PRPG [5], [46] or delimitation of the bounds between deterministic and pseudo-random test [47]. As result, an exploration of the search space of BIST controller needs to be performed to achieve the better fault coverage or solve the tradeoff between the size of additional memory and the quality of test. Similarly to the previous task, the search for optimal solution normally requires many cycles of the fault simulation to be run under various conditions.

#### 2.4.6 Contributions of current thesis

The current thesis introduces an application of fault simulation technique as well. In Paper IV presented in the last part of the thesis, fault analysis is incorporated into the procedure of composing the list of malicious faults (see Section 3.4) that is used in analysis of dependability of design.

The focus of co-authored papers ([VIII], [IX] and [X]) is a laboratory environment for research in the area of digital testing. Although, this topic have been not included into the main scope of current thesis we will try to outline the purposes and main features of the developed tools below.

The main goal of the presented tools is to study the different aspects of design and test using relatively small illustrative examples. In particular, in [VIII] the system for investigating issues of register-transfer level design and test is presented. In addition to wide set of features, it is capable to perform hierarchical fault simulation (on RTL and macro-level) in order to determine the fault coverage of functional testing. In [IX], the presented tool has been supplemented with the possibility to measure and evaluate the effectiveness of various implementations of BIST controller.

Furthermore, the software package of laboratory tools [X] has been enhanced with the system that is capable to study the influence of real defects and draw the correlations between physical defects and fault models.

## 2.5 Chapter summary

The purpose of this chapter was to provide reader with the background information needed to understand the basic principles of fault analysis.

The first part has briefly specified the goal and concept of testing of digital device. Next the notations fault and defects have been explained and the fault modeling issues have been studied. The main emphasis was made on the description and properties of stuck-at fault model that is used in simulation methods described in the thesis.

The approaches described in the chapter represent the main types of fault simulation. The chapter briefly introduces with the advanced techniques that are intended to optimize fault simulation process.

It is also important to understand that fault simulation is a not standalone problem of test quality assessment. Instead, fault analysis is used as an auxiliary step of other test-oriented tasks. Indeed, several applications described in the last part of the chapter require many iterations of fault simulation for achieving the satisfactory results. The latter fact gives especially clear motivation for improving efficiency of fault simulator, since even small advance in fault analysis speed can significantly influence the overall time spent on finding the optimal solution.

# Chapter 3 OVERVIEW OF RESEARCH RESULTS

This chapter gives an overview of the research results presented in Papers I-IV. The scope of the research is mainly focused on improving fault simulation methods for combinational circuits (or circuits enhanced with scan-path) with the usage of stuck-at faults for modeling defects. However, the intermediate steps of research were published in larger extent of papers (including [V], [VI] and [VII]), we have selected only four publications that contain the most important achievements.

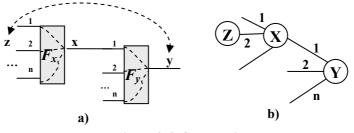

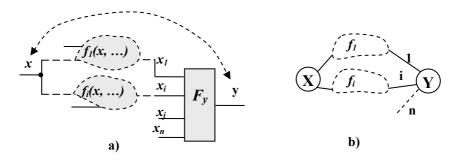

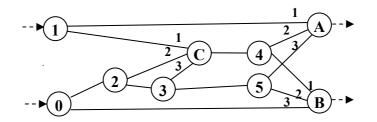

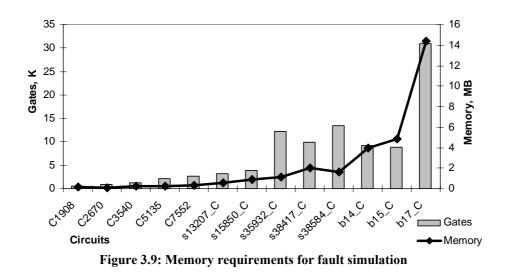

The first paper that is called "*Efficient Single-Pattern Fault Simulation on Structurally Synthesized BDDs*" addresses the problem of single-pattern fault analysis. The paper studies the possibility to perform fault simulation on macrolevel by introducing the version of deductive fault propagation algorithm refined for SSBDD model. Moreover, the paper proposes to use fault-free simulation on SSBDD for shrinking the set of initial fault list. Another contribution of the article is the idea to use topological analysis prior to fault simulation for accelerating propagation process for certain parts of the circuit. Since the implementation of the proposed method was not finished in the moment of publishing, the paper contains rather preliminary data, experimental results and estimations of the potential speedup. The overview of Paper I together with final results is given in Section 3.2.