#### TALLINN UNIVERSITY OF TECHNOLOGY

School of Information Technologies

#### Adeolu Samuel Osidibo 172624IASM

# TEST DATA GENERATION FOR SOFTWARE-BASED SELF TEST OF MICROPROCESSORS

Master's thesis

Supervisor: Raimund-Johannes Ubar

Professor

Co. Supervisor: Adeboye Stephen Oyeniran

Early Stage Researcher

Author's declaration of originality

I hereby certify that I am the sole author of this thesis. All the used materials, references

to the literature and the work of others have been cited. This thesis has not been presented

for examination anywhere else.

Author: Adeolu Samuel Osidibo

07.01.20

2

## **Abstract**

Test program generation has been a dominant challenge of software based self-test in a microprocessor. It was previously generated manually, and this process inflates the cost on test and reduces the fault coverage efficiency. However, a novel approach to automate some of the test processes was proposed in order to expedite a faster delivery of well tested devices to the market, minimize the cost for testing and obtaining the topmost fault coverage. The approach was to generate and organize a test program for a Microprocessor using HLDD [9].

Generating a test program for a microprocessor (MP) requires a test data and selecting a test data is as important as the test program itself [9]. In [1], it was stated that the test data plays a very important role in determining the quality of a test. From previous works, it has been proven that in using HLDD concept, control faults can be detected using conformity test and the data path fault can be detected using a scanning test [1][2]. The HLDD consists of the terminal and non-terminal nodes. The terminal nodes serves as the operations for processing data while the non-terminal nodes represent the control variables given in the MP. Basically, it has been previously proven that control test can be used to detect control faults and pseudo-exhaustive test can be used to exhaustively test the data processing operations for faults.

We propose a new approach for testing for fault coverage in a MP using random patterns, and a combination of random and control test, and random and pseudo-exhaustive test to detect faults in specific modules of a given microprocessor (miniMIPS). In the thesis, a lot of different scenarios of combining different test data for exercising control and data parts of microprocessor modules with the goal of trading off different quality measures like test length (memory space needed for storing test information), test quality (high-and low-level fault coverage), and testing time (by running test programs in a simulation environment).

We demonstrated with experiments which of the methods or combination of methods is more efficient in offering a high fault coverage that will eventually assure the performance and safety of MPs post manufacturing. A low-level fault simulator was used to calculate the fault coverage obtained from our experiments.

#### Annotatsioon

## Testandmete genereerimine mikroprotsessorite isetestimiseks

Lõputöö on kirjutatud inglise keeles ning sisaldab teksti 90 leheküljel, 6 peatükki, 30 joonist, 17 tabelit.

Testprogrammide genereerimine mikroprotsessorite enesetestimiseks on tõsineväljakutse protsessorite usaldusväärse töö tagamiseks. Mikroprotsessorite testprogramme koostatakse käsitsi, mis aga muudab selle töö kalliks, ega suuda garanteerida ka piisavat kvaliteeti. Üheks perspektiivseks lähenemissuunaks testprogrammide sünteesi automatiseerimisel on kõrgtaseme otsustusdiagrammide (HLDD) kasutamine [9].

Testprogrammide genereerimine põhineb testandmete kasutamisel, kusjuures andmete valikust oleneb oluliselt testimise kvaliteet. HLDD formalismi abil saab eristada kahte kontseptsiooni: mikroprotsessori juhtosa jaoks kasutada nn. konformseid (conformity) teste ning andmeosa jaoks nn. skaneerimisteste (scanning tests) [1-2]. HLDD graafid koosnevad terminaal- ja mitteterminaaltippudest. Terminaaltippude abil modelleeritakse andmetöötlusoperatsioone ja mitteterminaaltippude abil juhtsignaale. Vastavalt võib jaotada ka rikkeid mikroprotsessorites – juhtseadmete ja andmetöötlusseadmete riketeks.

Töös esitatakse uudne lähenemisviis automatiseeritud mikroprotsessorite testprogrammide sünteesiks, mis põhineb kolme tüüpi testandmete kasutamisel: testandmed juhtosa testiks ja andmeosa testiks, ning stohhastilised andmed. Töös on välja pakutud ning analüüsitud terve rida erinevaid stsenaariumeid testandmete kombineerimisel, mille eesmärgiks oli leida kompromisse kogutesti pikkuse (testide salvestamiseks vajaliku mälumahu), testimise kvaliteedi ja testimise aja vahel.

Töös on läbi viidud põhjalikud eksperimendid erinevate testprogrammide struktuuridega, mis võimaldas analüüsida ja kindlaks teha parimad lahendused, tagamaks mikroprotsessorite testimisel kõrget rikete katet ja suuremat usaldusväärsust mikroprotsessorite töös. Testprogrammide kvaliteedi määramiseks sai kasutatud Euroopa mikroelektroonika tipptööstusest pärit professionaalset rikete simulaatorit.

## Acknowledgments

Firstly, I give glory to God, my loving father in heaven. His love, empowerment and guidance encouraged me to complete this thesis.

Secondly, I will like to thank my supervisor, Prof. Raimund-Johannes Ubar, for his supervision, advice and support throughout the course of this research. It was a pleasure working with you. I appreciate my co-supervisor Adeboye Oyeniran Stephen, for his technical explanations, motivation and the personal sacrifices he made to make sure I am on track with this Thesis. I am very grateful, and your efforts remains in my heart always.

To my lovely girlfriend, Oluwabunmi Temitayo Awe, I am blessed to have you. Your support, motivation, sacrifice and help have a permanent stamp in me. Thank you for the long nights of studying together for moral support, your patience, and contribution to this thesis. We did it baby!

My deep and sincere appreciation goes to friends, who have become family – Gbenga Niyi-Leigh, Adeniyi Adekoya, and Oluwajoba Adekoya. Your calls, your support, your sacrifice and counsel, and your immense contributions to the completion of this project is immensely recognized. You guys are the best!

Oluwatoorera Kayode-Isola, my amazing friend who is far but near. I recognize your love, prayers and encouragement, thank you so much. It is a wrap now.

I must say a very big thank you to my friends and family who prayed for me, checked on me and continually encouraged me. George Ayankojo, Bolaji and Ebunmide Ladokun, and Oluwaseyi Dada, I appreciate you guys a lot.

God bless you all

## List of abbreviations and terms

ATG Automated Test Generation

ATPG Automated Test Pattern Generation

ALU Arithmetic Logic Unit

CPU Central Processing Unit

CUT Circuit Under Test

DUT Design Under Test

FC Fault Coverage

HLDD High Level Decision Diagram

ILA Iterative Logic Arrays

ISA Instruction Set Architecture

MP Microprocessor

MSF Multiple Stuck-At Fault

NOC Network-On-Chip

RAM Random Access Memory

RISC Reduced Instruction Set Computer

ROBDD Reduced Ordered Binary Decision Diagram

ROM Read-Only Memory

RTL Register Transfer Level

S-A-0 Stuck-At-0

S-A-1 Stuck-At-1

SBST Software Based Self-Test

SOC System-on-Chip

VHDL VHSIC Hardware Description Language

## **Table of contents**

| Abstract                                                     | 3  |

|--------------------------------------------------------------|----|

| Acknowledgments                                              | 5  |

| 1 Introduction                                               | 11 |

| 1.1 Background and problem                                   | 12 |

| 1.2 Objectives                                               | 13 |

| 1.3 Organization of thesis                                   | 14 |

| 2 Digital systems                                            | 15 |

| 2.1 Development life cycle of digital systems                | 15 |

| 2.2 Testing in digital systems                               | 16 |

| 2.2.1 Defects, Faults, Error and Failure                     | 17 |

| 2.2.2 Levels of Abstraction in Digital System Testing        | 17 |

| 2.3 Fault modelling                                          | 18 |

| 2.3.1 Stuck-At-faults Model                                  | 19 |

| 2.3.2 Conditional fault model                                | 20 |

| 2.3.3 Open and Short Faults                                  | 20 |

| 2.3.4 Transistor Faults                                      | 21 |

| 2.4 HLDD based fault models                                  | 21 |

| 2.4.1 Decision diagrams                                      | 21 |

| 2.4.2 Structural Synthesized Binary Decision diagram (SSBDD) | 21 |

| 2.4.3 High level Decision Diagram (HLLD)                     | 22 |

| 2.4.4 HLDD Based Fault Models                                | 23 |

| 2.5 Low level and high-level fault models                    | 24 |

| 2.5.1 Behavioural Bit Stuck-At Fault Models                  | 24 |

| 2.5.2 Branch and Condition Stuck-At Faults                   | 24 |

| 3 Software-based self-test                                   | 25 |

| 3.1 Development of SBST                                      | 25 |

| 3.1.1 MiniMIPS ISA                                           | 26 |

| 3.1.2 HLDD Synthesis                                         | 28 |

| 3.1.3 Test Synthesis from HLDD                               | 31 |

| 3.2 Test program generation with HLDD                        | 32 |

| 3.2.1 High Level Test Data Generation                        | 33 |

| 3.3 Test program generation                        | 46 |

|----------------------------------------------------|----|

| 3.4 Fault simulation                               | 47 |

| 3.5 Conclusions                                    | 47 |

| 4 Development and investigations of the methods    | 47 |

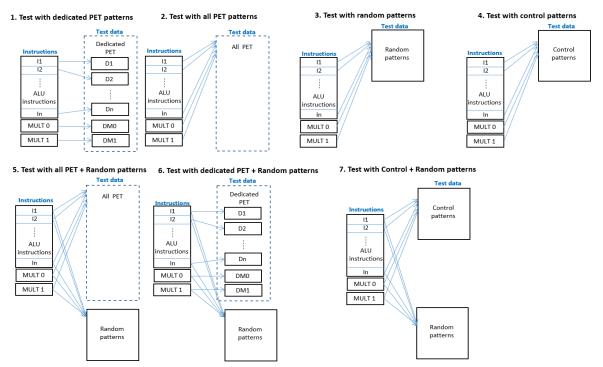

| 4.1 Test templates                                 | 48 |

| 4.2 Set-up of the Experiments                      | 52 |

| 4.3 Combination of different methods               | 53 |

| 5 Implementation and investigations                | 56 |

| 5.1 Goals of the experiments                       | 57 |

| 5.2 Investigations #1                              | 58 |

| 5.3 Investigations #2                              | 60 |

| 5.4 Investigations #3                              | 61 |

| 5.5 Investigations #4                              | 62 |

| 5.6 Investigations #5                              | 62 |

| 5.7 Investigations #6                              | 63 |

| 5.8 Investigations #7                              | 64 |

| 6 Conclusion                                       | 67 |

| References                                         | 68 |

| Appendix 1 – Program Description and Manual        | 71 |

| Appendix 2 – Structure of the miniMIPS processor   | 75 |

| Appendix 3 – CPU specification for the experiments | 76 |

| Appendix 4 – Source Code                           | 77 |

| A Pseudo_template.py                               | 77 |

| B Random_Template.py                               | 81 |

| C Random_data_generator.py                         | 85 |

| D Parameter.txt                                    | 86 |

| E TestProgramGenerator.pv                          | 89 |

# List of figures

| Figure 1: Testing Process of a digital circuit under test                        | 16     |

|----------------------------------------------------------------------------------|--------|

| Figure 2: Levels of abstraction of digital systems [11]                          | 18     |

| Figure 3 AND gate with two inputs                                                | 19     |

| Figure 4: SA1 in an AND gate                                                     | 19     |

| Figure 5: Representing an RTL data path with HLDD [4]                            | 22     |

| Figure 6: SBST generation framework                                              | 26     |

| Figure 7: Structural representation of miniMIPS registers [36]                   | 27     |

| Figure 8: Types of instruction formats                                           | 28     |

| Figure 9: AND instruction architecture                                           | 28     |

| Figure 10: MiniMIPS HLDD model using 4 instruction sets                          | 30     |

| Figure 11: Synthesis of HLDD for miniMIPS [9]                                    | 31     |

| Figure 12: Example of test generation                                            | 32     |

| Figure 13: High-Level test data and test program generation                      | 33     |

| Figure 14: Mapping of miniMIPS instruction formats and the HLDD functional value | riable |

|                                                                                  | 38     |

| Figure 15: Algorithm for conformity test                                         | 38     |

| Figure 16: Structure of Conformity test                                          | 39     |

| Figure 17: Structure of Scanning Test                                            | 43     |

| Figure 18: Algorithm for scanning test                                           | 44     |

| Figure 19: PET combination to All PET Test Patterns                              | 45     |

| Figure 20: Test Program Generation process with four templates                   | 46     |

| Figure 21: HLDD Structure for method 2, 3, and 4                                 | 49     |

| Figure 22: ADD structure in miniMIPS ISA                                         | 49     |

| Figure 23: Set-up of the experiments                                             | 53     |

| Figure 24: Experiment structure for experiments 1 - 7                            | 54     |

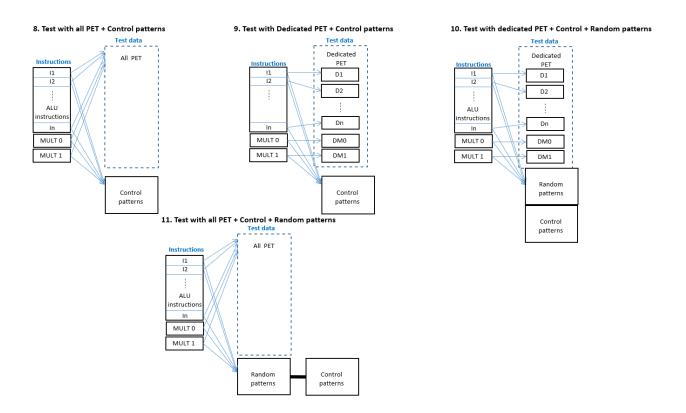

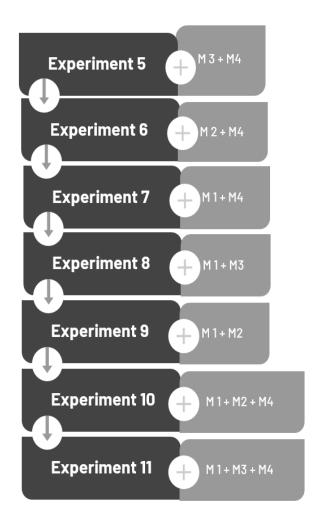

| Figure 25: Experiment structure for experiments 8 – 11                           | 54     |

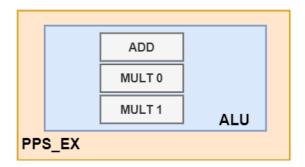

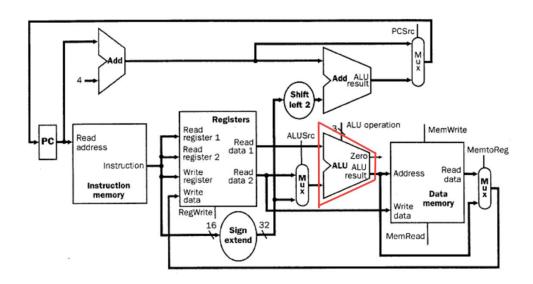

| Figure 26: Structure of miniMIPS execute module                                  | 55     |

| Figure 27: Combination of different methods                                      | 56     |

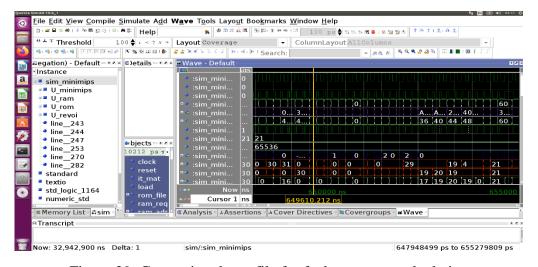

| Figure 28: Test program generator response from Linux terminal                   | 72     |

| Figure 29: Generating dump file for fault coverage calculation                   | 73     |

| Figure 30: Structure of the miniMIPS processor                                   | 75     |

## List of tables

## 1 Introduction

This thesis focuses on a new approach of testing microprocessors with software based self-test by combining different test data generation methods to detect faults in microprocessor modules. A novel concept of HLDD synthesis was used to generate the test program while implementing the combination of test data.

This chapter discusses the background and problem, subsequently, the goal of the thesis, and lastly, the overall structure of this work.

## 1.1 Background and problem

The increase in technological advances has enabled much more complex digital systems (DS) to be built. Massive parallel computing and new design paradigms like System-on-Chip (SoC) and Network-on-Chip (NoC) now exists and needed in-depth research to develop new algorithms and design and test methods, based on microprocessors. As more complex digital systems are being developed, it becomes more evident that Moore's law is continually being proven. Moore's law emphasize that the number of transistors on integrated circuits doubles every 18 months [5] [6]. Fragility of transistors becomes more rampant as the microprocessors undergo rigorous manufacturing processes. Defects becomes inevitable in the transistors of MPs, which could lead to faults in the MPs and could bear severe consequences, especially when the complex system is a critical system. The failure of such system could cause loss of sensitive data, lives and properties. The severity of a fault in the transistors on a MP helps to emphasize the importance of testing to guarantee and improve the reliability of any MP during the operational stage.

In the recent decade, the semiconductor industry was challenged to develop novel testing methods that can be integrated in MP test flow. Without a humongous budget, the testing methods to be developed are targeted at high quality product development. A test method that suits the description was first proposed in 1980 [3], and it is called Software-Based Self-Test (SBST).

For the main purpose of testing the processor, the operational approach of SBST is to execute the test program on processor itself and its surrounding resources [4]. As mentioned earlier, this method eradicates the need for external hardware, which may be expensive, and the time of the test is limited with the performance of the processor. The

main subject in the SBST methodology is the test program generation, which must comply with the high-quality fault coverage standards imposed by the industry [4].

Self-test programs for microprocessors have emerged from been written manually, as a novel formal approach for modelling the high-level functionality and possible faulty behaviours was developed; High-Level Decision Diagram (HLDD). HLDDs can be considered as a generalization of logic level Binary Decision Diagrams (BDD) [4].

From previous works, it has been proven that in using HLDD concept, control faults can be detected using conformity test and the data path fault can be detected using a scanning test [1]-[2]. The HLDD consists of the terminal and non-terminal nodes. The terminal nodes serve as the data path while the non-terminal nodes represent the control variables given in the MP. Using HLDD, control test can be used to detect control faults and pseudo-exhaustive test can be used to exhaustively test the data processing operations for faults. However, as varieties of approaches of MP tests spikes up the interest in this topic of academia and industry as well, a combination of approaches may contribute immensely to the effectiveness of MP testing and improve testability.

## 1.2 Objectives

The goal of the thesis is to develop different methods for the combinations of test data for microprocessor software based self-testing. The Execute module of the MIPS microprocessor was partitioned into three sub- modules: ALU (arithmetic and logic operations), MULT1 and MULT2 (multiplication operations).

The section above identified that previous works have been done to improve SBST, develop test program for SBST, and develop different approaches in testing the control part and the data path of a microprocessor. The approaches applied in testing the control part and data path of a MP fulfils the constraints for test data generation. To further deduce the possibilities of these approaches, this thesis presents the following goals:

- Develop different combinations of test data for microprocessor software base selftesting.

- Develop test templates that enables the test program generator to handle various combination of test data.

• Carrying out simulation experiments through the developed methods to evaluate the quality (SAF coverage) of four basic test algorithms separately and evaluate the possible contribution of each test approach.

## 1.3 Organization of thesis

The thesis is organized as follows:

In chapter 2, an overview of the digital system is surveyed. The area to testing digital systems and various fault models were discussed, alongside the concept of high-level decision diagram (HLDD).

Chapter 3 covers the overview of software based self-test and its development. An indepth view of HLDD was covered, including how it is used to generate test programs for the miniMIPS processor. The chapter also contains the test data generation stage, preceding the test program generation. Chapter 4 entails the development of our proposed methods in stages and the approach we applied in order to combine the 4 methods. We implemented the proposed methods by performing various experiments and analysed the results.

Lastly, the summary and conclusion of the thesis is presented in chapter 6.

## 2 Digital systems

In today's world the word digital is more common than sliced bread, so are its techniques are widely known and utilized in all sectors of life. According to [27] which described digital systems as a combination of devices designed and manipulate logical information or physical quantities that are represented in digital form that is the quantities can take on only discrete values. Arguably digital systems applications in the world of electronics, as well as other major technologies, have performed better than any other systems in any other era.

## 2.1 Development life cycle of digital systems

Every complex system goes through a development life cycle, i.e. the detailed plan for how to develop, alter, maintain, and replace a system to produce a system with the highest quality and lowest cost in the shortest time.

Digital system undergoes 3 stages which includes

- Design

- Production

- Operation

These stages are set up to mitigate the possible misconceptions that may or may not occur, every digital systems development is prone to human and system error at every stage, Each stage has sublevels with the Design stage consisting of specification, implementation, realization for Production possesses pilot and full while the Operation has the Installation and Maintenance sub levels [28]. With a wide ranch of possible errors manifesting any possibly every stage of development it is mandatory to undergo reviews and checks with every component and stages associated with the development life cycle of digital systems. Each stage undergoes reviews, as for the Operation stage requires possible repairs for faults, dividing the systems into level, with the considerations of various factors responsible for the faults encountered. System Designs need Verifications in a bid to check the correctness for each step employed, production stage also undergoes

testing which is where our focus will be centred upon in the next couple of headings in this chapter.

## 2.2 Testing in digital systems

Testing is a concept widely practiced in all sectors of life. Although the approaches may differ slightly, the fundamental achievement remains absolute and is made manifest in the process which is an endeavour in determining the overall correctness of a system with little to no doubt by exposing it to the hardest levels of scrutiny it can possibly handle.

This philosophy also rings through in the aspects of digital systems, which is often referred to as a black block experiment at every level of development to determine correct functionality with the application of stimuli at the input and observing the response on the output [28].

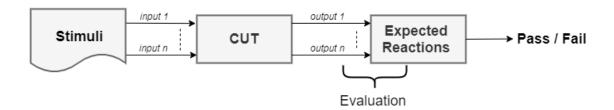

The investigation of the output includes the comparison of its expected reaction with the yield presented amid the introduction of stimuli, this process is known as circuit under test (CUT) as we will see in the figure below elaborating the testing process of a digital circuit under test.

Figure 1: Testing Process of a digital circuit under test

Digital systems become more complex over the years as a result of technological advancements, components become less testable which makes development complex, with this growing complexity and technological advancement in digital systems, problems tend to arise during testing phases since testing is required to encompass multiple activities in the life of a system. These possible occurrences will be discussed extensively in the next topic.

#### 2.2.1 Defects, Faults, Error and Failure

Common terms that are familiar with researchers who undergo testing with digital systems include errors, faults defects and flat out failures. These amongst other phrases are the possible red flags expressing incorrectness of a system.

A defect in an electronic system is the unintended difference between the implemented hardware and its intended design [33].

An error is the manifestation of a fault or multiple faults expressing the deviation from the appropriate behaviour in a system.

Failure indicates a fatal issue in a system or in its module which is making the system inoperative or unresponsive.

A fault depicts the presence of defects which could either reflect a temporary or irreversible change in hardware [15]. It could either be structural or physical forms.

There is a bit of a comparison and contrast when we discuss errors and faults in a system, the appearance of an error automatically implies the presence of fault or some faults, however, faults do not necessarily cause error history has proven systems to work well for year even with the possibility of faults proven from stress test which have a slim chance of occurring in real life. It is important to detect faults that can lead to errors in systems so that they can be mitigated, guaranteeing systems functionality at optimum capacity for a long period of time.

#### 2.2.2 Levels of Abstraction in Digital System Testing

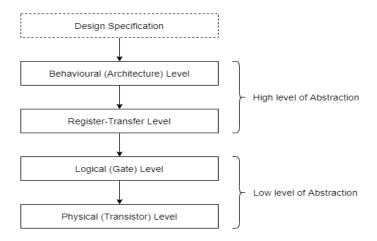

This expresses the physical borders of digital systems, also known as series of abstraction, is the levels from the topmost to the bottom with which the digital system is designed. This principle is adopted to manage complexity and promote order when developing a system from the conceptual state even to the highest level.

Figure 2: Levels of abstraction of digital systems [11]

The series are grouped together into two levels as we can see in the above figure, there is a low level of abstraction and the high level. The logic and the physical level accounts for the low level, the high level of abstraction is accounted for in the RTL and behavioural levels [29].

## 2.3 Fault modelling

In the area of test generation and fault simulation, integrals part of digital design, the diversities facing both centralize focus is enormous in respect to fault detection despite the similarities. Fault models are essential to the test generation and evaluation so much so that a wide range of fault models exist in determining the nature and behavioural defects in digital circuits.

The outcomes of test generation and fault simulations is highly predicated on the fault models, which usually faces a back and forth between cost and quality of test, sadly this is not enough to guarantee an accuracy in detecting faults in accordingly, a blend of various deficiency models at numerous cases are utilized in the age and assessment of test vectors.

A few faults have illustrated that numerous recognize test designs with high coverage give a high demonstrative resolution as well as can help boost the inclusion between nodes. This methodology makes the ATPG procedure increasingly troublesome and CPU-concentrated, yet it is quite simple to apply and doesn't require any adjustment in the test-pattern-generation flow.

#### 2.3.1 Stuck-At-faults Model

Originally stuck-at fault is the widely proposed test for the logic circuit without the application of inputs because the fault suggests that faults will inevitably present itself when logic variables are stuck at 1s or 0s, relying on a percentile outcome in every sequence.

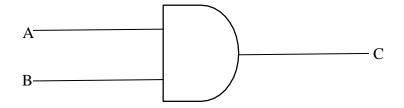

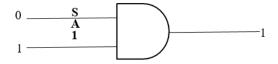

Consider an AND gate consisting of two inputs (A and B) and an output C

Figure 3 AND gate with two inputs

Table 1: Truth table for an AND gate (no faults)

| A | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Let us assume that there is an SA1 at input A, if the logic value at A is 0 or 1, the logic value will remain as 1. Normally, if A=0 and B=1 then the output C=0 but due to the SA1 at input A then output C will be always be 1.

Figure 4: SA1 in an AND gate

Stuck-at fault has proved to be effective and efficient with a technique modelled with electromagnetic relays coils that become automatically stuck at the appearance of a fault [8]. However, its complexity becomes detrimental when handling test generation especially for a large number of faults present in a system, exposing its inaccuracy (over reliance on the percentage of sequence) in modern-day nanoelectronics technology.

#### 2.3.2 Conditional fault model

This is a functional fault model that includes functional verification for every circuit either with partial or complete design level. This is also represented as an input pattern fault model possesses similar attributes to Stuck-at fault (SAF) model nevertheless, its level of accuracy proves valuable in applications to diminish complexity in test generation in modern-day nanotechnology and microprocessor [4].

**Definition 1**: A fault  $(l_i/\alpha, l_j = \beta)$ , where  $l_i$  and  $l_j$  are two lines in a circuit and  $\alpha, \beta \in \{0,1\}$  is a conditional stuck-at (CSA) fault if  $l_i/\alpha$  refers to the fault  $l_i$  stuck-at  $\alpha$  and  $l_j = \beta$  refers to the requirement that some test vector for the stuck fault  $l_i/\alpha$  produces the value  $\beta$  on line  $l_j$ . This test vector is then said to detect the CSA fault  $(l_i/\alpha l_j = \beta)$ .

The definition according to [10] includes the null condition possibility corresponding to a normal stuck fault, where  $(l_i / \alpha l_j = \beta)$  is simply  $(l_i / \alpha)$  and no  $l_j$  or  $\beta$  is specified. This type of CSA faults is going to be called null condition CSA faults. The expression "completely specified CSA fault" will be used whenever it is necessary to emphasize the fact that both the condition line and the condition value have to be specified, as opposed to the null condition CSA faults.

In a bid to improve test generation and fault coverage numerous fault models have been created by researchers over the years, with unique components used for uncovering in respect to faults.

#### 2.3.3 Open and Short Faults

Short faults can also be called bridging faults. This type of fault exists in the wire that interconnects the transistors that forms the circuit [11]. Also known as interconnects faults, it occurs due to the broken connections between different points that are expected to be connected in the circuit. Correspondingly, short faults exist whenever an accidental connection occurs between nodes that are not asserted to be connected.

#### 2.3.4 Transistor Faults

The stuck-at fault cannot precisely emulate the behaviour of fault at the transistor level because of the multiple transistors that are used to construct CMOS logic gates [11]. Due to the occurrence of switching at the transistor level, there is a probability that a transistor would be stuck open or stuck short. Both possessing the idea that a single fault can affect different combinations of fan-out branches.

#### 2.4 HLDD based fault models

#### 2.4.1 Decision diagrams

Decision diagrams are methods of modelling digital systems at various level of abstraction. This can be modelled at both low and high levels of abstractions. The low level which is the logic level possesses binary features which are popularly referred to as BDDs and the other which deals with the behavioural and the RTL level is known as the HLDDs.

Binary decision diagram (BDD), a system for modelling digitally has been the standard in a data structure in computer-aided design (CAD) for manipulating Boolean functions at various levels of abstraction [9]. Over a jubilee ago when it was introduced, researchers have proposed other new data structures like the Reduced ordered BDD, Ternary decision diagram (ROBDD), Edge-Valued decision diagram (EVBDD), zero suppressed (ZBDD hybrid BDDs (HBDD) and a host of others, with each possessing a level of simplicity while retaining unique qualities which made BDDs one of the most popular representations of Boolean functions.

#### 2.4.2 Structural Synthesized Binary Decision diagram (SSBDD)

SSBDDs are unique to other binary decision diagrams because they possess the ability to map logic circuits directly from the gate level structure. This functionality allows the modelling various objectives in testing like delays on paths, fault-masking, signal paths etc. a feature all other BDD do not possess.

#### 2.4.3 High level Decision Diagram (HLLD)

High-Level Decision Diagram (HLDD), another alternative of Decision diagram that represents digital systems from the RTL to the behavioural levels of abstraction. The data processing operation of HLDD occurs using nodes, a technique which exhibits an extension of SSBDDs methods for test generation and fault simulation [21]. It comprises of terminal and non-terminal nodes representing boolean variables from structurally synthesized BDDs as boolean vectors or high level algebraic operations possessing not only the ability to describe the structure of a system usually synonymous to logic level circuits but also the working behaviour of the system thereby extending to the high level functions of the digital system.

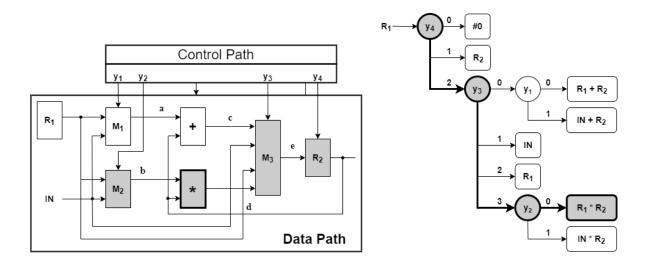

Figure 5 expresses the functionality as well as the structural components of a circuit represented by an RTL data path using an HLDD. As you can see the data path circuit enumerates R1 and R2 registers with non-terminal nodes, internal nodes y1-y4 with intermediaries between the control unit and data with data buses.

Figure 5: Representing an RTL data path with HLDD [4]

Seeing from the diagrams above the procedure for calculating the register variable  $R_2$  assumed IN  $R_1$ ,  $R_2$  from left to right. Using HLDD,  $R_2$  next state (direction) is calculated in each non-terminal node  $y_k$  of  $G_{R_2}$ , predicated on the value of the  $R_2$  using the expression shown by each terminal node, For instance, if  $y_4 = 4$ ,  $y_3 = 5$  and  $y_2 = 3$ ,  $R_2 = R_1 * R_2$  is activated, then the update is stated in  $R_2$ .

The HLDD nodes account for the structural components of the circuits as does the topology covers the behavioural aspect.

#### **2.4.4 HLDD Based Fault Models** [2]

In the definition of HLDD according to [2], it is a graphical representation of a given discrete function F(Z) and it is a directed acyclic graph that can be defined as a quadruple  $Gz = (M, \Gamma, Z, F)$  with a set of nodes M, a mapping  $\Gamma$  from m to M. In this equation,

- M is a finite set of nodes

- $\Gamma$  is a finite set of edges

- Z is a function which defines the variables labelling the node

- F is a function on  $\Gamma$ .

M is divided into two subsets of node: non-terminal  $M_N$  and terminal  $M_T$  nodes.  $\Gamma(m) \subset M$  represents the set of all successors of the node  $m \in M$  and  $\Gamma^{-1}(m) \subset M$  denotes the set of all predecessors of m. The graph has a root node  $m_0$  with  $\Gamma$ -1  $(m) = \emptyset$ . The nonterminal nodes  $m \in M_N$  are labelled by variables  $z(m) \in Z$ . The terminal nodes  $m_k \in M_T$  are labelled by sub-functions  $z(m_k) = f_k(Z_k)$ ,  $f_k(Z_k) \in F$ , which may be as well variables  $z_k \in Z$  or constants.

For each value e from a set V(z(m)), there is an existence of a corresponding output edge  $(m, m^e)$  from the node m into the successor node  $m \in \Gamma(m)$ ,  $e \in V(z(m))$ .

$Z^t$  a vector of values assigned to Z at a time t. The edge  $(m, m^e)$ , where  $e \in V(z(m))$ , is activated by  $Z^t$  if z(m) = e. A given path  $I(Z^t) = (m, n)$  in the HLDD is called the activated if all edges on the path are activated. The activated by  $Z^t$  edges form a full activated path  $I(Z^t) = I(m_0, m_k)$  which determines the value of the graph variable  $f_k(Z_k)$  from the root node  $m_0$  to one of the terminal node  $m_k$ .

The HLDD uses the cycle-based modelling theory for evaluating the behaviour of a digital system. The usage of this theory insinuates that the actuation of a circuit or system state at a particular cycle is possible, based on the exactness of the system behaviour modelling required.

## 2.5 Low level and high-level fault models

Growing complexities in digital systems have directly reduced the observability of internal components thereby narrowing down effective manipulation during testing, with this looming setback, adequate fault coverage may not be evaluated using certain models. Speed testing has become a commonly used approach to attain quality tests.

Test pattern generation in digital circuits has two critical approaches from its levels of abstraction [32]. First is identifying the appropriate model relatable to the physical fault and the other is inducing the respective models in generating patterns in identifying them. In most cases, researchers have often defined physical induced faults, which are also referred to as low-level faults which become evident on higher levels as convenient reasons why fault models from logic level such as stuck-at faults can be adaptable for fault modelling during test generation on a higher level.

In this section, we will discuss a few fault models at logic level testing which bear similarities to fault models at behavioural and R-T level giving rise to mapping low-level faults to High-level fault models.

#### 2.5.1 Behavioural Bit Stuck-At Fault Models

It is common knowledge that Stuck -at fault models at logic level works when signals and variables is encoded in either stuck at 1 or 0 however when this low-level fault model is clearly mapped at behavioural and R-T level it becomes quite useful as well. Stuck- at fault models components at R-T level are synthesized to specific logic component thereby implementing input and outputs with that connection [32]. Although this approach can only model a subgroup of physical fault, it proves the potential physically induced fault possess even at higher levels in test generation.

#### 2.5.2 Branch and Condition Stuck-At Faults

Branch stuck-at fault reflects a given section which behaviour is stuck at. These could be a chosen statement or a condition (if, else) statement whereby the condition is either suck at true or stuck at false.

A choice in a branch articulation might be founded on various conditions associated through consistent administrators. A condition may likewise be utilized in contingent assignments and watched practices

Generally, low-level abstraction is regarded in the physical subset of a circuit, but it really isn't the case all the time because the logic level and R-T level can be categorised as that level up abstraction as well [31] that is why this section discusses certain ways in which low-level faults can be mapped up to behavioural level after undergoing sensitization. These type of fault models are quite advantageous in delivering test vectors even to levels beyond the behavioural level of a circuit.

## 3 Software-based self-test

This chapter discusses the proposed formalised method used for SBST program synthesis for MPs. Using the HLDD model, the test program generation for microprocessor is in two levels: The system level and the module level of the microprocessor. Each HLDD presents the behaviour of a module, and the network of HLDDs presents the behaviour of the system as a whole. At the module level of the microprocessor, the nodes of the HLDDs are the target of test generation, while the HLDDs themselves are the targets at the system level. The HLDDs (module) tests T(*m*)that were generated locally are embedded into the system level test program template. This entails that the test stimuli for the modules will be made controllable and the results of the tests will be made observable at the system level [4].

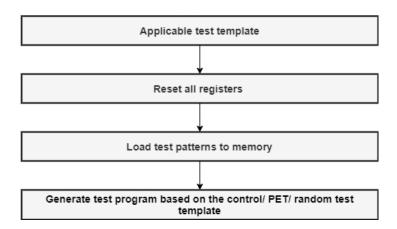

## 3.1 Development of SBST

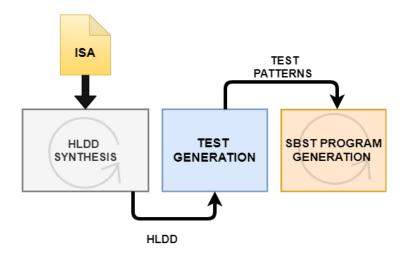

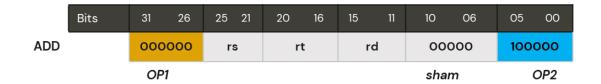

This section introduces the SBST generation framework. Figure 6 shows a generic overview of the framework. It consists of three main modules: HLDD synthesizer, test vector generator, and an SBST-generator synthesizer which converts test vectors into test programs using prepared test code templates [4]. The translation from a set of instructions into a test program is demonstrated on a 32-bit RISC MiniMIPS microprocessor [30] according to instruction set in MIPS architecture [30].

Figure 6: SBST generation framework

#### 3.1.1 MiniMIPS ISA

An instruction set architecture, ISA is an abstract representation of a processor and its functionality provided in the architecture documentation. These includes the description of the general-purpose registers, flags, list of instructions, assembly language syntax and their binary representation [4]. These descriptions are presented in a specific format that can be transformed in High-level decision diagrams. Given this information, test programs can be created. In this section, the open-source microprocessor miniMIPS is considered. The miniMIPS has 32 registers that are 32 bits long. A structural representation is depicted in Figure 7.

| Register    | Assembly<br>Reference | Usage                               |

|-------------|-----------------------|-------------------------------------|

| \$0         | \$zero                | \$zero                              |

| \$1         | \$at                  | Reserved for assembler use          |

| \$2 - \$3   | \$vO - \$v1           | Result storage                      |

| \$4 -\$7    | \$aO - \$a3           | Argument storage                    |

| \$8 - \$15  | \$tO - \$t7           | Temporary values                    |

| \$16 - \$23 | \$sO - \$s7           | Saved registers for procedure calls |

| \$24 - \$25 | \$t8 - \$t9           | More temporary values               |

| \$26 - \$27 | \$k0 - \$k1           | Reserved for OS                     |

| \$28        | \$gp                  | Global pointer                      |

| \$29        | \$sp                  | Stack pointer                       |

| \$30        | \$fp                  | Frame pointer                       |

| \$31        | \$ra                  | Return address                      |

Figure 7: Structural representation of miniMIPS registers [36]

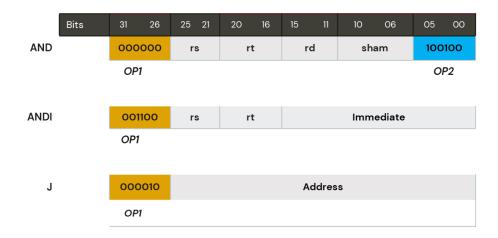

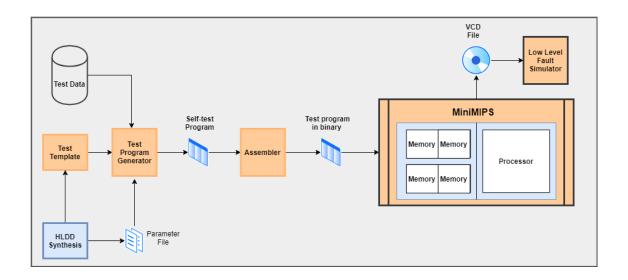

The instruction encoding contains different fields with specific encoding instructions that describe the function of the module. The rs, rt, rd fields hold the address of the registers where the operands and results of the functions are stored. OP1 encodes the type of instruction and OP2 encodes a type of registers for the instruction. Immediate defines the immediate value as an operand and the field address contains the address where to jump to [9]. The miniMIPS instruction format used can be categorized into three distinct types as shown in Figure 8.

Figure 8: Types of instruction formats

Figure 9 shows an AND instruction description of the miniMIPS processor manual [30]

Figure 9: AND instruction architecture

## 3.1.2 HLDD Synthesis

High-level decision diagrams can be constructed from ISA. The HLDD can be constructed by representing the instructions given in the ISA in a structural format as shown in Table 2.

Table 2: Expansion of the miniMIPS ISA [9]

| S/N | Instruction | OP1         | OP2          | Mnemonics             | ISA Level Operation         |

|-----|-------------|-------------|--------------|-----------------------|-----------------------------|

| 1   | ADD         | 000000 (0)  | 100000 (32)  | ADD rd rs rt          | rd= rs + rt                 |

| 2   | ADDI        | 001000 (8)  | -            | ADDI rt rs I          | rt= rs + I                  |

| -   | ADDIU       | 001001 (9)  | -            | ADDIU rt rs I         | rt= rs + I                  |

| -   | ADDU        | 000000 (0)  | 100001 (33)  | ADDU rd rs rt         | rd= rs + rt                 |

| 5   | AND         | 000000 (0)  | 100100 (36)  | AND rd rs rt          | rd= rs AND rt               |

|     | ANDI        | 001100 (12) | -            | ADDI rt rs I          | rt= rs AND I                |

| 7   | BEQ         | 000100 (4)  | -            | BEQ rs rt offset      | If rs= rt then branch       |

|     | BGEZ        | 000001 (1)  | 00001 (1)    | BGEZ rs offset        | If rs >=0 then branch       |

| 9   | BGEZAL      | 000001 (1)  | 10001 (17)   | BGEZAL rs offset      | If rs >=0 then procedure    |

| 10  | BGTZ        | 000111 (7)  | =            | BGTZ rs offset        | If rs > 0 then branch       |

| 11  | BLEZ        | 000110 (6)  | -            | BLEZ rs offset        | If rs <=0 then branch       |

| 12  | BLTZ        | 000001 (1)  | 00000 (0)    | BLTZ rs offset        | If rs < 0 then branch       |

| 13  | BLTZAL      | 000001 (1)  | 10000 (16)   | BLTZAL rs offset      | If rs < 0 then procedure    |

| 14  | BNE         | 000101 (5)  | =            | BNE rs offset         | If rs != rt then branch     |

| 15  | J           | 000010 (2)  | -            | J Target              | rd= return_address          |

| 1.0 | TALD        | 000000 (0)  | 001001 (0)   | JALR rs               | .1                          |

| 16  | JALR        | 000000 (0)  | 001001 (9)   | JALR rd rs            | rd =return_address          |

| 17  | JR          | 000000 (0)  | 001000 (8)   | JR rs                 | PC = rs                     |

| 18  | LUI         | 001111 (15) | -            | LUI rt I              | rt = I                      |

| 19  | LW          | 100011 (35) | -            | LW rt offset (base)   | rt = memory [base + offset] |

| 20  | MFHI        | 000000 (0)  | 010000 (16)  | MFHI rd               | rd= HI                      |

| 21  | MFLO        | 000000 (0)  | 010010 (18)  | MFLO rd               | rd= LO                      |

| 22  | MTHI        | 000000 (0)  | 010001 (17)  | MTHI rs               | HI = rs                     |

| 23  | MTLO        | 000000 (0)  | 010011 (19)  | MTLO rs               | LO = rs                     |

| 24  | MULT        | 000000 (0)  | 011000 (24)  | MULT rs rt            | [LO, HI] = rs X rt          |

| 25  | MULTU       | 000000 (0)  | 011001 (25)  | MULTU rs rt           | [LO, HI] = rs X rt          |

| 26  | NOR         | 000000 (0)  | 100111 (39)  | NOR rd rs rt          | rd= rs NOR rt               |

| 27  | OR          | 000000 (0)  | 100101 (37)  | OR rd rs rt           | rd= rs OR rt                |

| 28  | ORI         | 001101 (13) | -            | ORI rt rs I           | rt = rs OR I                |

| 29  | SLL         | 000000 (0)  | 000000 (0)   | SLL rd rt sa          | $rd = rt \ll sa$            |

| 30  | SLLV        | 000000 (0)  | 000100 (4)   | SLLV rd rt rs         | $rd = rt \ll rs$            |

| 31  | SLT         | 000000 (0)  | 101010, (42) | SLT rd rs rt          | rd = rs < rt                |

| 32  | SLTI        | 001010 (10) | -            | SLTI rt rs I          | rt = rs < I                 |

| 33  | SLTIU       | 001011 (11) | -            | SLTIU rt rs I         | rt = rs < I                 |

| 34  | SLTU        | 000000 (0)  | 101011 (43)  | SLTU rd rs rt         | rd = rs < rt                |

|     | SRA         | 000000 (0)  | 000011 (3)   | SRA rd rt sa          | rd = rt >> sa               |

| 36  | SRAV        | 000000 (0)  | 000111 (7)   | SRAV rd rt rs         | rd = rt >> rs               |

|     | SRL         | 000000 (0)  | 000010 (2)   | SRL rd rt sa          | $rd = rt \gg sa$            |

| 38  | SRLV        | 000000 (0)  | 000110 (6)   | SRLV rd rt rs         | rd = rt >> rs               |

|     | SUB         | 000000 (0)  | 100010 (34)  | SUB rd rs rt          | rd= rs - rt                 |

|     | SUBU        | 000000 (0)  | 100011 (35)  | SUBU rd rs rt         | rd= rs - rt                 |

|     | SW          | 101011 (43) | -            | SW rt offset(base)    | Memory[base + offset]=rt    |

| 42  | SYSCALL     | 000000 (0)  | 001100 (12)  | SYSCALL               | System call                 |

| 43  | XOR         | 000000 (0)  | 100110 (38)  | XOR rd rs rt          | rd= rs XOR rt               |

| 44  | XORI        | 001110 (14) |              | XORI rt rs I          | rt = rs XOR I               |

| 45  | JAL         | 000011(3)   |              | JAL target            | rd=return_address           |

| 46  | LWCO        | 110000      |              | LWCO cs, offset(base) | cs=memory[base + offset]    |

| 47  | MFCO        | 10000       | 0            | MFCO rt, cs           | rt = cs                     |

| 48  | MTCO        | 10000       | 100          | MTC0 rt, cs           | cs = rt                     |

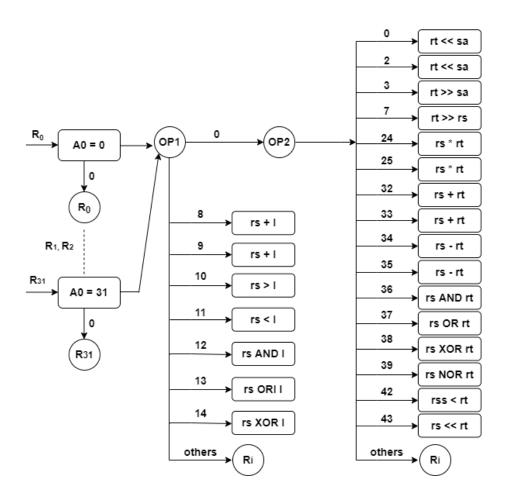

Using Table 2, an HLDD representing the behaviour of the system or the unit of the system under test can be created. From the table, it can be noted that OP1 and OP2 are control variables (which determines the path to be taken in the graph) and hence are non-terminal nodes in the HLDD. The combined states of OP1 and OP2 are however unique and will result in a terminal node defined by the instruction shown as ISA level operation.

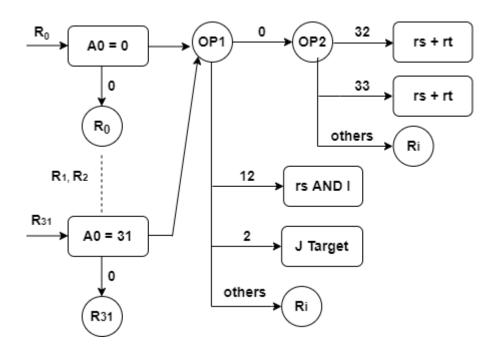

Figure 10 shows an HLDD of 4 instructions, ADD, ADDU, ANDI, and J. The values of OP1 and OP2 have been converted to their decimal values for simplification.

Figure 10: MiniMIPS HLDD model using 4 instruction sets

For the ADD instruction set, OP1 is 000000 and is shown in the diagram as the decimal value 0, likewise the OP2 is 100000 which is shown in the diagram as the decimal value 32. For the ADDU instruction, OP1 is 000000 and is shown in the diagram as the decimal value 0, likewise the OP2 is 100001 which is the decimal value 33. For the ANDI instruction, OP1 is 001100 shown as the decimal value 12 and for the J instruction, 000010 shown as the decimal value 2.

The system traverses to the ADD instruction when OP1 is 0 and OP2 is 32. Likewise, when OP1 is 0 and OP2 is 33 the system traverses to the ADDU terminal instruction. However, if OP1 is 12, then the system traverses to the AND instruction terminal and if OP1 is 2 then the system traverses to the J instruction terminal.

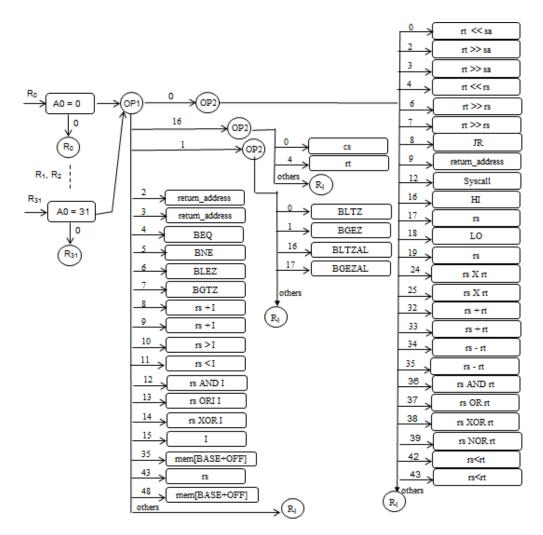

Figure 11 shows the complete HLDD representation of the miniMIPS instruction sets using the same concept.

Figure 11: Synthesis of HLDD for miniMIPS [9]

#### 3.1.3 Test Synthesis from HLDD

Using the HLDD graph model or the given processor, test generation can be performed. Test generation will result in a set of test patterns which can be used to test the structural entities of the processor [4]. The process of test generation involves traversing the graph by activating the nodes and consequently deriving a set of patterns. There are two types of nodes in the HLDD namely; control nodes and terminal nodes. The control nodes activate the path of the graph to a desired working mode or terminal node of the system. The terminal node contains nodes that activate the data path which can be used to test the different working modes of the processor.

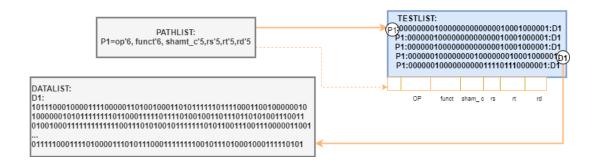

During test generation, three sets of patterns are generated, the pathlist, the datalist and the testlist. The pathlist holds the patterns (control nodes variables values) that lead to the

terminal nodes. The datalist holds the patterns which will be loaded in the register during the execution of the test program. These patterns activate the datapath within the terminal nodes. The testlist contains the list of test patterns generated by walking through all the nodes. These contains the pathlist and the datalist.

Figure 12 as seen in [4] shows an example of test generation from HLDD model for a miniMIPS ADD instruction.

Figure 12: Example of test generation

The testlist has the following syntax P#:test:D# where # is the placeholder for enumeration, P represents the pathlist, D represents the datalist, and test is the binary representation of the node values.

The pathlist has the following syntax P#name1'width1,...,namen'widthn, # is the place-holder for the index, name is the name of the node, and width is the size of the node.

The datalist has the following syntax D#: binary list, where # is the placeholder for the index and binary list is a list of numeric values. This is generated using the methods in [4].

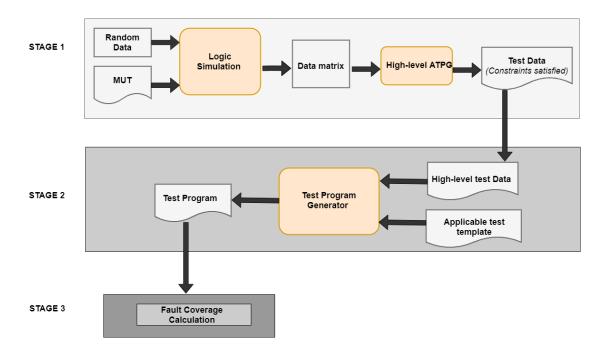

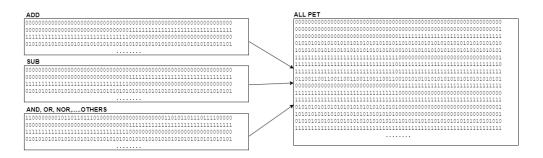

## 3.2 Test program generation with HLDD

The test program is an important part of SBST. It is divided into three stages. The first is the high-level test data generation, followed by the high-level test program generation and lastly, the fault coverage calculation. The visualization can be seen in Figure 13. High level test data generation was used to generate the control test data, and the pseudo-exhaustive data that were used in our experiments. High level test program generation was used with the test templates generated through HLDD synthesis in section 3.1.2.

Figure 13: High-Level test data and test program generation

#### 3.2.1 High Level Test Data Generation

Test generation is continually being improved every day in digital systems, as we are aware of technological advancements breeding new challenges in testing modern devices, we will like to discuss the complexities faced in test generation for microprocessors.

An essential quality in generating test in micro technologies is speed while focusing on faults two important data assignments is required giving rise to activation of the faults and the other for fault propagation [11], using some definitions relating to faults in microprocessors.

Test vectors are generated to imitate defects that may occur during the manufacturing process of chips, which may lead to the malfunctioning of the chips. Imitating physical defects means that the test vectors should be able to induce the faulty behaviour that matches the physical faults that may occur during the manufacturing process. The complexity of the system, the size of the tests to be taken and the factor of test quality are reasons why automatic test methods are used for generating test patterns for digital systems. In [1], the quality of a test is dependent on the test data, also the aim of any automatic test pattern generation (ATPG) is to produce efficient test patterns.

ATPG is the application of algorithmic based software for generating test vectors [12] and its need at the structural level is undisputed, because most, if not all the faults in a digital system has to be covered. In addition to the goal of producing efficient test patterns, ATPG aims to cover a high level of fault coverage during testing.

Test pattern generation algorithms can be accessed by the following indicators [13]

- Test effectiveness

- Fault coverage

- Length of the generated test

- Test generation time

In this thesis, the test data were generated using four basic methods (algorithms).

## 3.2.1.1 Method 1 – Conformity Test

**Control Test Patterns**— These are the test data patterns, generated to cover high-level functional fault model, and to be used by all instruction in the give processor (miniMIPS), so that the results of all instructions were distinguished pairwise in each bit of the data word. It is also known as **Conformity test**.

Test vectors are gotten from analysing the Circuit Under Test (CUT) and a specific type of fault is being targeted, followed by fault simulation. The targeted faults could be the defects that are in the structural part of a given CUT. After the test for the defects in the targeted area, and a fault is detected, fault simulation is carried out to find other faults that this generated test vector can detect [14]. The process of generating deterministic test patterns can be very extensive, and before fault simulation is carried out to detect other faults, the initial detected faults are noted.

Ideally, detecting all possible faults in a CUT is the aim of testing and we can conclude that detecting all possible faults in the CUT means 100% Fault Coverage (FC). Fault coverage is the percentage of fault that can be detected by the applied test vectors [15]. FC at 100% is desirable but is it not always reached in most tests due to some undetected faults. Undetected faults can also occur even when deterministic test patterns are being used.

#### **Generating Operands for Testing Control path**

As part of the HLDD fault model, two constraints were introduced for testing the control part of the MP in [23]. They are as follows:

$$\forall m^T \in M^T(m): [f(m^T) \neq \Omega)] \tag{1}$$

$$\forall m_i, m_j \in M^T(m), i \neq j: \forall k \left[ f_k(m_i) < (f_k(m_i) * f_k(m_j)) \right]$$

(2)

Where  $\Omega = ZERO$  or ONE and \* = logic OR or logic AND, both depending on the technology implemented in the MP [22] [23].

The label ZERO means the binary vector (000...0) while ONE means the binary vector (111...1). Representing the bit number of the data word is the index k.

The test operands used in the later for testing the control part has to satisfy constraints 1 and 2 (equation 1 and equation 2) stated above. In order to conform to these constraints, Algorithm 1 was developed. The algorithm generates the bits of the operands (data words) which are represented by  $D_1$  and  $D_2$ , starting from the LSB, bit by bit, unto the MSB. The essence for this is so that constraints 1 and 2 will be solved for all pairs of the functions  $f_k(m_i)$  and  $f_k(m_i)$  [24].

Algorithm 1: Test data generation for control part - RANDOM [25]

**Input**: Instruction set of the processor

Output: Sets of test operands OPi for each instruction, including a fault table D

**Notations**: n – represents the number of functions  $F_i$ ,

op – test operand,

OP – current set of selected random test operands,

$f_i(op)$  – result of the instructions  $I_i$  for the operand(s) op,

D – Fault table.

D<sub>ij</sub> – w-bit entry in D,

w – Length of the data word)

```

1. Initialize OP = \emptyset

2. Generate a set of random operands (R)

3. for i = 1, ...., n

4. Initialize OPi = \emptyset,

for j = 1, ...., n (j \neq i)

***operands for solving constraints fi,k < fj,k

Initialize Dij = 0

6.

7.

for all op \in R while Dij \neq 0

***adding new operands for covering Dij

8.

Dij(op) = fj(op) \land (fi(op) \oplus fj(op))

*** calculating fault coverage for op

9.

if (Dij (op) V Dij) \bigoplus Dij \neq 0 then

*** check for the coverage increment

10.

begin

11.

Dij = Dij V Dij(op)

*** update of the coverage vector

12.

include op into OPi

*** new operand is selected

13.

end

14.

endfor op

15.

endfor j

16. endfor i

```

This Algorithm 1 will produce a set of operands for every instruction in the MP and a fault table that satisfies the constraint  $f_{i,k} < f_{j,k}$ .  $D^k_{ij} = I$  if the constraint is satisfied, and is covered by a minimum of one operand, otherwise  $D^k_{ij} = 0$ . Finally, the percentage of 1s in D is the high-level functional fault coverage for the test for control path [25].

Algorithm 1 is called RANDOM. This is because for each step of line 7, the random operand that came first (op  $\in$  R) will be selected with a goal of increasing the fault coverage. Another algorithm called GREEDY was established in order to reduce the test length.

The difference between the GREEDY algorithm and RANDOM is that at line 7, where the best operand is being searched for maximum fault coverage, the subsequent operand is selected and the algorithm proceeds with the search until target  $D^{k}_{ij} = 1$  is reached or no further operands can satisfy the constraint  $f_{i,k} < f_{j,k}$ .

It is notable that the constraint  $f_{i,k} < f_{j,k}$  may not be solved if the related functional fault is redundant, or the search spare R is not large enough [25].

According to [2], Conformity test is a test for a non-terminal node of the HLDD, and its goal is to test the control part of the microprocessor. The conformity test is generally generated according to constraints 1 and 2 that were set up for testing non-terminal nodes.

#### • Generating Conformity Test Program for Control part of Microprocessor

The generation of conformity test for the control part of the microprocessor was developed in [4] and [6]. According to [4] and [6], conformity test was explained as such:

Consider an HLDD  $G^Y = (M, \Gamma, X)$  with Y = F(X) as a functional model of the instruction set of a given MP.

$X = C \cup D$  (which represents the instruction format of the MP)

Y = destination data

C = opcode of the instruction format, and is divided into sub-fields  $C_k \in C$

D = source data of the instruction format and is divided into  $D_k \in D$ .

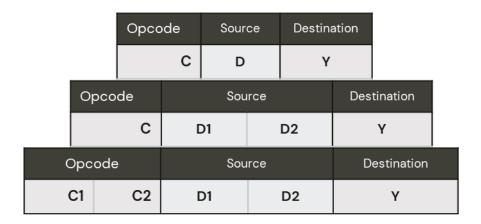

It is notable that the source and destination data variables may refer directly to the registers of may refer to the addressable memory locations. Examples of mapping between instruction formats and the HLDD functional variables are illustrated for three instruction formats below:

- I. Instruction format with 1 opcode subfield (C), 1 source subfield (D) and one destination subfield (Y).

- II. Instruction format with 1 opcode subfields, 2 source subfields (D1 and D2) and one destination subfield (Y).

- III. Instruction format with 2 opcode subfields (C1 and C2), 2 source subfields (D1 and D2) and one destination subfield (Y).

Figure 14: Mapping of miniMIPS instruction formats and the HLDD functional variable

The main targets of the conformity tests are not the instructions as a whole, as per the instruction format, and it involves both the control and data functions. This depicts that if the opcode C is divided into subfields  $C_k \in C$ , then the control tests will target all the subfield one after the other. To test if all the sub-functions that relates to  $C_k$  were rightly selected, the node m in the HLDD module test T(m) for all the values of  $x(m) \in V(x(m))$  has to be tested.

In [4], generating a test instruction for testing a fault  $r \in R$  (m, v), it is essential to find a test pattern Xt which activates a path  $l(m_0, m^{T,v})$  from the root node  $m_0 \in M^N$  to a terminal node  $m^{T,v} \in M^T$ , so that x(m) = v, and  $m \in l(m_0, m^{T,v})$ ; the pattern  $X^t$  corresponds to a full opcode C of instruction, which includes the needed value of  $C_k$ . It is also essential to complete the pattern  $X^t$  by generating the test data D, so that the constraints 1 was satisfied. The result for generating a test instruction for testing the fault model  $R(m,v) \subset R(m)$  includes a control pattern (instruction) C(m,v), and a set of data pattern D(m,v).

The algorithm for conformity test program according to [4] is:

```

for all m ∈ M do

for all v ∈ V (x(m)) do

for all r do

execute C(m,v).D(m,v,r)

end for

end for

end for

```

Figure 15: Algorithm for conformity test

#### • Explanation of the algorithm for conformity test

In line 1,  $m \in M^N$  represents the nonterminal nodes, and line 1 is testing  $T(M^N)$  for the fault model R. Lines 2-5, firstly initializes all registers involved in operations  $f(m^{Tv})$  at every terminal nodes  $m^{Tv} \in M^T(m) \subseteq M^T$  with values satisfying *constraints* 2. Secondly, it executes the instruction that assigns the value or v to x(m), activates a path that leads to node m in  $G_Y$ , and the paths that transits from m to  $m^{T, v} \in M^T(m)$ ; Thirdly, the algorithm observes the value of Y.

Line 6 ends the testing for nonterminal node m  $\in M^N$  and line 7 ends the conformity test of the HLDD  $G^Y$ .

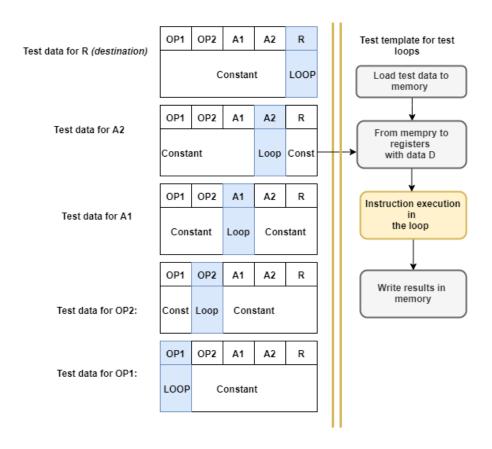

The conformity test is used to generate a template that will be used with the control test patterns. The functional variables in this test loops through all the instructions, while the other variables remain constants [9]. A test template was created for the conformity test as seen in Figure 16.

Figure 16: Structure of Conformity test

In Figure 16, OP1, OP2, A1, A2 and R serves as the control nodes (non-terminal nodes). Each of them has a test template that consists of instructions that leads to the path of a particular node. The test program that will be generated also consists of these instructions, which will be used test the control nodes. However, the control test data generated in with Algorithm 1 that satisfy the constraint 1 and 2 will be passed into the test program as described in Figure 13.

#### 3.2.1.2 Method 2 – Short Scanning Test

**Dedicated PET** – this is the pseudo-exhaustive test data for testing each instruction with so called dedicated data, generated separately for each instruction based on its functionality, and to guarantee exhaustive test of each bit of the data word. It is also known as the **Short scanning test**.

For understanding the concept of pseudo-exhaustive test pattern, the concept of exhaustive test pattern should be understood.

#### **Exhaustive Test Pattern**

Exhaustive test patterns detect all the possible faults, either gate-level SAF faults, wired AND/OR faults, and bridging faults in a combinational circuit. A combinational CUT with N-input, exhaustive testing will require applying 2N exhaustive patterns [16]. This approach will not detect all possible transistor-level faults or delay faults because these kinds of faults needs a specific order at which the vectors needs to be arranged, if possible, the potential to repeat certain test vectors within the vector set [12]. If a combinational circuit has few primary inputs, exhaustive testing may be a viable option, where every possible input vector is considered [17]. However, in circuits with large amount of primary inputs, exhaustive testing might not be the viable approach. Due to this drawback, pseudo-exhaustive test makes it possible to partition the circuit and only exhaust the input vectors within each cone for each primary output [17].

**Pseudo-Exhaustive Patterns** alternatively, have lesser number of test patterns [18]. As stated above, the circuit is partitioned and is exhaustively tested. This means that a better FC is achieved. In [17], a circuit with three primary inputs n1, n2, and n3, with a

corresponding primary output cone each will have a total number of  $2^{n1} + 2^{n2} + 2^{n3}$  pseudo-exhaustive vectors at most.

## **Generating Operands for Testing the Data Path**

A significance of pseudo-exhaustive data is that remaining test generation procedure will not depend on the implementation details of the processor cores under test [25]. Ideally, logic operations are independent in all bits, hereby enabling the operations in all bits to be tested independently. In cases of unary operations, two exhaustive patterns will be enough, while for logic operations, we need to use four exhaustive patterns  $\{(0,0), (0,1), (1,0), (1,1)\}$  per bit [24].

Table 3: Generation of PET data for adder [25]

| No | <br>4-bit | 3-bit         | 2-bit         | 1-bit         | 0-bit         |

|----|-----------|---------------|---------------|---------------|---------------|

|    | a4 b4 c4  | $a_3 b_3 c_3$ | $a_2 b_2 c_2$ | $a_1 b_1 c_1$ | $a_0 b_0 c_0$ |

| 1  | <br>000   | 000           | 000           | 000           | 000           |

| 2  | <br>010   | 010           | 010           | 010           | 0 0 1         |

| 3  | <br>100   | 100           | 100           | 100           | 110           |

| 4  | <br>110   | 0 0 1         | 110           | 0 0 1         | 011           |

| 5  | <br>0 0 1 | 110           | 001           | 110           | 100           |

| 6  | <br>011   | 011           | 011           | 011           | 101           |

| 7  | <br>101   | 101           | 101           | 101           | 110           |

| 8  | <br>1 1 1 | 111           | 111           | 111           | 111           |

Table 4: Generation of PET data for Subtractor [25]

| No | • • • • | 4-bit    | 3-bit         | 2-bit         | 1-bit         | 0-bit         |

|----|---------|----------|---------------|---------------|---------------|---------------|

|    |         | a4 b4 c4 | $a_3 b_3 c_3$ | $a_2 b_2 c_2$ | $a_1 b_1 c_1$ | $a_0 b_0 c_0$ |

| 1  |         | 000      | 000           | 000           | 000           | 000           |

| 2  |         | 110      | 011           | 110           | 011           | 0 0 1         |

| 3  |         | 0 0 1    | 100           | 0 0 1         | 100           | 010           |

| 4  |         | 100      | 110           | 100           | 110           | 011           |

| 5  |         | 011      | 0 0 1         | 011           | 0 0 1         | 100           |

| 6  |         | 101      | 101           | 101           | 101           | 101           |

| 7  |         | 010      | 010           | 010           | 010           | 110           |

| 8  |         | 111      | 111           | 111           | 111           | 111           |

In Table 3 and Table 4 above, ripple-carry is used for generating the PET data for addition and ripple-carry is implemented for generating the PET data for subtraction. ADD and SUB stands as operators in the miniMIPS ISA and the data generated are dedicated for these operators. The same applies to other operators used in our experiment – AND, XOR,

SLL, SRL, etc. To cover every combinations of the input operands  $a_0$ ,  $b_0$  and  $c_0$  of each bit of the adder, 8 pairs of data were needed, as seen in Table 3 and Table 4.  $C_0$  may be the carry bit in the case of addition, or the borrow bit in the case of subtraction. PET patterns are generated from the LSB, after calculating the carry for the  $c_n$  for the next bit, and the right values which will fit into the operands  $a_n$  and  $b_n$ . Through this previous step, all pseudo-exhaustive combinations for the bit section would be achieved [25]. Additionally, the columns titled "2-bit" and "1-bit" can be copy pasted for the next two-bit-pairs to the right [24].

**Scanning Test Definition**: According to [4], Scanning test is a test for a terminal node of the HLDD, and its goal is to test the data path of the microprocessor. It focuses on testing the correctness of the terminal nodes in the HLDD by making use of the same instruction with different test data.

#### Generating Scanning Test for the Data Path of MP

The generation of scanning test for the data path of the microprocessor was developed in [4] and [6]. According to [4] and [6], scanning test was explained as such:

Consider an HLDD  $G^Y = (M, \Gamma, X)$  with Y = F(X) as a functional model of the instruction set of a given MP.

$X = C \cup D$  (which represents the instruction format of the MP)

Y = destination data

C = opcode of the instruction format, and is divided into sub-fields  $C_k \in C$

D = source data of the instruction format and is divided into  $D_k \in D$ .

D and Y could be the address of a register or the address of a memory location. The source D could also be an immediate data which could be part of the miniMIPS instruction format.

The source and destination data variables may be the address of the registers, or to the addressable memory locations. The immediate data which will be part of the instruction format, may be represented by the source variable.

A test will be generated for every terminal nodes  $m^T \in M^T \subset M$  in each HLDD  $G^Y = \{G\}$ ,  $Y \in U$  (|U| = number of HLDDs), for the purpose of testing the complete data path of the provided microprocessor which consists of various HLDDs.

In [4], the term of data functional fault model (DFFM) of the HLDD  $G^Y$  was introduced. It is denoted as  $R(m^T)$  and a union of all functional fault models in the terminal nodes  $m^T \in M^T \subset M$ , and it represents the working nodes of the microprocessor  $Y = f(m^T)$ . Each functional fault  $r \in R(m^T)$  is similar to the conditional SAF model developed for gate-level testing [7].

In order to test the faults  $r \in R(m^T)$ , we need to execute a test using the set of instruction of the microprocessor.

$$T(mT) i= \{C(m^T). D(m^T, r)\}$$

In the test above,  $C(m^T)$  = Instruction code and it remains constant

D  $(m^T, r)$  = Data. It is dynamic with the values from the set of constraints  $R(m^T)$ .

The general point of the scanning test is to reiterate the same instruction with data fetched by scanning a given data array.

Figure 17: Structure of Scanning Test

In the figure above, all the registers are loaded with the data fetched from the array, the instructions that activates in the HLDD are activated and in a loop, lastly, the result of each operation is written into memory.

The algorithm for scanning test according to [4] is:

```

for all m ∈ M<sup>N</sup> do

for all r do

execute C(m<sup>T</sup>).D(m<sup>T</sup>, r)

end for

end for

```

Figure 18: Algorithm for scanning test

#### **Explanation of the algorithm for Scanning Test**

In line 1,  $m^T \in M^N$  represents the nonterminal nodes, and line 1 is testing  $T(M^N)$  for the fault model R. Lines 2-3, firstly initializes all registers involved in the function  $f(m^{Tv})$  at every terminal nodes  $m^{Tv} \in M^T$  with the test data d. Secondly, it implements the instruction that activates in  $G_Y$  a path to the node m in  $M^T$ . Thirdly, the algorithm observes the value of Y.

Line 4 ends the testing for terminal node  $m \in M^N$  and line 5 ends the scanning test of the HLDD  $G_Y$ .

The scanning test described in this section is called short scanning test.

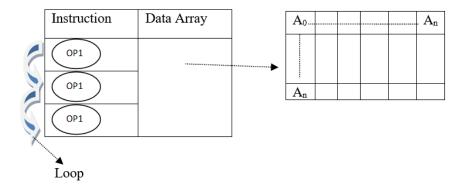

#### 3.2.1.3 Method 3 – Long Scanning Test

**All PET Test Patterns** — These are the pseudorandom test data for testing each instruction with a sum of all test patterns generated pseudo-exhaustively for the data part. It uses the combination of all the dedicated PET data to test for each instruction based on its functionality. It can be referred to as Long scanning test.

All PET represents combination of the all the PET data generated through scanning test in section 3.2.1.2. For our experiment in chapter 5, 9 patterns were dedicated for the ADD and SUB instructions, 4 patterns for the logic instructions AND, OR, XOR and NOR, while 2 different sets of patterns were dedicated for the shift, load and branch instructions. Lastly, a total of 310 patterns were dedicated for the MULT instruction.

In [26], a method to transform the "paper and pencil" 2-dimensional ILA of n-bit array into a set of (n-1) 1-dimensional ILAs of n cells, which can be tested pseudo-exhaustively nearly as easily as ripple-carry adders. In order for such modification to occur, the concept of data-controlled segmentation of the circuit was introduced.

Figure 19: PET combination to All PET Test Patterns

#### 3.2.1.4 Method 4 – Random Test

Random Test Patterns: Random test patterns are very easy to generate via Random Test Generation (RTG). Unlike deterministic and pseudo-exhaustive test patterns, no specific faults are targeted for the random test generation. Additionally, exhaustive test may be superior to RTG because RTG can produce duplicated vectors and may miss certain ones [17]. RTG stands out because it is easy to generate the random vectors, it does not satisfy any constraints and the complexity is low. However, the detrimental effect of random test patterns is that it can detect a set of faults that is up to 10 times larger than a deterministic test patterns for the same set of faults [12]. Due to this, determining the quality of a test set becomes difficult, because conventional methods based on fault simulation becomes costly [19]. In [20], some of the disadvantages of random test generation is that it can have very long test application time, love coverage, area overhead and additional delay.

RTG makes it possible for the random vectors to be evenly distributed in the pattern set. This means that the random patterns will eventually have equal numbers of logic 1s and 0s in the set as a whole. The method used to generate the random patterns for the experiments carried out in this thesis is not totally random. A pseudo-random number was used so that the random patterns can remain the same in cases where they need to be regenerated. For RTG, we cannot totally be confident in the kind of result or FC, we can

only be certain that the random patterns used in a test will detect all possible Single Stuck Fault (SSF) [12].

Similar to line 2 of Algorithm 1, a fewer set of random data is generated with a python script and loaded directly as a high-level test data into the test program generator, alongside the test templates, as illustrated in Figure 13. It is notable to mention that the randomly generated patterns do not satisfy any constraints as compared to the control test patterns.

### 3.3 Test program generation

As discussed in section 3.1.2, the test program is generated from the HLDD synthesis. The synthesis is implemented through prepared test code templates, used in generating the test program. As miniMIPS is a processor with 32-bits registers, the initial target of the test template is to reset all the 31 registers in Figure 7, to make sure that the current test program is not affected by the previously generated program with a different data in the registers. After the registers are set to null, the test data is loaded into the memory. The test data could be the control, PET, All PET or random test data. The final process is the generation of the test program based on the conformity test template or scanning test template or random data test program. Section 4.1 will provide a more elaborate explanation on the test template creation.

Figure 20: Test Program Generation process with four templates

#### 3.4 Fault simulation

The fault simulation is the final stage of the automated SBST. It comprises two fault simulators:

- 1. "Home-made" high-level fault simulator for measuring the quality of conformity test, whereas the PET-based scanning test by definition is considered a full (100%) high-level test.