TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 17/2019

# Scenario Oriented Model-Based Testing

EVELIN HALLING

TALLINN UNIVERSITY OF TECHNOLOGY Faculty of Information Technologies Department of Software Science

The dissertation was accepted for the defence of the degree of Doctor of Philosophy in Informatics on April 2, 2019.

| Supervisor: | Professor Jüri Vain                 |

|-------------|-------------------------------------|

|             | Department of Software Science      |

|             | Faculty of Information Technologies |

|             | Tallinn University of Technology    |

|             | Tallinn, Estonia                    |

|             |                                     |

**Opponents:**

Dragos Truscan, PhD Åbo Akademi University Turku, Finland

Anatoliy Gorbenko, PhD Leeds Beckett University Leeds, United Kingdom

Defence of the thesis: May 10, 2019, Tallinn

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for any academic degree elsewhere.

**Evelin Halling**

signature

Copyright: Evelin Halling, 2019 ISSN 2585-6898 (publication) ISBN 978-9949-83-416-7 (publication) ISSN 2585-6901 (PDF) ISBN 978-9949-83-417-4 (PDF) TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 17/2019

# Stsenaariumjuhitud mudelipõhine testimine

**EVELIN HALLING**

# Contents

| List of Publications 9 |        |                                                                        | 9               |

|------------------------|--------|------------------------------------------------------------------------|-----------------|

| Aut                    | thor's | s Contributions to the Publications                                    | 10              |

| Ove                    | erviev | w                                                                      | 12              |

| Ab                     | brevia | ations                                                                 | 12              |

| 1                      | INTR   | ODUCTION                                                               | 13              |

|                        | 1.1    | Motivation                                                             | 13              |

|                        | 1.2    | The scope of the thesis                                                | 14              |

|                        |        | 1.2.1 The application domain perspective                               | 14              |

|                        |        | 1.2.2 The testing technology perspective (to meet the requirements) .  | 15              |

|                        |        | 1.2.3 Formal modelling perspective                                     | 17              |

|                        | 1.3    | Related work                                                           | 18              |

|                        | 1.4    | Main hypothesis and goals                                              | 20              |

|                        | 1.5    | The methodology used in the thesis                                     | 21              |

|                        | 1.6    | Thesis main contributions                                              | 21              |

|                        | 1.7    | Chapter summary                                                        | 22              |

| 2                      | PRFI   | IMINARIES                                                              | 23              |

| -                      | 2.1    | Model-based testing                                                    | 23              |

|                        | 2.2    | Uppaal timed automata                                                  | 24              |

|                        | 2.3    | Conformance testing with Uppaal TA                                     | 27              |

|                        | 2.4    | Test coverage criteria                                                 | 28              |

|                        | 2.5    | Chapter summary                                                        | 30              |

| -                      |        |                                                                        |                 |

| 3                      |        |                                                                        | 31              |

|                        | 3.1    | The Correctness of SUT Models                                          | 31              |

|                        |        | <ul> <li>3.1.1 Modelling Timing Aspects of SUT</li></ul>               | 31<br>33        |

|                        |        | 3.1.2 Connected Control Structure and Output Observability             | 33<br>33        |

|                        |        | 3.1.2.2 Input Enabledness.                                             | 33              |

|                        |        | 3.1.2.3 Strong Responsiveness                                          | 34              |

|                        | 3.2    | Correctness of RPT Tests                                               | 34              |

|                        |        | 3.2.1 Functional Correctness of Tests                                  | 34              |

|                        |        | 3.2.2 Invariance of Tests with Respect to Changing Time Constraints of |                 |

|                        |        | SUT                                                                    | 35              |

|                        | 3.3    | Correctness of test deployment                                         | 37              |

|                        | 3.4    | Chapter summary                                                        | 37              |

| 4                      | тест   | PURPOSE SPECIFICATION LANGUAGE                                         | 39              |

| 4                      | 4.1    | Overview of the test purpose specification language                    | <b>37</b><br>39 |

|                        | 4.2    | $TDL^{TP}$ syntax                                                      | 39              |

|                        | 4.3    | $TDL^{TP}$ semantics                                                   | 40              |

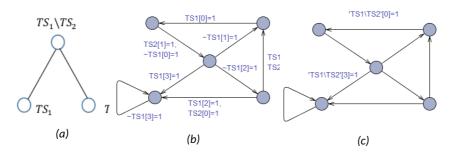

|                        |        | 4.3.1 Atomic labelling function                                        | 41              |

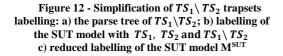

|                        |        | 4.3.2 Derived labelling operations (trapset operations)                | 41              |

|                        |        | 4.3.3 Interpretation of $TDL^{TP}$ expressions                         | 42              |

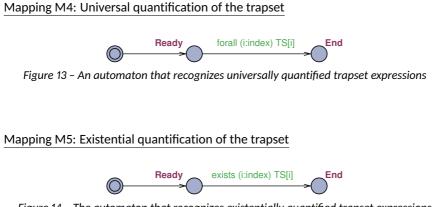

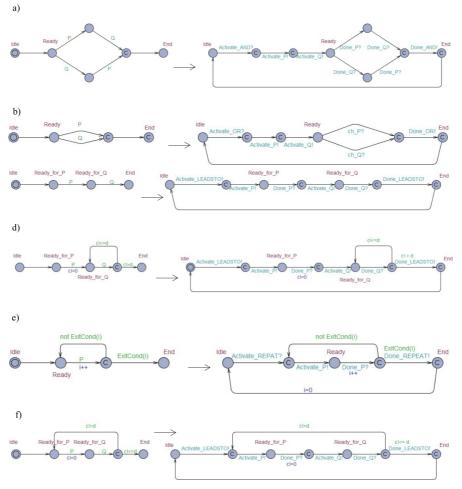

|                        | 4.4    | Mapping $TDL^{TP}$ expressions to behavior recognizing automata        | 43              |

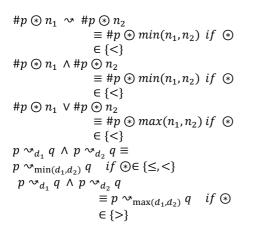

|                                            |                                             | 4.4.1  | Mapping $TDL^{TP}$ trapset expressions to SUT model $M^{SUT}$ labelling | 43  |  |

|--------------------------------------------|---------------------------------------------|--------|-------------------------------------------------------------------------|-----|--|

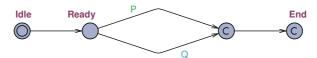

|                                            |                                             | 4.4.2  | Mapping $TDL^{TP}$ logic operators to recognizing automata              | 45  |  |

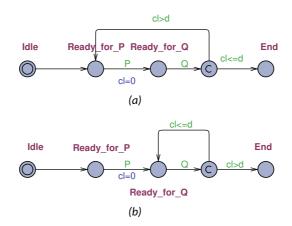

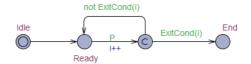

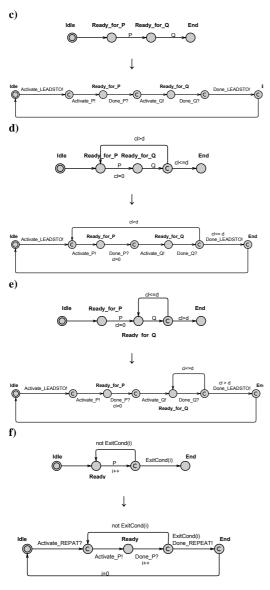

|                                            |                                             | 4.4.3  | Mapping $TDL^{TP}$ temporal operators to recognizing automata           | 46  |  |

|                                            | 4.5                                         | Reduct | tion of the supervisor automata and the labelling of SUT                | 47  |  |

|                                            | 4.6                                         | Compo  | osing the test supervisor model                                         | 48  |  |

|                                            | 4.7                                         | Encodi | ng the test verdict and test diagnostics in the tester model            | 49  |  |

|                                            | 4.8                                         | Chapte | er summary                                                              | 51  |  |

|                                            |                                             |        |                                                                         |     |  |

| 5                                          |                                             | STUDY  |                                                                         | 52  |  |

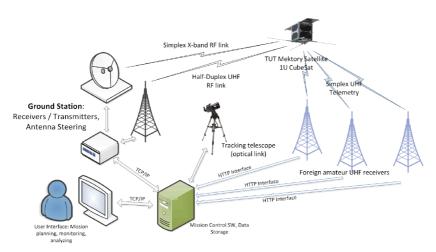

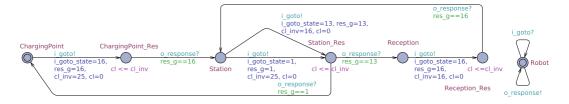

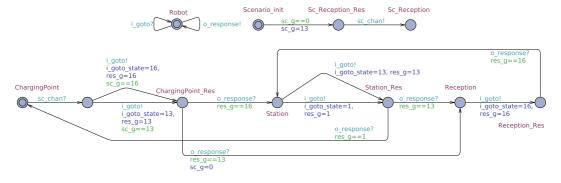

|                                            | 5.1                                         |        | description                                                             | 52  |  |

|                                            |                                             | 5.1.1  | Ground Segment                                                          | 53  |  |

|                                            |                                             | 5.1.2  | Space Segment                                                           | 53  |  |

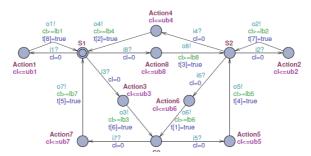

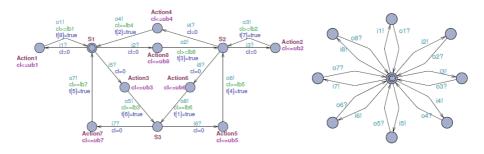

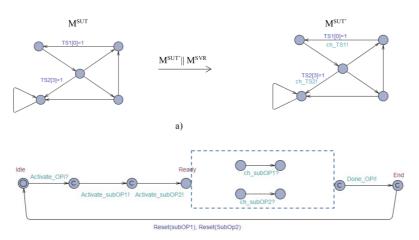

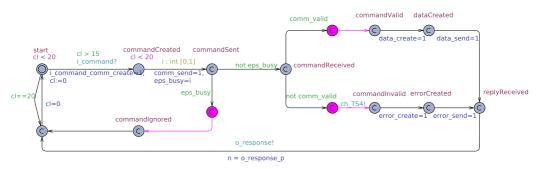

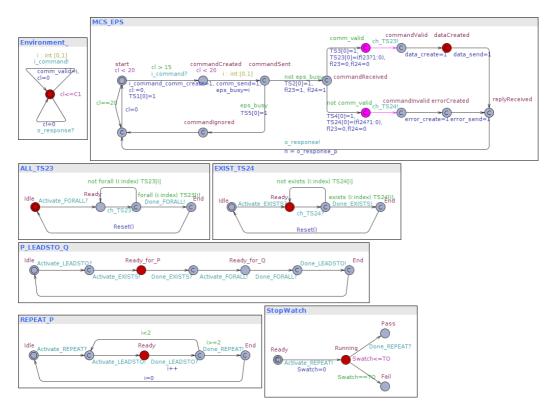

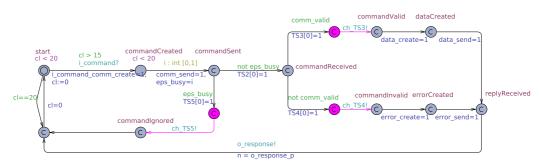

|                                            | 5.2                                         | •      | under test modelling                                                    | 54  |  |

|                                            | 5.3                                         |        | se 1                                                                    | 54  |  |

|                                            |                                             | 5.3.1  | Test purpose specification                                              | 54  |  |

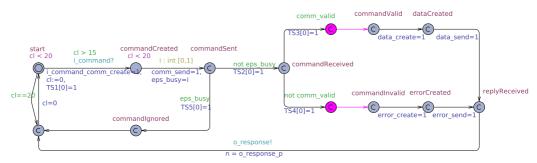

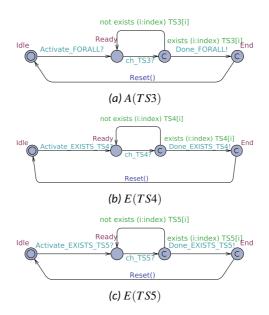

|                                            |                                             | 5.3.2  | Labelling of $M^{SUT}$                                                  | 54  |  |

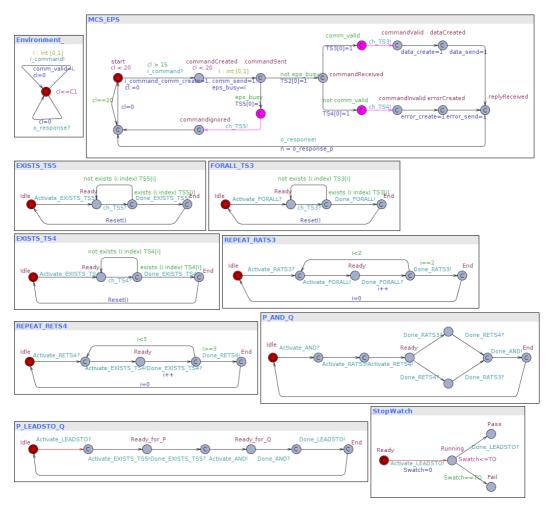

|                                            |                                             | 5.3.3  | Test model construction                                                 | 55  |  |

|                                            |                                             | 5.3.4  | Generating test sequences                                               | 56  |  |

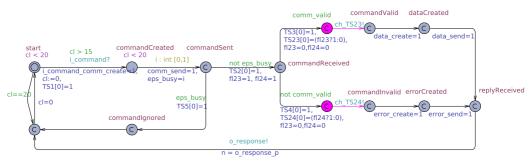

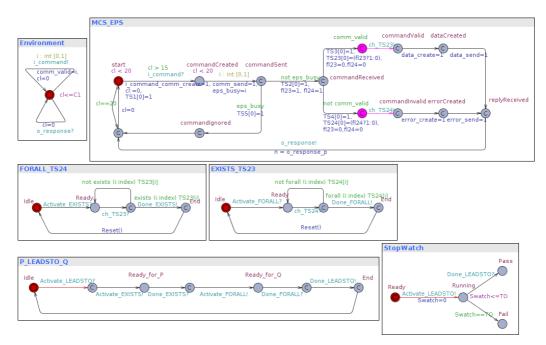

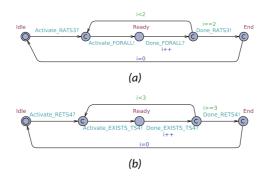

|                                            | 5.4                                         |        | se 2                                                                    | 56  |  |

|                                            |                                             | 5.4.1  | Test model construction                                                 | 57  |  |

|                                            |                                             | 5.4.2  | Generating test sequences                                               | 57  |  |

|                                            | 5.5                                         |        | se 3                                                                    | 58  |  |

|                                            |                                             | 5.5.1  | Test model construction                                                 | 58  |  |

|                                            | - <i>(</i>                                  | 5.5.2  | Generating test sequences                                               | 58  |  |

|                                            | 5.6                                         | Chapte | er summary                                                              | 58  |  |

| со                                         | NCLU                                        | SIONS  |                                                                         | 67  |  |

| List of Figures 71                         |                                             |        |                                                                         |     |  |

| Re                                         | References 72                               |        |                                                                         |     |  |

| Acknowledgements 77                        |                                             |        |                                                                         |     |  |

|                                            |                                             |        |                                                                         | 78  |  |

|                                            |                                             |        |                                                                         | 81  |  |

|                                            |                                             |        |                                                                         | 85  |  |

|                                            |                                             |        |                                                                         |     |  |

| Appendix 2 - Testcase 2 test sequence   93 |                                             |        |                                                                         |     |  |

| -                                          | Appendix 3 - Testcase 3 test sequence   105 |        |                                                                         |     |  |

| -                                          | Appendix 4 - Publication I123123            |        |                                                                         |     |  |

| -                                          | Appendix 5 - Publication II 13              |        |                                                                         | 139 |  |

| Ар                                         | Appendix 6 - Publication III 15             |        |                                                                         | 155 |  |

| Ар                                         | Appendix 7 - Publication IV 165             |        |                                                                         |     |  |

| Appendix 8 - Publication V | 181 |

|----------------------------|-----|

| Curriculum Vitae           | 197 |

| Elulookirjeldus            | 199 |

# **List of Publications**

- Publication I: E. Halling, J. Vain, A. Boyarchuk, and O. Illiashenko. Test scenario specification language for model-based testing. *International Journal of Computing*, 2019

- Publication II: J. Vain, A. Anier, and E. Halling. Provably correct test development for timed systems. In H. Haav, A. Kalja, and T. Robal, editors, *Databases and Information Systems* VIII Selected Papers from the Eleventh International Baltic Conference, DB&IS 2014, 8-11 June 2014, Tallinn, Estonia, volume 270 of Frontiers in Artificial Intelligence and Applications, pages 289–302. IOS Press, 2014

- Publication III: J. P. Ernits, E. Halling, G. Kanter, and J. Vain. Model-based integration testing of ROS packages: A mobile robot case study. In 2015 European Conference on Mobile Robots, ECMR 2015, Lincoln, United Kingdom, September 2-4, 2015, pages 1–7. IEEE, 2015

- Publication IV: J. Vain, E. Halling, G. Kanter, A. Anier, and D. Pal. Model-based testing of real-time distributed systems. In G. Arnicans, V. Arnicane, J. Borzovs, and L. Niedrite, editors, Databases and Information Systems - 12th International Baltic Conference, DB&IS 2016, Riga, Latvia, July 4-6, 2016, Proceedings, volume 615 of Communications in Computer and Information Science, pages 272–286. Springer, 2016

- **Publication V:** J. Vain and E. Halling. Constraint-based testing scenario description language. Proceedings of 13th Biennial Baltic Electronics Conference, BEC 2012, IEEE: 89–92, 2012

## Author's Contributions to the Publications

- I In Publication I, I was the main author, carried out the simulations and the analysis of the results, prepared the figures, and wrote the manuscript.

- **II** In Publication II, I conducted the experiments and simulations, analysed the results, prepared the figures, and wrote the manuscript.

- **III** In Publication III, I conducted the experiments and simulations, analysed the results, prepared the figures, and wrote the manuscript.

- **IV** In Publication IV, I prepared the example models and conducted validation experiments.

- **V** In Publication V, I conducted the experiments and simulations, prepared the figures, and wrote the manuscript.

# Overview

In this thesis, the research is focused on model-based testing, specifically, on the test purpose specification and test generation techniques to address the test coverage and faults back-traceability problems.

The structure of the thesis is the following:

- Chapter 1 gives the motivation why this research is needed in the critical systems software engineering practice, defines the research problems to be solved and their scope, outlines the related work, and introduces the methodology, problem specific hypothesis and goals to be addressed in the thesis.

- Chapter 2 presents the theoretical and methodological preliminaries the results of the thesis are built upon. The foundations of the thesis are model-based conformance testing theory, Uppaal timed automata and TCTL model checking theory.

- Chapter 3 introduces the provably correct test development workflow and verification conditions necessary to assure the correctness of development increments. The test purpose descriptions and test generation correctness are verified with respect to these conditions.

- Chapter 4 defines the test purpose specification language *TDL*<sup>*TP*</sup>, its syntax and semantics.

- In Chapter 5, the practical usability of the test purpose specification language  $TDL^{TP}$  and provably correct test development method are validated on the TUT100 satellite software case study.

The results of the thesis are concluded and future research perspectives outlined in the thesis conclusion.

# Abbreviations

| CCDL    | Check Case Definition Language                 |

|---------|------------------------------------------------|

| CPS     | Cyber/Physical Systems                         |

| DTRON   | Distributed Testing Realtime systems Online    |

| EFSM    | Extended Finite State Machine                  |

| IOCO    | Input-Output Conformance Relation              |

| IOTS    | Input-Output Transition System                 |

| ISO     | International Organization for Standardization |

| ITU     | International Telecommunication Union          |

| IUT     | Implementation Under Test                      |

| LEOP    | Launch and Early Orbit Phase                   |

| LTL     | Linear Temporal Logic                          |

| LTS     | Labelled Transition System                     |

| MBT     | Model-Based Testing                            |

| MCS     | Mission Critical Systems                       |

| MSC     | Message Sequence Chart                         |

| NTA     | Network of Timed Automata                      |

| OTX     | Open Text Sequence Exchange Format             |

| RPT     | Reactive Planning Tester                       |

| RT-IOCO | Real-time Input-Output Conformance Relation    |

| SUT     | System Under Test                              |

| SysML   | Systems Modelling Language                     |

| TA      | Timed Automata                                 |

| TCTL    | Timed Computation Tree Logic                   |

| TCS     | Time Critical Systems                          |

| TDL     | Test Description Language                      |

| TIOTS   | Timed Input-Output Transition System           |

| TLTS    | Timed Labelled Transition System               |

| TPLan   | Test Purpose Language                          |

| UML     | Unified Modelling Language                     |

| V&V     | Verification and Validation                    |

## **1 INTRODUCTION**

In this chapter the motivation for studying novel methods of model-based testing is given. The scope of the thesis is determined from three perspectives: application domain, testing technology, and formal framework for test purpose specification, test generation and execution. The goal and main results of the thesis are positioned with respect to the related work of other authors in the field. The chapter concludes by outlining the main hypothesis, methodology, and contribution of the thesis.

## 1.1 Motivation

*Mission Critical Systems*<sup>1</sup> (MCS) are systems whose failure might cause catastrophic consequences, such as someone dying, damage to property, severe financial losses, damage to national security and others. There are several well-known failure cases, such as TheracTwentyFive<sup>2</sup> radiation therapy machine malfunctioning caused by undetected software fault, namely race condition. Six known accidents have been listed due to the overdose, several of them fatal. Similarly, Patriot Missile Failure caused by software error in the system's clock, resulted in an accumulated clock drift that led to the improper reaction to Scud attack and death of twenty eight soldiers and over hundred other casualties. Mars Climate Orbiter Crash (NASA lost \$125-million) was caused by misinterpreted requirements in software implementation, namely, the thrust impulse command for the thrusters was produced in imperial units, instead of metric units.

In these and many other examples the mission criticality is mixed also with time criticality. The *Time Critical Systems*<sup>3</sup> (TCS) fail if the timing deadlines are not met by the system. So, a well-designed MCS, even in case of unavoidable system's failures, if properly predicted, timely detected and recovered, should be able to operate under severe exploitation conditions without catastrophic consequences.

Detection of software bugs, especially those deeply nested in software loops which manifest sporadically as wrong timing in complex TCS, is a real challenge for current MCS and TCS software engineering methods. The methods of risk mitigation, in particular the provably correct software synthesis, formal verification as well as model-based testing, are powerful but time-wise and computationally expensive which limits their wider application. In [26], it is stated that software verification and testing constitutes up to 50 percent (or even more in mission critical applications) of the total development costs of software.

Authors of [34] report that the root causes of 56 percent of all defects identified in software projects are introduced in the requirements phase. They profess that low software quality is mainly due to the *problematical test coverage and incorrect requirements*. In addition, 50 percent of incorrect requirements are caused by incomplete specification and another 50 percent by *unclear* and *ambiguous* requirements.

Another research report [5] outlines the application domains and development phases with highest risk of failure or delay. In *automotive* and *medical* domain the *system integration level test and verification* cause project delays respectively in 63 percent and in 66,7 percent of the cases. An extreme is the medical domain where system's *middleware development and test* has caused delays in about 75 percent of studied cases. Since both automotive and medical domains are often mission and time critical it gives indication that *the software integration level test* and *verification are the main bottlenecks*, thus new

<sup>&</sup>lt;sup>1</sup>http://wiki.c2.com/MissionCritical

<sup>&</sup>lt;sup>2</sup>http://wiki.c2.com/TheracTwentyFive

<sup>&</sup>lt;sup>3</sup>http://wiki.c2.com/TimeCritical

verification and test development methods and their tooling are of key importance. This way, any increase in productivity of testing methods and tools would have strong impact on the productivity of the whole development process and on MCS software assurance in general.

## 1.2 The scope of the thesis

In this thesis, the research is focused on model-based testing, specifically, on the test purpose specification and test generation techniques to address the test coverage and back-traceability of faults problems capitalized in Section 1.1.

The scope of the thesis is defined from three interrelated perspectives:

- The application domain that dictates needs and constraints on the testing approach;

- The testing technology applied to meet these needs;

- The *formal framework* used to automatize the test purpose specification and generation procedures.

## 1.2.1 The application domain perspective

The applications that require extensive test effort are typically systems that integrate many functions onto one while ensuring the safe segregation of functions with different criticality levels. These systems are called mixed-criticality systems. Those mixed-critical MCS are usually based on a small set of core services that can be used to instantiate the system e.g., networked, virtualized multicore computers satisfying both the performance and segregation demands, which are extended depending on the specifics of a mission with relevant application software services [1]. However, the mixed criticality integration challenge also exists for the development process. Here, model-based engineering enables to integrate numerous functions of different criticality levels onto a shared complex hardware / software platform.

For instance, Robotic systems completing critical missions and having extensive degree of autonomy constitute one subclass of MCS. They operate in the dynamic and often under unpredictable conditions which require complex software solutions and sometimes even dynamic reconfigurability. Examples of such systems are surgical robots and assisting robots used in medical treatment procedures as well as spacecrafts having long term autonomous missions.

One of the practical examples of such MCS is the *Scrub Nurse Robot* (SNR) [6] developed at Tokyo Denki University. It was designed to collaborate with a human surgeon to assist at laparoscopic surgeries. Anticipating surgeon's movements, estimating the course of surgery and planning assisting actions (what instrument to pick, when and how to pass it to the surgeon) needs complex decision making methods, high degree of precision in timing and in manipulator movement planning. Exhaustive manual testing of SNR application appeared to be extremely time consuming and error prone due to factors such as variability of surgeon motion characteristics, imperfections of fusing different sensor types (cameras, IMU, etc.), mechanical inertia when moving instruments of different weight and shape, safety precautions of picking and handling instruments to surgeon (instrument must be in steady position and orientated properly when surgeon can safely grasp it), etc.

Due to safety-criticality and complex use cases, such applications as SNR set high requirements on testing. Extensive number of combinations of movement characteristics and variations of behaviour have to be covered by tests. Doubtlessly, exhaustive manual testing or even writing only test scripts for automatic test execution of these test cases remains out of the practical feasibility limits.

Satellite mission control. Launch and early orbit phase (LEOP) are the critical first steps in a spacecraft's life starting after the satellite separates from the launcher's upper-most stage. Mission control on-board software is responsible for activating, monitoring and verifying various subsystems on board the satellite, to ensure that the solar panels have deployed and that they undertake critical orbit and attitude control manoeuvres.

During LEOP the ground station software should provide extra telecommanding 'passes', time slots when the satellite is in view of a station. This provides mission controllers flexibility when complex command stacks must be sent up or additional software must be uploaded to troubleshoot any problems that may be found.

In the later phases of mission, despite the best preparations, unforeseen problems and challenges often arise that must be solved in real-time by mission control software autonomously when the satellite is out of communication range or already too far for timely communication. The onboard mission control operates in synch with core functionalities of the satellite control software including flight control, flight dynamics, telecommanding and data receipt via ground stations, and at the same time, has to take care of high-level functions such as conflict resolution, algorithm generation, event and plan generation.

Common features to be addressed when testing the use cases of satellite mission control are:

- significantly longer communication delays compared to local computation deadlines, e.g., when communicating with a ground station,

- security vulnerabilities due to communicating via open channels,

- functional interference between software components,

- non-determinism regarding events timing,

- varying control and data transmission capabilities (the communication depends on the satellite position in the orbit, atmospheric conditions), etc.

#### 1.2.2 The testing technology perspective (to meet the requirements)

According to standard IEEE-1012-2004 testing is considered to be part of the software verification and validation (V&V) processes. *Verification* focuses on evaluating whether the software matches its specification, the *validation* goal is to assess if the specification matches the customer's requirements. Software testing as a method can be used in both. While the testing of functionality has been used traditionally in non-critical software development approaches, verifying and validating the predictable timing of critical services in the presence of heterogeneous and evolving distributed architectures remains still a challenge [6]. Therefore, validation methods like bench testing and encasing alone, although helpful and widely used, have become insufficient for MCS.

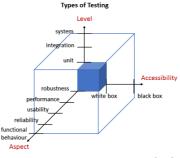

The quality and productivity issues of MCS V&V can be mitigated with model-based techniques and tools that operate on relevant level of abstraction [28]. MBT as one group of such techniques provides the opportunities for test automation and reduces systems V&V effort [39]. MBT suggests the use of a formal model for specifying the expected behaviour of System Under Test (SUT) and the test purpose. For instance, the behaviours or model elements to be covered by tests are subject to test purpose specification. Both, the SUT model and the test purpose specification are pre-requisites for automatic test generation. According to the taxonomy shown in Figure 1 [35] MBT captures the up-right corner

of the Accessibility-Level plane and extends through all categories along the Aspect dimension. Thus, MBT advantages expose most clearly in *Integration* and *System* level testing where the functionality, timing, safety, security and other aspects of MCS are inspected in their most integrated form.

Figure 1 - Taxonomy of testing [40]

From test generation-execution point of view, in MBT the tests are generated either in *offline* or *online* mode. The online testing (test generation) can be divided internally by the methods how the test purpose is defined and how the test stimuli are selected on-the-fly. Online test execution requires more run-time resources for interpreting the SUT outputs and selecting new inputs until the test verdict about the conformance relation can be made. In offline testing, it is required to explore the whole state space of the model of SUT prior to generating the tests and therefore, the computationally expensive state space exploration is not needed during test execution anymore.

MBT focuses on the *conformance testing* where the SUT is considered to be a "blackbox", i.e. only its inputs and outputs are assumed to be externally controllable and observable, respectively. The internal behaviour of the system is abstracted away in a model. The aim of black-box conformance testing, according to [41], is to check if the behaviour observable on the system interfaces conforms to that of given in the system requirements specification. During MBT, a tester executes selected test cases (extracted from the system specification model) by running SUT in the test harness and emits a test verdict (*pass*, *fail, inconclusive*). The verdict shows test result in the sense of a conformance relation between SUT and the requirements model. A conformance relation used most often in MBT is Input-Output Conformance (IOCO) introduced by Tretmans [37]. The behaviour of IOCO-correct implementation should respect after some observations the following restrictions:

- the outputs produced by SUT should be the same as allowed in the requirements model;

- if a quiescent state (a situation where the system cannot evolve without an input from the environment) is reached in SUT, this should also be the case in the model;

- any time an input is possible in the model, this should also be the case in the SUT.

From MBT point of view, the aim of the thesis is to develop an *expressive test purpose specification language* and the *method of extracting complex test cases* from SUT models. The derived tests should satisfy the coverage criteria specified in the test purpose, be *correct*, which means that they should not signal errors in correct implementations, and should be *meaningful*, i.e. erroneous implementations should be detected with high

probability [36]. To address the problems of complexity and traceability in MBT the thesis extends the model-based conformance testing with *a scenario based test description language*  $TDL^{TP}$  and an automatic *test generation technique* and *tool*.

#### 1.2.3 Formal modelling perspective

MBT relies on formal models. The models are built from the requirements or design specifications in order to describe the expected behaviour of SUT in interaction with its environment. The model should be precise, unambiguous, and presented in a way relevant for correctness verification and test generation.

Another main purpose of using models in MBT is that the models of SUT are used to retrieve a test suite consisting of a set of test cases. The test cases are selected by means of a test case specification. The standard ETSI ES 202 951 v1.1.1 (2011-07) "Requirements for Modelling Notations" is used to define characteristics of MBT [3]. These characteristics concern main phases of the MBT process: SUT and its environment modelling, test purpose specification that defines the test coverage criteria, test generation and test execution steps.

Based on the rigour of semantics, the models used in testing can be classified into formal, semi-formal and informal ones. The models with strict formal semantics provide certainty that if the models represent systems adequately, then all the properties verified, really hold. However, formal models tend to have some practical usability limits for MBT, in particular, the scalability of test generation methods for large industrial systems. Due to high complexity their usage is typically limited with critical software domains such as automotive, medical, military, and critical infrastructure systems. The general purpose software industry uses semiformal modelling languages such as Unified Modelling Language (UML), Systems Modelling Language (SysML) and others which are expressive and intuitive to designers, but lack fully rigorous semantics. Regardless the lack of complete formal semantics they are preferred also due to elaborated graphical representations and tool support. Informal models are used to communicate the main ideas but they lack a clear semantics and are not suitable for development of critical systems. Regardless the wide use of UML, a considerable amount of testing theory has been conducted on formal models, in particular, based on different classes of state machines. An extensive survey on modelling formalisms used in MBT can be found in [30].

From the test goal specification and automated test generation point of view, the modelling formalism to be used for MCS should be expressive enough to specify the features of systems that are required to be tested. The class of systems in the thesis target domain - TCS and MCS can be characterized with the following features: behaviours of TCS have projection in the unbounded and dense time domain featuring effects such as Zeno behaviour and time bounded fairness; explicit reference to metric time constraints; simultaneous behaviours on different time scales and their interrelations; timing as well as data dependent non-determinism of behaviours; both synchronous and asynchronous concurrency between the parallel components of the system.

The formal notation should be supported also by the analysis methods where the properties of practical importance (safety, bounded reachability, etc.) are decidable and their verification feasible from the complexity point of view. The last presumes modelling and verification automation tools that meet also practical usability requirements. Since the theory of timed automata and its extension Uppal timed automata (Uppaal TA) theory satisfy the criteria listed above, the thesis relies on the underlying theory of Uppaal TA. Related Uppaal<sup>4</sup> tool family, supports modelling, validation and verification of real-time

<sup>&</sup>lt;sup>4</sup>http://www.uppaal.org

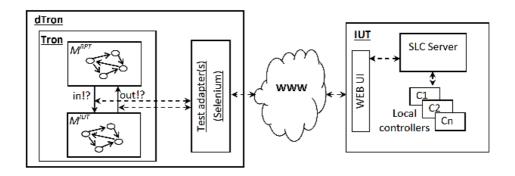

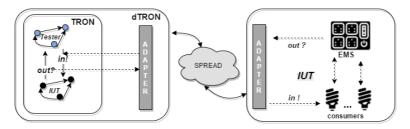

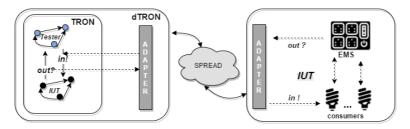

systems. Uppaal TA model systems as a collection of non-deterministic processes with finite control structure and real-valued clocks, communicating through channels and (or) shared data structures. Typical application areas include systems in which timing aspects are critical. In particular, for online test execution the tool Uppaal Tron and its extension for distributed testing DTron will be exploited in this work.

## 1.3 Related work

The requirements to the test purpose specification languages for MBT can be summarized as following:

- *intuitivity* to support human comprehension and to make the specification process user-friendly;

- *expressiveness* to capture the features and behaviours under test in a compact and unambiguous form;

- *formal semantics* to make the test purpose specifications verifiable and pertinent for automated test generation;

- *decidability* to make the test generation from test purpose specification algorithmically feasible.

The first two criteria have been capitalized in earlier attempts of designing test purpose specification languages. Check Case Definition Language (CCDL) [31] provides a high-level approach for requirements-based black-box system level testing. Test simulations and expected results specified in human readable form in CCDL can be compiled into executable test scripts. However, due to the lack of standardization, high-level test descriptions in CCDL are heavily tool-dependent and can be embedded only in its proprietary testing process.

High-level keyword-based test languages, using frameworks such as the Robot Framework<sup>5</sup>, have also been integrated with MBT [32]. In some domains such as avionics [22] and automotive industry the efforts have been made to address the standardization of testing methods and languages, e.g. creating a meta-model for testing avionics systems [22], and the Automotive TestML [21] focusing on automotive systems. Similarly, the Open Test Sequence Exchange Format (OTX) [9] standardized at the International Organization for Standardization (ISO) provides tool-independent XML-based data exchange format [10] for the formal description and documentation of executable test sequences for automobile diagnostics. These efforts have focused primarily on enabling the exchange of test specifications between involved stakeholders and tools, and do not possess precise semantics. Due to their domain and purpose specialization the applicability of these languages in other domains is limited.

The Message Sequence Chart (MSC) [8] standardized at the International Telecommunication Union (ITU) was one of the first languages for the specification of scenarios, not focusing strictly on testing. In addition, [7] provides a formal specification of the semantics of MSC. Some of the features of MSC are adopted in UML as Sequence Diagram. The loose semantics of UML and various interpretations of sequence diagrams are a limiting factor for its use as a universal and consistent test description language [4].

The Precise UML [14] introduces a subset of UML and OCL for MBT trying to provide strict semantics of different diagrams. This was motivated by the need for behavioural specifications of SUT which are well suited for generating test cases out of SUT models.

<sup>&</sup>lt;sup>5</sup>https://robotframework.org

Though, the experience with approaches that are based on a concrete executable language with strict semantics, such as TTCN-3, are not well suited for review and high-level interpretation of testing results. This is due to the low level of detail and the need to be able to understand the programming language-like syntax [20].

The domain specific and weakly formalized test purpose specification languages referred above share also a common set of disadvantages, either they have imprecise or informal semantics, lack of standardization, lack of comprehensive tool support, or poor interoperability with other development and testing tools.

*European Telecommunications Standards Institute ETSI* intended to address these shortcomings and develop a new specification language standard by introducing Test Purpose Language (TPLan) that supports the high-level expression of test purposes in prose [2]. Though TPLan provides notation for the standardized specification of test purposes, it leaves a gap between the declarative test purposes and the imperative test cases. Without formal semantics the development of test descriptions by means of different notations and dialects led to significant overhead and frequent inconsistencies that needed to be checked and fixed manually.

As a consequence, ETSI started a new initiative to develop the Test Description Language TDL [20] intended to bridge the gap between declarative test purposes and imperative test cases by offering a standardised approach for the specification of test descriptions. TDL provided a standardised meta-model, that was subsequently enriched with a graphical syntax, exchange format, and a UML profile. By 2015 ETSI succeeded in completing TDL as a common meta-model with well-defined semantics, which can be represented by means of different concrete notations. The main benefits of ETSI TDL outlined in [20] are:

- higher quality tests through better design;

- easier layout to review by non-testing experts;

- better and faster test development;

- seamless integration of methodology and tools.

The development of ETSI TDL was driven by industry where it is used primarily, but not exclusively, for functional testing. To enable the application of TDL in UML based working environments, a UML Profile for TDL (UP4TDL) [4] was developed. Domain-specific concepts are represented in a UML profile by means of *stereotypes*. A stereotype enables the extension of a UML meta-class with additional properties, relations, or constraints in order to address domain-specific concerns.

Though the ETSI TDL features one of the most advanced test purpose description language it has room for improvements including following:

- Automatic mapping of ETSI TDL to TTCN-3, that is needed for generating executable tests from TDL descriptions and re-using the existing TTCN-3 tools and frameworks for test execution, is not fully defined yet.

- Adaptation of TDL to different domains and types of testing in order to determine new language features and extensions, e.g. for security and performance testing, needs to be done.

- Restricted timing semantics. The *Time* package in TDL contains concepts for the specification of time operations, time constraints, and timers. TDL time operations include *Wait* and *Quiescence* and timer operations *Start*, *Stop*, *Timeout*. Since time

in TDL is global and progresses monotonically in discrete quantities there is no way of expressing synchronization conditions between local time events of parallel processes and detecting possible *Zeno computations* that can be analysed in continuous time models. Similarly, *time-divergency* (a path is time-divergent if its execution time is infinite), *timelock-freedom* cannot be *analysed* (a model is timelock-free if no state in the reachability set of the model contains a timelock - a state contains a timelock whenever no time-divergent paths emanate from it).

As one step further towards automatic test generation, the timed games based synthesis of test strategies has been introduced in [17] and implemented in the Uppaal Tiga tool. Timed computation tree logic (TCTL) is used to specify test purpose in this approach. TCTL has high expressive power and formal semantics relevant for expressing quantitative time properties combined with CTL operators such as AG ('*always*'), AF ('*inevitable*'), EG ('*potentially always*'), EF ('*possible*'), and > ('*leads-to*') [16].

Due to the complexity consideration of model checking, the TCTL syntax in Uppaal tool is limited with un-nested operators only, making the TCTL expression with respect to the temporal operators 'flat'. On the other hand, to specify the properties of timed reachability the 'flat' TCTL expressions are not sufficient for specifying complex properties and so called auxiliary property recognizing automata have to be added to the test models. An instance of such auxiliary automata is 'stopwatch' automata that are needed to compensate for that deficiency. Modifying the test model structure by adding property automata is not trivial for non-expert and may be error prone process leading to the unintended changes of model semantics.

As an extension to TCTL based test purpose specification language, the aim of thesis is to build an extra language layer (Test Scenario Definition Language -  $TDL^{TP}$ ) for test scenario specification that is expressive, free from the limitations of 'flat' TCTL, interpretable in Uppaal TA, and thus, suited for automated test generation.

## 1.4 Main hypothesis and goals

The research goals of the thesis are based on following hypothesis:

- Due to its high expressive power the representation of test scenarios in *TDL*<sup>TP</sup> is more compared to that of TCTL;

- Formal semantics of *TDL<sup>TP</sup>* expressions enables

- formal correctness verification of test models and test purpose specifications, incl. evaluation of their feasibility, time/space complexity;

- automated generation of tests from verified models;

- interpretation of different coverage criteria and back-tracing the root causes of found bugs.

- The *TDL<sup>TP</sup>* expressions can be interrelated with other test coverage criteria and coverage metrics like structural coverage, function coverage, requirement coverage etc.

The technical goals of the thesis are following:

- Defining the syntax of test scenario definition language *TDL*<sup>*TP*</sup>;

- Defining the interpretation of  $TDL^{TP}$  in terms of language generating Uppaal TA;

- Designing and implementing the interpreter of  $TDL^{TP}$  and based on that a symbolic test generator;

- Integrating the *TDL*<sup>TP</sup> usage into provably correct testing workflow described in Publication II.

- Demonstrating the feasibility of *TDL*<sup>TP</sup> usage on a practical non-trivial test purpose specification and test generation case study.

## 1.5 The methodology used in the thesis

The research methodology applied in the thesis relies on the theory of automata, model checking and model-based testing. To achieve the thesis goals, following concrete techniques and methods are applied:

- *TDL<sup>TP</sup>* syntax is defined in textual form that is inspired by temporal logic and process algebra notation;

- To reuse the existing test generation methods designed for Uppaal TA, the semantics of  $TDL^{TP}$  operators is interpreted by transforming the terms of  $TDL^{TP}$  to fragments of Uppaal TA that constitute the executable test model;

- *TDL<sup>TP</sup>* interpretation rules are defined recursively as rewriting rules applicable to the terms of *TDL<sup>TP</sup>* expressions;

- the correctness of SUT models and the test models generated from  $TDL^{TP}$  is verified using TCTL model checking. The verification follows methodology introduced in [43];

- the usability of *TDL*<sup>TP</sup> is validated on a case study where TUT100 satellite software is tested and *TDL*<sup>TP</sup> expressions are extracted from the satellite software requirements specification;

- the efficiency evaluation of the developed approach is measured in terms of saved test generation effort, and detected bugs *back-traceability* effort (the bug is *back-traceable* if the term of TDL expression can be referred to which caused the 'test fail').

## **1.6** Thesis main contributions

The thesis provides the following novelties in the field of model-based testing:

- 1. Defines a highly expressive test purpose specification language  $TDL^{TP}$  for complex test scenario specifications that is needed for MBT in safety and time critical systems.

- 2. Gives the semantics of  $TDL^{TP}$  operators that is defined in terms of model transformation rules that map declarative  $TDL^{TP}$  expressions to executable test models represented as Uppaal timed automata.

- 3. A provably correct test development process model is introduced and correctness conditions specified to be verified when showing correctness of test development steps.

- 4. Validation of the thesis theoretical results on the TUT100 satellite software case study.

## 1.7 Chapter summary

This chapter gives the motivation about why further research is needed in the domain of critical software engineering theory and practice. We define the research problems to be solved and their scope from three perspectives, the application domain that dictates the needs and constraints on the testing approach, the testing technology applied to meet these needs and the underlying formal framework to implement the MBT approach. Based on the analysis of the related work on test purpose specification languages it was concluded that extensions towards languages expressive power and semantic rigour are needed to support automatic test generation from coverage specifications. Research methodology how to solve these problems in the thesis was outlined. Finally, problem specific hypothesis and goals were defined to keep the focus and to prove the validity of targeted results.

# **2 PRELIMINARIES**

In this chapter, the basics of testing are introduced in the context of model-based testing process while capitalizing the role of formal test model development and test purpose specification. Uppaal Timed Automata are defined as the modelling formalism for SUT description and test execution environment Uppaal Tron is explained as relevant tool for this class of models. To decide on the test sucess or fail, the Relativized Timed Input Output Conformance (RTIOCO) relation between the model and system under test is defined. Finally, related work on test coverage criteria and test purpose specification languages used in model-based testing are reviewed and the need for a new multi-criterial test scenario specification language is articulated.

## 2.1 Model-based testing

Typically, MBT is a black box testing technique where state machine models are used as specifications of observable interactions between SUT and its environment. The goal is to project the behaviours described in the model onto SUT by sending model generated test stimuli to SUT and observing if reactions of SUT conform to those specified in the model.

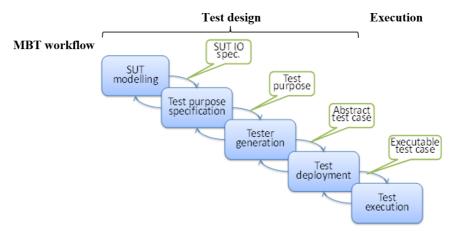

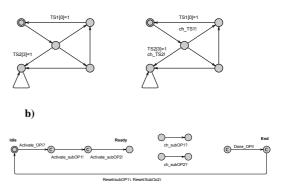

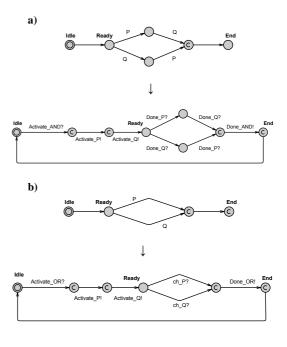

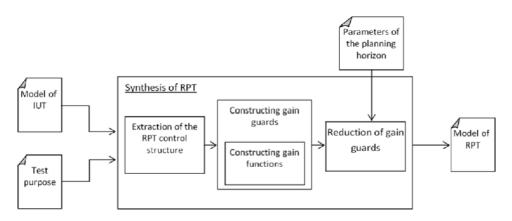

Like other software processes the MBT test development can follow different process models - waterfall, spiral, v-shape, agile etc. Regardless the process model all of them include five principal steps: *modelling of SUT*, *specification of the test purpose*, *test generation*, *deployment*, *and execution*. In this thesis, we exploit as an example the waterfall shape test development process model shown in Figure 2 [43].

Figure 2 - Waterfall shape MBT workflow

Based on the test requirements and the test plan, a test model is constructed, at first. The model is usually an abstract, partial representation of the desired behaviour of SUT. The test model is used to generate the test cases that together form an abstract test suite. In principle, the test models can represent infinite sets of SUT behaviours. Therefore, test selection criteria, specified as *test purpose*, are meant to select a finite and practically executable set of implementable test cases. For example, different model coverage criteria, such as all-states, all transitions, selected branching conditions etc. can be used to extract the corresponding test cases.

The coverage of model structural elements (states and transitions) can be used also as a measure of *thoroughness* for a test suite. Thus, a test purpose is a specific objective (or property) that the tester wants to test, and can be seen as a specification of the test case. It may be expressed in terms of a single coverage item, scenarios, duration of the test run etc. As an example let us consider a requirement "Test a state change from state  $s_A$  to state  $s_B$ " in a model  $M^{SUT}$ . For this purpose, a test case should be generated such that, when starting from the initial state  $s_0$  of  $M^{SUT}$ , it covers the specific state transition  $s_A \rightarrow s_B$  of  $M^{SUT}$ . This requires that the test drives SUT to the state  $s_A$ , then executes  $s_A \rightarrow s_B$  and the test should terminate in some safe state of  $M^{SUT}$  after that.

For non-deterministic systems a single precomputed test sequence may never succeed in reaching the test goal if  $M^{SUT}$  is not deterministically test-controllable. Instead of a single test sequence we need here an online testing strategy that is capable of reaching the goal even when SUT provides non-deterministic responses to test stimuli. The issue is addressed in [44] where the reactive planning online tester synthesis method is described.

In the third step, the abstract test suite is generated from the model consisting of SUT and the environment component so that the test purpose can be reached by executing the test suite. The test sequences generated are the intersection of behaviours of SUT and those specified by the test purpose.

The abstract test cases are deployed using the test execution framework. Deployment means transforming abstract tests to executable test scripts or by introducing test adapters which map symbolic model inputs to executable ones and the concrete outputs of SUT back to symbolic form to compare them with ones given in the model. The advantage of separating an abstract test suite and concrete test suite is the *platform* and *language independence* of the abstract test cases so, that the same abstract test case can be executed in different test execution environments.

In the fifth step, the deployed test cases are executed against the SUT. The test execution will result in a report that contains the outcome of the execution of the test cases. After the test execution, the detected bugs are analysed and their root cause backtracked. Hereby, for each test that reports a failure, the cause of the failure is determined and the program (or model) is corrected.

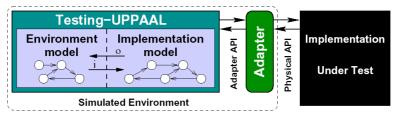

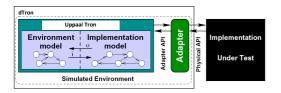

An example of symbolic test execution tool for Uppaal TA is Uppaal-TRON [25] depicted in Figure 3.

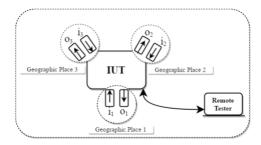

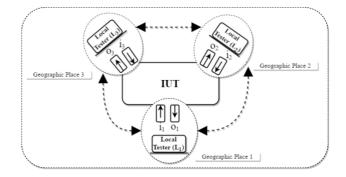

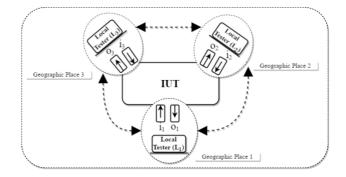

Figure 3 - Online MBT execution architecture: Uppaal-TRON

### 2.2 Uppaal timed automata

The Uppaal TA are extension of Timed Automata defined in [13] as follows:

#### **Definition 2.1 (Timed Automaton)**

Assume  $\Sigma$  denotes a finite alphabet of actions  $a, b, \ldots$  and C a finite set of real-valued variables x, y, z, standing for clocks. A guard is a conjunctive formula of atomic constraints of the form  $x \sim n$  for  $c \in C, \sim \in \{\geq, \leq, =, >, <\}$  and  $n \in \mathbb{N}^+$ . We use G(C) to denote the set of guards.

A timed automaton A is a tuple  $\langle L, l_0, E, I \rangle$  where

- *L* is a finite set of locations (or nodes),

- $l_0 \in L$  is the initial location,

- $E \in L \times G(C) \times \Sigma \times 2^C \times L$  is the set of edges and

- $I: L \to G(C)$  assigns invariants to locations (here we restrict to constraints in the form:  $x \le n$  or  $x < n, n \in \mathbb{N}^+$ . For shorthand we write  $l \xrightarrow{g,a,r} l'$ , to denote edges.

To define the clock conditions with respect to local events the functions known as clock resets are used. They map *C* to non-negative naturals  $\mathbb{N}$ . To keep the analysis tractable we limit the class of timed automata to rectangular timed automata where guard conditions are in conjunctive form with conjuncts of the form  $k \sim n$  for  $n \in \mathbb{N}$ , and  $\sim \in \{\geq, \leq, =, >, <\}$ .

#### Definition 2.2 (Operational Semantics of TA)

The semantics of a timed automata are defined as a transition system. There are two types of transitions between states: either delay, or action (action transition).

To keep track of the changes of clock values, we use a function known as clock assignment that maps *C* to non-negative reals  $\mathbb{R}$ . Let u, v denote such functions, and  $u \in g$ means that clock values denoted by u satisfy the guard g. For  $d \in \mathbb{R}^+$  let u + d denote the clock assignment that maps all  $x \in C$  to u(x) + d. For  $r \subseteq C$ , let [0/r] denote the clock value substitution for all clocks in r to 0 and preserving the value of other clocks in  $C \setminus r$ .

The operational semantics of timed automata is represented using timed transition system where states are pairs  $\langle l, u \rangle$  and transitions are defined by the rules:

- Timed transitions:  $\langle l, u \rangle \rightarrow_d \langle l, u+d \rangle$  if  $u \in C(l)$  and  $(u+d) \in C(l)$  for a non-negative real  $d \in \mathbb{R}^+$ ;

- Action transitions:  $\langle l, u \rangle \rightarrow_a \langle l', u' \rangle$  if  $l \xrightarrow{g,a,r} l', u \in g, u' = u[0/r]$  and  $u' \in I(l')$ .

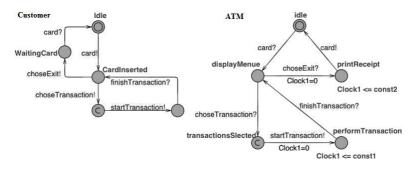

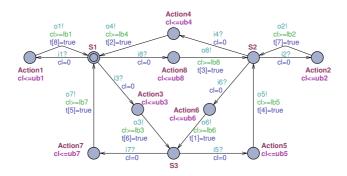

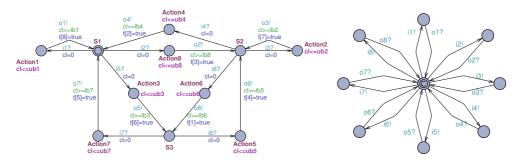

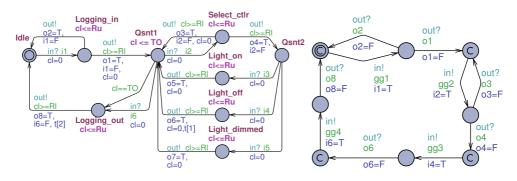

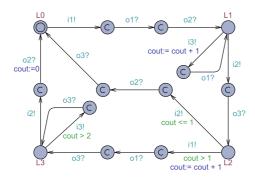

The graphical representation of a timed automaton is considered as a directed graph, where locations are represented by the vertices and they are connected by edges (see Figure 2.3). Locations are labelled with invariants. Invariants are conjunctive Boolean expressions where the literals consist of clock variables and bound conditions of clock variables, e.g.  $Clock1 \le const1$ .

In the graphical representation the edges are annotated with guards, synchronisations and updates. An edge is enabled by a guard in a state if and only if the guard evaluates to true. Processes (parameterized instances of automata templates) can synchronize transitions over channels. The execution of two edges of different automata labelled with a common channel is synchronized. For instance in Figure 4, the edge *WaitingCard*  $\rightarrow$  *Idle* of Customer automaton and the edge *printReceipt*  $\rightarrow$  *Idle* of ATM automaton synchronize over channel *card*. Updates express the change of the system state when the edge is executed, e.g., update *Clock*1 = 0 resets the value of model clock *Clock*1.

To model concurrent systems, TA are extended with parallel composition. A network of TA  $N_{TA} = (T_1||...||T_n)$  is a collection of concurrent TA  $T_i(i = 1, ..., n)$  composed using parallel composition. The state of the network is modelled by a configuration  $\langle \bar{l}, \bar{c} \rangle$ , where the first component is a location vector  $\bar{l} = \langle l_1, ..., l_n \rangle$  where  $l_i$  is the current location of automaton  $T_i$ . The second component  $\bar{c} \in \mathbb{R}^+$  is the valuation of all clock variables. The initial configuration of the network is  $\langle \bar{l}, \bar{c} \rangle$ , where all automata in  $N_{TA}$  are at initial configuration and the valuation of all clock variables is zero.

Figure 4 – The TA model of ATM

Similarly to TA network configuration a symbolic state s of a single timed automaton T is a pair  $\langle l, c \rangle$ , where  $l \in L(T)$  is a location and c is the valuation of all clocks in C(T). The valuation c must always satisfy the invariant constraints in the current location of the automaton  $l : c \models I(l)$ . There are three types of transitions in a TA network. A transition for TA network  $N_{TA}$  is defined by:

- Action transition: if  $l_i \xrightarrow{g,a,r} l'_i$  is an action transition in the *i*-th automaton  $T_i$  with a guard over clock constraint  $g(\bar{c}), \bar{c}' \models I(\bar{l}')$ , an action  $a \in A$ , and an action transition  $\langle \bar{l}, \bar{c} \rangle \xrightarrow{a} \langle \bar{l}_j, \bar{c}' \rangle$ .

- Synchronized transition: if  $l_i \xrightarrow{g_1,a,r_1} l'_i$  and  $l_j \xrightarrow{g_2,\bar{a},r_2} l'_j$  are edges in *i*-th and *j*-th  $(i \neq j)$  automata synchronized via action *a* and its co-action  $\bar{a}$  with  $\bar{c} \models (g_i \land g_j)$  and  $\bar{c}' \models I(\bar{l}')$ , then  $\langle \bar{l}, \bar{c} \rangle \xrightarrow{\tau} \langle \bar{l}', \bar{c}' \rangle$  is an internal action transition in  $N_{TA}$ , where  $a, \tau \in A, \bar{l}' = \bar{l}[l'_i/l_i, l'_j/l_j]$ , and  $\bar{c}' = (r_1 \land r_2)(\bar{c})$ . Notation  $\bar{l}[l'_i/l_i]$  means substitution of all occurrences of  $l'_i$  with  $l_i$  in  $\bar{l}$  [33].

- Delay transition: if  $\delta \in \mathbb{R}^+$  is a delay with condition  $\forall d < \delta : (\bar{c} + d) \models I(\bar{l})$ , then  $\langle \bar{l}, \bar{c} \rangle \xrightarrow{\delta} \langle \bar{l}', \bar{c} + \delta \rangle$  is a  $\delta$ -delay transition in  $N_{TA}$ .

Uppaal timed automata [12] extend TA also with data types such as bool, integer, arrays of both types but also types of locations such as committed, urgent and normal. The advantage of this extension is that the model has rich enough modelling power to represent real-time and resource constraints and at the same time to be efficiently decidable for reachability analysis.

**Definition 2.3** A timed automaton with data variables (TAD) over actions A, clock variables C and data variables V is a tuple  $(L, l_0, E)$  where

- *L* is a finite set of locations,

- *l*<sup>0</sup> is the initial location,

- *E* ⊆ *L*×*G*(*C*,*V*)×*A*×*P*<sup>*C*</sup>×*L* corresponds to the set of edges, where *G*(*C*,*V*) is set of guard conditions that range over *g*.

- *g* is a constraint in the form:  $c \sim n$  or  $v \sim n$  for  $c \in C, v \in V, v \in \{\geq, \leq, =\}$  and *n* is a natural number.

- the guards G(C,V) can be divided into two parts: a conjunction of constraints over clock variables in the form c ∼ n and conjunction of constraints over data variables in the form v ∼ n.

## 2.3 Conformance testing with Uppaal TA

We define the conformance relation using Uppaal TA semantics representation as a timed labelled transition system (TLTS). TLTS is a 4-tuple  $(S, s_0, Act_{\tau\varepsilon}, \rightarrow)$ , where

- *S* is a non-empty set of states

- $s_0 \in S$  is the initial state

- $Act_{\tau\varepsilon} \stackrel{def}{=} Act \cup \{\tau\} \cup D$  are the actions Act including the internal action  $\varepsilon$  and timepassage actions  $\tau$ ; where  $D = \{\varepsilon(d) \mid d \in \mathbb{R}^+\}$

- $\rightarrow \subseteq (S \times Act_{\tau \varepsilon} \times S)$  is the transition relation with the following consistency constraints:

- Time Determinism whenever  $s \xrightarrow{\varepsilon(d)} s'$  and  $s \xrightarrow{\varepsilon(d)} s''$  then s' = s''

- Time Additivity  $\forall s, s'' \in S \land \forall d_1, d_2 \ge 0 : (\exists s' \in S : s \xrightarrow{\varepsilon(d_1)} s' \xrightarrow{\varepsilon(d_2)} s'') \text{ iff } s \xrightarrow{\varepsilon(d_1+d_2)} s'' \xrightarrow{\varepsilon(d_1+d_2)} s''$

- Null Delay  $\forall s, s' \in S : s \xrightarrow{\varepsilon(0)} s' \text{ iff } s = s'.$

The labels in  $Act_{\varepsilon}$  (where  $Act_{\varepsilon} \stackrel{def}{=} Act \cup D$ ) represent the observable input-, output actions  $(Act = Act_I \cup Act_O)$  of a system, i.e. labelled actions and passage of time; the special label  $\tau$  represents an unobservable internal action. A transition  $(s, \mu, s') \in \rightarrow$  is denoted as  $s \stackrel{\mu}{\to} s'$ .

A computation is a finite or infinite sequence of transitions:  $s_0 \xrightarrow{\mu_1} s_1 \xrightarrow{\mu_2} s_2 \xrightarrow{\mu_3} \dots \xrightarrow{\mu_{n-1}} s_{n-1} \xrightarrow{\mu_n} s_n(\rightarrow \dots)$

A *timed trace* captures the observable aspects of a computation; it is the sequence of observable actions. The set of all *finite* sequences of actions over  $Act_{\varepsilon}$  is denoted by  $Act_{\varepsilon}^*$ , while  $\varepsilon$  denotes the empty sequence. If  $\sigma_1, \sigma_2 \in Act_{\varepsilon}^*$  then  $\sigma_1 \cdot \sigma_2$  is the concatenation of  $\sigma_1$  and  $\sigma_2$ .

We consider normalised traces where actions and delays strictly alternate, starting with a delay. It has been shown that this set characterises the set of all traces [5]. A timed trace is thus a sequence  $\sigma \in (\mathbb{R}_{\geq 0} \cdot Act)^* \cdot (\mathbb{R}_{\geq 0} + \varepsilon)$  such that  $s_0 \xrightarrow{\sigma} s'$  for some  $s' \in S$ . The set of traces of TLTS *S* is noted traces(S). The set of states that can be reached from state *s* via a trace  $\sigma$  is denoted as *s* after<sub>t</sub>  $\sigma$ .

**Definition 2.4 (***after*<sub>*t*</sub>**).** Let  $\langle S, Act, s_0, \rightarrow \rangle$  be a TLTS and  $\sigma \in (\mathbb{R}_{\geq 0} \cdot Act)^* \cdot (\mathbb{R}_{\geq 0} + \varepsilon)$ . Then *s* after<sub>*t*</sub> $\sigma =_{def} \{s' \mid s \xrightarrow{\sigma} s'\}$ .

Crucial for the definition of *tioco* is the set of delay and output labels of the outgoing transitions of a state.

**Definition 2.5 (***elapse*(*s*) **and** *out*<sub>*t*</sub>(*s*) **).** We define *elapse*(*s*) =<sub>*def*</sub> { $d | s \xrightarrow{d}$ }, and *out*<sub>*t*</sub>(*s*) =<sub>*def*</sub> { $o \in Act_U | s \xrightarrow{o}$ }  $\cup$  *elapse*(*s*). For  $S' \subseteq S$ , *out*<sub>*t*</sub>(S') =<sub>*def*</sub>  $\cup_{s \in S'} out_t(s)$ .

As in the *ioco* theory, we assume that implementations under test are input-enabled. **Definition 2.6 (Input-enabled** *TLTS*). A *TLTS*  $\langle S, Act, s_0, \rightarrow \rangle$  is called input-enabled if and only if for all  $s \in S$  and all  $i \in Act_I : s \stackrel{i}{\rightarrow}$ .

With the introduced concepts we can define the family of implementation relations  $tioco_F$ .

**Definition 2.7** (*tioco<sub>F</sub>*). Let *P* be an input-enabled *TLTS*, *S* a *TLTS*, and  $F \subseteq traces(S)$ . Then *P* conforms to *S* w.r.t. *tioco<sub>F</sub>* (written *P* tioco<sub>F</sub>*S*) if and only if the following holds:  $\forall \sigma \in F : out_t(P \text{ after}_t \sigma) \subseteq out_t(S \text{ after}_t \sigma)$ .

#### Definition 2.8 Relativized timed input/output conformance (RTIOCO)

Let  $TTr_i$  be projection of traces(S, E) on input alphabet  $\Sigma^I$ , i.e.

$$TTr_i(S, E) = traces(S, E)|_{\Sigma^I}$$

and let  $TTr_o$  be projection of traces(S, E) on output alphabet  $\Sigma^O$ , i.e.

$$TTr_o(S, E) = traces(S, E)_{|\Sigma^O|}$$

An implementation *I* conforms to its specification *S* under the environmental constraints *E* if for all timed input traces  $\sigma \in traces(S)$  the set of timed output traces of *I* is a refinement of the set of timed output traces of *S* for the same input trace.

*I* rtioco *S* iff  $\forall \sigma \in TTr_i(E)$  :

$TTr_o((I,E),\sigma) \sqsubseteq TTr_o((S,E),\sigma)$  (1)

The timed traces generated by Upaal verifier provide symbolic test sequences to be executed by Uppaal Tron. For each test event, symbolic state in which the event occurred is specified in terms of clock constraints, variable valuation, list of next available states, and list of input/output actions. In the test sequence, when executed by TRON, a new test event occurs at a specific time, the clock constraints are updated, a transition to a new symbolic state occurs and the list of the next available states is updated.

### 2.4 Test coverage criteria

Test selection criteria are based on what hypothesis about the SUT behavior have to be covered by test cases. Like the code coverage measures what percentage of code is covered by tests, MBT coverge criteria measure how well the generated test suite covers the model elements. Many model coverage criteria have been adopted from the field of code coverage, e.g. statement coverage, decision/condition coverage, etc. In the MBT taxonomy of [40] following coverage based test selection criteria groups are described:

- Structural model coverage

- Data coverage

- Requirements coverage

- Test case specification coverage

- Random & stochastic coverage

- Fault based coverage

Structural coverage criteria deal with coverage of the control-flow through the model, based on analogy of control flow through programs. Structural model coverage criteria are derived from the key concepts of the modeling paradigms used for model-based testing. For example, transition-based notations have given rise to a family of coverage criteria that includes all-states, all-transitions, and all-transition pairs.

Pre/post notations refer to predicate coverage of guards and invariants in the model. For state transition models their control graph related notions can be used such as *all*  states, all transitions, all cycles. Also data-flow coverage criteria reflect the data dependencies in the model computations, e.g. all updates of variables that depend on given input values.

Data coverage deals with the coverage of the input data space of an operation or transition in the model. It presumes choosing test data values from a large input data space. To reduce the number of possible test cases the data space is split into equivalence classes and one representative from each equivalence class has to be chosen to detect potential failures. The partitioning of the value domains into equivalence classes is often complemented by *boundary tests* of the equivalence classes.

*Requirements coverage* aims to generate a test suite that ensures that all the informal requirements are tested. Traceability of requirements can be automated if the fragments of the model can be associated with requirements of the SUT. For instance, if requirements' ID-s are used to label the transitions or states of a state machine or predicates of the post-conditions of a pre- and post-condition model, then test generation can aim to cover all requirements.

*Random & stochastic coverage* based generation is a computationally cheap way to generate tests that explore a wide range of system behaviors. These are mostly applicable to environment models, because it is the environment that determines the usage patterns of the SUT. The probabilities of actions are modelled directly or indirectly. The generated tests then follow an expected usage profile ([49], [29]).

*Fault-based coverage* is used to find faults in the SUT using mutation coverage. This involves mutating the model, then generating tests that would distinguish between the mutated model and the original model. The assumption is that there is a correlation between faults in the model and in the SUT. The mutants are used for test generation against the implementation in order to check whether the latter allows for unspecified behaviors [33].

Ad-hoc test case specifications. To drive the test on heavily used cases, or to ensure that particular paths will be tested an explicit control of test execution can encoded in the test model. The notation used to express these test objectives may be the same as the notation used for SUT modelling, or it may be a declarative notation interpreted on the model. Notations commonly used for test objectives include UML Sequence diagrams, FSMs, regular expressions, temporal logic formulae, constraints and Markov chains (for expressing intended usage patterns). This family of coverage criteria relates to the scenario-based testing approach (e.g., ([50], [38])) where test cases are generated from descriptions of abstract scenarios.

The main advantage of explicit test case specifications is that they give precise control over the test run. The drawback is that such specifications can be more labor intensive than choosing some structural model coverage criteria. Therefore, it is recommended to combine test selection criteria. One such strategy is to start generating tests using simple structural model coverage and data coverage criteria and then use test case specifications to enhance the coverage of SUT parts that are accessible only when applying complex test scenarios.

To summarize, a large variety of coverage criteria can be used to configure an automated test generation process. These criteria have different scopes and purposes, but the key is *complementarity of test selection criteria* [40]. To obtain good quality test suites, different coverage criteria should be combined, particularly when testing complex MCS. In other words, these applications need scenario based testing where multiple coverage criteria are seamlessly combined and applied jointly or separately in the steps of test scenarios. To minimize such multi-criterial scenario specification effort, instead of explicit test control scenario descriptions symbolic languages with rich expressive power are needed.

## 2.5 Chapter summary

Model-based testing of time/mission critical systems presumes relevant formal notation for describing time-dependant complex behaviors of SUT and the test coverage criteria for specifying critical test cases. In this chapter, syntax and semantics of Uppaal Timed Automata which is one of the most relevant formalism for such description, is described. To decide on the test sucess or fail the Relativized Timed Input Output Conformance (RTIOCO) relation between the Uppal TA model and system under test is defined. The taxonomy of test coverage criteria and test purpose specification languages used in model-based testing revieled that the available test specification languages suffer from expressibility and/or automatic test generation support for the class of SUTs of interest in this thesis. As a conclusion the need for a new multi-criterial test scenario specification language for time/mission critical systems is articulated.

# **3 PROVABLY CORRECT TEST DEVELOPMENT**

The provably correct MBT process introduced in Section 2.1 (Figure 2) comprises test development steps (modelling the system under test, specifying the test purposes, generating the tests and executing them against SUT) that alternate with verification steps. In this chapter, the verification of test development steps is described and how the test results are made trustworthy throughout the testing process. We focus on model-based online testing of systems with timing constraints capitalizing on the correctness of the test suite through test development and execution process.

## 3.1 The Correctness of SUT Models

### 3.1.1 Modelling Timing Aspects of SUT

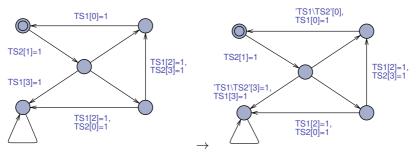

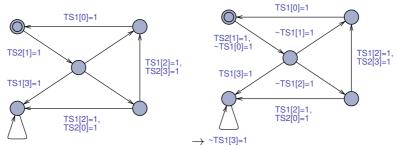

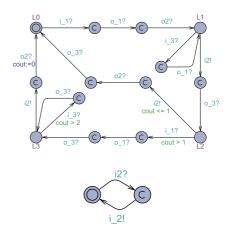

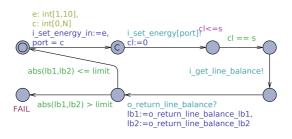

For automated testing of input-output conformance of systems with time constraints we restrict ourselves with a subset of Uppaal TA that simplifies SUT model construction. Namely, we use a subset of Uppaal TA where the data variables, their updates and transition guards on data variables are abstracted away. We use the clock variables only and the conditions expressed by clocks and synchronization labels (channels). An elementary modelling pattern for representing SUT behaviour and timing constraints is *Action pattern* (or simply Action) depicted in Figure 5.

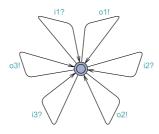

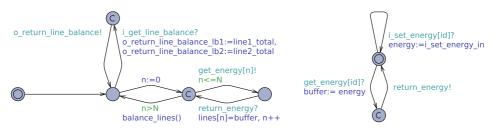

Figure 5 - Elementary modelling fragment

An Action models a program fragment execution on a given level of abstraction as one *atomic step*. The Action is triggered by input event and it responds with output event within some bounded time interval (*response time*). The SUT input events (*stimuli* in the testing context) are generated by Tester, and the output events (SUT *responses*) are to make the reactions of SUT observable to Tester. In Uppaal TA, the interaction between SUT and Tester is modelled with *channels* that link synchronous input/output events.

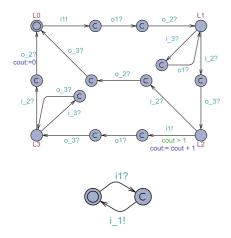

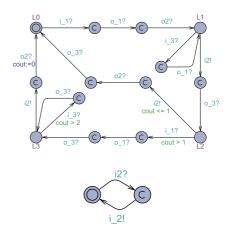

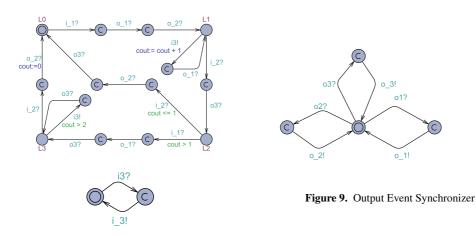

The major timing constraint we represent in SUT model is the duration of the *Action*. To make the specification of durations more realistic we represent it as a closed interval  $[l\_bound, u\_bound]$ , where  $l\_bound$  and  $u\_bound$  denote lower and upper bound repectively. The duration interval  $[l\_bound, u\_bound]$  can be expressed in Uppaal TA as a pair of predicates on clocks as shown in Figure 5. The clock reset *clock* = 0 on the edge (*Pre\_location*  $\rightarrow$  *Action*) makes the time constraint specification *local* to the *Action* and independent from the clock value accumulated during earlier execution steps. The clock invariant *clock\_* <=  $u\_bound$  of location *Action* forces the *Action* to terminate latest at time instant  $u\_bound$  after the clock reset and guard *clock\_* >=  $l\_bound$  on the edge *Action*  $\rightarrow$  *Post\_location* defines the earliest time instant (w.r.t. clock reset) when the outgoing transition of *Action* can be executed.