# Hardware Modeling for Design Verification and Debug

ANTON TŠEPUROV

#### TALLINN UNIVERSITY OF TECHNOLOGY

Faculty of Information Technology Department of Computer Engineering

Dissertation was accepted for the defence of the degree of Doctor of Philosophy in Computer and Systems Engineering on May 13, 2013.

Supervisors: Prof. Jaan Raik,

Dr. Maksim Jenihhin

Department of Computer Engineering, TUT

**Opponents**: Prof. Heinrich Theodor Vierhaus

Brandenburg University of Technology, Cottbus, Germany

Dr. Giovanni Squillero Politecnico di Torino, Italy

**Defence of the thesis**: June 14, 2013

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted for any academic degree.

/Anton Tšepurov/

Copyright: Anton Tšepurov, 2013

ISSN 1406-4731

ISBN 978-9949-23-478-3 (publication)

ISBN 978-9949-23-479-0 (PDF)

## INFORMAATIKA JA SÜSTEEMITEHNIKA C87

# Riistvara modelleerimine disaini verifitseerimise ja silumise jaoks

ANTON TŠEPUROV

To my parents Alviina and Nikolai who are responsible for the revival of this thesis

## **Abstract**

Modern hardware design process relies entirely on CAD (Computer-Aided Design) tools. The main difficulties faced today by the EDA (Electronic Design Automation) industry and academia are the enormous scale and complexity of digital designs. This brings to the front the scalability property of design representation models and their ability to represent designs in the most efficient way for the given design task. Despite all the EDA efforts, the design productivity gap persists and manifests designers' inability to harness all that technology allows. Furthermore, verification productivity gap does not allow verification engineers to even ensure a 100% correctness of what yet can be designed.

This thesis contributes to closing these gaps using two powerful design representation models. Designers' productivity is improved through an automated debug method based on a scalable Instantiation Graph (IG) model. Researchers' capabilities are enriched through a scalable IG-based open source platform for hardware design and verification. It offers a solid ground for building other EDA tools and experimental environments. Verification accuracy is further improved through stringent code coverage measurement and fast assertion checking methods based on High-Level Decision Diagrams (HLDD) model and its modifications. If HLDD model suits best for academic research, then IG model is required for experimenting on large industrial designs and has also found industrial application.

First, we present several HLDD model modifications and extensions that target verification accuracy and speed. The thesis includes a methodology for automated generation of behavioral and structural HLDD models from VHDL descriptions. Different HLDD compactness levels are investigated with respect to code coverage measurement accuracy. Certain compactness levels are found to provide more stringent coverage metrics than classical metrics based on hardware description languages (HDLs). Different conditional statements representations by HLDDs are considered: some are found beneficial for condition coverage measurement, others — for automated bug location using statistical methods. The concept of mutation testing on HLDDs is discussed and shown to provide a better estimation of test quality than the code coverage approach. Temporally extended HLDD (THLDD) model is introduced and shown to provide faster verification assertion

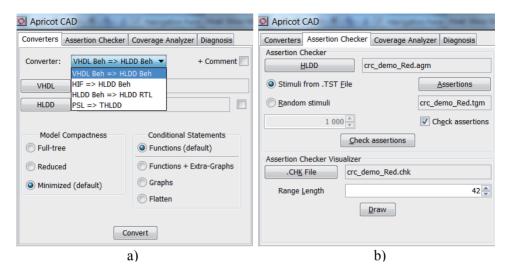

checking than using an HDL-based state-of-the-art assertion checker. Corresponding methodology for THLDD generation from PSL assertions is also provided. Finally, a unified HLDD-based verification framework APRICOT is presented along with its implementation as ApricotCAD.

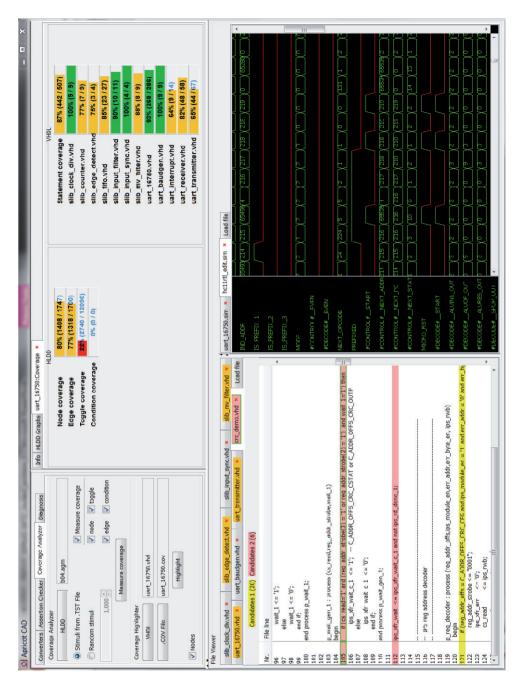

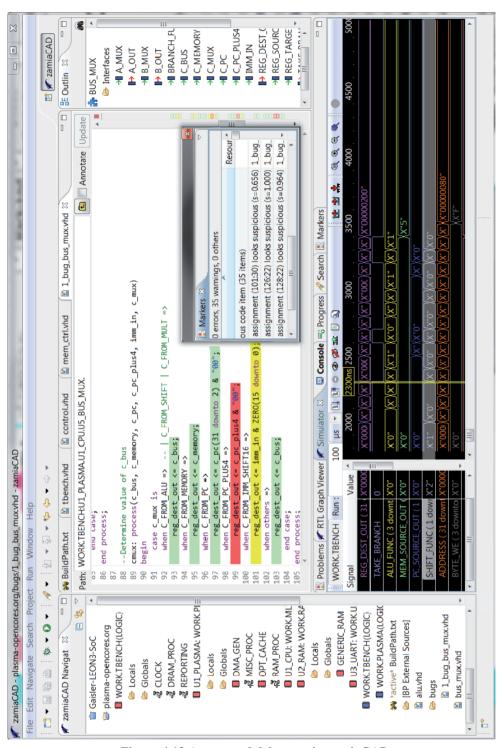

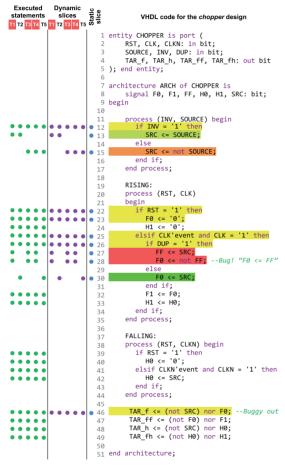

Second, to address the scalability problem unsolved in ApricotCAD, the thesis introduces IG model for scalable design representation and a methodology for comprehensive HDL descriptions elaboration into the IG model. The scalability property of the model is investigated on a system on chip consisting of 3584 LEON3 processor cores, which is far ahead of even tomorrow's scale. zamiaCAD scalable open source platform for design and verification powered by IG model is presented in detail. Tools for static code analysis and VHDL simulation based on zamiaCAD platform are described. Finally, a scalable automated method for precise bug localization in industrial-sized designs is also presented. It uses the both above mentioned tools and is experimentally proven to be particularly useful and accurate in debugging complex conditional statements in large industrial designs of today's scale.

The two proposed models and their derivatives offer wide possibilities for research and industrial application. The models can also be merged together to achieve promising synergic effect discussed shortly in the concluding chapter.

## Kokkuvõte

Kaasaegne riistvaraarendus põhineb täielikult CAD (Computer-Aided Design) vahenditel. Tänapäevaste digitaalsete skeemide ülikõrge suurus ja keerukusaste on saanud põhilisteks raskusteks elektroonika arendus-automatiseerimistööstuse (EAA) ja vastavate teaduslike uuringute jaoks. See tõstab esiplaanile riistvara esitusmudelite skaleeritavusvõimet ja nende täpset sobivust ja efektiivsust riistvara esitusel antud arendusülesande täitmise kontekstis. Vaatamata EAA saavutustele, jätkuvalt säilib arendusvahendite kesisus, mis ei luba arendajatel realiseerida kõike, mida tehnoloogia parasjagu teha lubab. Ega ka verifitseerimisvahendite puudus luba tõestada selle 100% korrektsust, mis ikkagi realiseerida annab.

Antud väitekirja panuseks ongi nende kahe puuduse kõrvaldamine läbi kahe võimsa riistvara esitusmudeli kaasamise. Arendajate tootlikkus suurendatakse automaatse silumismeetodiga, mis põhineb hästi skaleeritaval eksemplar graaf (EG) mudelil. Uurijate võimalusi samuti rikastatakse läbi avatud lähtekoodiga riistvara arendamiseks ja verifitseerimiseks mõeldud laiendatava EG-põhise platvormi. Selle põhjal annab luua teisi EAA vahendeid ja skaleeritavaid eksperimentaalseid keskkondasid. Suurem täpsus ja kindlus verifitseerimisel saavutatakse range koodikatte mõõtmise ja kiire väidete kontrolli meetoditega, mis põhinevad kõrgtaseme otsustusdiagrammide (KTOD) mudelil ja selle laienditel. Kui KTOD mudel on eriti sobilik akadeemiliste uuringute läbiviimiseks, siis EG mudel on vajalik, et teha katseid suurte skeemidega, ja seega on leidnud rakendust tööstuses.

Esiteks me esitame mitmeid KTOD mudeli modifikatsioone ja laiendeid täpsuse ja kiiruse tõstmiseks verifitseerimisel. Väitekirjas tuuakse metodoloogia käitumuslike ja struktuursete KTOD mudelite automaatseks genereerimiseks VHDL kirjeldustest. Käsitletakse erinevaid KTOD kompaktsustasemeid. On leitud, et mõned neist annavad rangema koodikatte mõõtmise tulemuse võrreldes klassikaliste riistvara kirjelduskeeltel (RKK) põhinevate meetrikatega. Erinevad tingimuslausete esitusviisid on vaadeldud: mõned on osutunud kasulikeks tingimuskatte mõõtmiseks, teised — automaatseks vigade avastamiseks statistiliste meetoditega. On uuritud mutatsioontestimist KTOD mudeli peal ja see on osutunud koodikatte mõõtmisest veelgi paremaks testi kvaliteedi hindajaks. Ajalise laiendiga

KTOD (AKTOD) mudel on esitatud ja saavutavat kiirema väidete kontrolli kui lubab kaasaegne RKK-põhine väidete kontrollija. Vastav metodoloogia AKTOD genereerimiseks PSL väidetest on samuti lisatud. Lõpuks esitatakse ühtne KTOD-põhine verifitseerimiskeskkond APRICOT koos seda realiseeriva ApricotCAD rakendusega.

Teiseks, et pakkuda lahendust skaleerimise probleemile, mis jäi ApricotCADis lahendamata, väitekiri esitab EG mudeli skaleeritavaks disaini esituseks ja vastava metodoloogia selle mudeli saamiseks läbi põhjaliku RKK kirjelduste teisendamise. Mudeli skaleeritavusvõime hindamiseks kasutatakse 3584 LEON3 protsessor tuumast koosnevat kiipsüsteemi, mis vastab isegi kaugema kui homse päeva tööstuslikule ulatusele. Järgmisena esitatakse avatud lähtekoodiga skaleeritav zamiaCAD platvorm, mis põhineb EG mudelil ja on mõeldud riistvara arendamise ja verifitseerimise hõlbustamiseks. Kirjeldatud on kaks zamiaCAD põhjal loodud rakendust, millisteks on staatiline koodi analüsaator ja RKK VHDL kirjelduste simulaator. Lõpuks ka avaldatakse skaleeritav silumismeetod täpseks ja automaatseks disainivigade lokaliseerimiseks, milles kasutatakse mõlemat ülalmainitud rakendust. Järgnevas eksperimentaalses osas näidatakse meetodi erilist efektiivsust ja täpsust vigade avastamisel keerulistes tingimuslausetes ja selliste disainide suuruste puhul, mis vastavad tänapäeva tööstuslikule ulatusele.

Pakutud mudelid koos nende laienditega ja neist tuletatud teiste mudelitega on heaks aluseks laiale hulgale teaduslikele uuringutele ja ka tööstuses kasutamiseks. Ka mudelite kokkuviimine annab saavutada paljulubavat sünergilist efekti, mida arutatakse lühidalt väitekirja viimases peatükis.

# Acknowledgements

I only have one chance to thank everyone who has contributed to this thesis, so here I take it.

First and foremost, I would like these leaves to constantly deliver words of gratitude to Prof. Raimund-Johannes Ubar, Prof. Jaan Raik and Dr. Margus Kruus. It is for the professional work of your team that I had been attracted to scientific research in the first place, supported diligently throughout my stay and had a chance to contribute and meet the top players in the field, both at the international conferences and here, in Tallinn. Your Teamwork is outstanding!

This work of mine would never exist without the generous advice and guidance of my supervisors Dr. Maksim Jenihhin and Prof. Jaan Raik. You have endowed me with a frame of reference for what the intense and fruitful teamwork should be like. You have taught me that hypotheses are nets: only he who casts will catch. And that to achieve a lot, one must do a lot. You were the Super-Wisers!

During the years, Günter Bartsch has shown me what it is to be a true engineer. The mastermind behind zamiaCAD, its founder and a brilliant versatile engineer, you have virtually shaped and inspired a half of this thesis. Herein I express my deepest gratitude to you and my anticipation of further collaboration. I would also like to thank Rainer Dorsch for all your valuable contributions and particularly for arranging our acquaintance with Günter Bartsch. You both played quite a Role!

I am also happy to have a pleasure of bringing up the rear of PhD defenses of the four close friends who have once started their BSc studies together: Dr. Anton Tšertov, Dr. Sergei Kostin and Dr. Igor Aleksejev. There was always more than just studies. While writing this thesis, I was constantly looking back at your own, fellows, work to make sure I remain on a par. We shall never forget that environment creates a man. And a man creates the Environment.

Dedicated gratitude goes to all the organizations that supported my PhD studies: Tallinn University of Technology, European Commission FP6 research project VERTIGO, European Commission FP7 research project DIAMOND, Centre of Research Excellence in Dependable Embedded Systems (CREDES), National Graduate School in Information and Communication Technologies (IKTDK) and

Estonian IT Foundation (EITSA). It is for your Support that new generations of researchers and citizens can concentrate on learning about the mistakes of the past and the experience of the past, so that the former would not be repeated, while the latter would be employed to the fullest extent possible.

Here I want it to be explicitly stated that it is not what I have learned that I value most, but the people I got acquainted with and the processes I observed during my stay at TUT.

Last but not least, I bring here my warmest thanks to my family who are at the core of my Universe, even if not always obvious. Alviina, Nikolai, Kirill, all I do is ultimately for you to be proud of. You are the endless source of Inspiration and Wisdom! And there were days when I did not Exist at all, to say nothing of the thesis

It is also not a tradition to thank your beloved, but a great desire, a pleasant duty and an inevitable felicity one cannot help. I would love to thank my dear fiancée Olga for all your mildness and love, encouragement and help, which made my days both easier and brighter. You are my All!

Thank you!

Anton Tšepurov Tallinn, May 2013

## **List of Publications**

- V. Tihhomirov, A. Tšepurov, M. Jenihhin, J. Raik, R. Ubar, "Assessment of Diagnostic Test for Automated Bug Localization", *14th Latin American Test Workshop (LATW'13)*, April 3–5, 2013, Cordoba, Argentina, pp. 1–6.

- M. Jenihhin, A. Tšepurov, V. Tihhomirov, J. Raik, H. Hantson, R. Ubar, G. Bartsch, J. H. Meza Escobar, H. D. Wuttke, "Automated Bug Localization in Processor Designs", *IEEE Design & Test of Computers Magazine*, 2013, [Accepted].

- J. Raik, U. Repinski, A. Tšepurov, H. Hantson, R. Ubar, M. Jenihhin, "Automated design error debug using high-level decision diagrams and mutation operators", *Microprocessors and Microsystems Journal*, 2013, 37(4), pp. 1–10.

- A. Tšepurov, V. Tihhomirov, M. Jenihhin, J. Raik, G. Bartsch, J.-H. Meza Escobar, H.-D. Wuttke, "Localization of Bugs in Processor Designs Using zamiaCAD Framework", *Microprocessor Test and Verification (MTV'12)*, December 10–12, 2012, Austin, Texas, USA, pp. 1–6.

- A. Tšepurov, G. Bartsch, R. Dorsch, M. Jenihhin, J. Raik, V. Tihhomirov, "A Scalable Model Based RTL Framework zamiaCAD for Static Analysis". IFIP/IEEE 20th International Conference on VLSI and System-on-Chip (VLSI-SoC), October 7-10, 2012, Santa Cruz, USA, pp. 171–176.

- J. Raik, T. Drenkhan, M. Jenihhin, T. Viilukas, A. Karputkin, A. Tšepurov, R. Ubar, "Generating Directed Tests for C Programs using RTL ATPG", *Proceedings of the IEEE 13th Workshop on RTL and High Level Testing (WRTLT'12)*, Niigata, Japan, November 22-23, 2012, pp. 1–6.

- J. Raik, U. Repinski, M. Jenihhin, A. Chepurov, "High-Level Decision Diagram Simulation for Diagnosis and Soft-Error Analysis". *Book chapter in "Design and Test Technology for Dependable Systems-on-Chip", Information Science Reference (IGI Global), Ed. R. Ubar,* USA, 2011, pp. 294–309.

- M. Jenihhin, J. Raik, A. Chepurov, R. Ubar, "Application of High-Level Decision Diagrams for Simulation-Based Verification tasks". *Estonian Journal of Engineering*, 2010, 16(1), pp. 56–77.

- J. Raik, U. Repinski, R. Ubar, M. Jenihhin, A. Chepurov, "High-level design error diagnosis using backtrace on decision diagrams". *28th Norchip Conference (NORCHIP'10)*, November 15-16, 2010, Tampere, Finland, pp. 1–4.

- H. Hantson, J. Raik, G. Di Guglielmo, M. Jenihhin, A. Chepurov, F. Fummi, R. Ubar, "Mutation Analysis with High-Level Decision Diagrams". *11th Latin-American Test Workshop (LATW'10)*, March 28-31, 2010, Punta del Este, Uruguay. IEEE Computer Society Press, pp. 1–6.

- R. Ubar, A. Jutman, J. Raik, S. Devadze, I. Aleksejev, A. Chepurov, A. Chertov, S. Kostin, E. Orasson, H.-D. Wuttke, "E-Learning Environment for WEB-Based Study of Testing". *Proc. of the 8th European Workshop on Microelectronics Education (EWME'10)*. Darmstadt, Germany, pp. 47–52.

- M. Jenihhin, J. Raik, A. Chepurov, R. Ubar, "PSL Assertion-Checking Using Temporally Extended High-Level Decision Diagrams". *Journal of Electronic Testing Theory and Applications (JETTA)*, 25(6), 2009, pp. 289–300.

- M. Jenihhin, R. Raik, A. Chepurov, U. Reinsalu, R. Ubar, "High-Level Decision Diagrams based Coverage Metrics for Verification and Test". Proceedings of 10th IEEE Latin American Test Workshop (LATW'09), 2009, pp. 1–6.

- M. Jenihhin, J. Raik, A. Chepurov, U. Reinsalu, R. Ubar, "Code Coverage Analysis for Concurrent Programming Languages Using High-Level Decision Diagrams". *Proceedings of the 12th European Workshop on Dependable Computing (EWDC'09)*, May 14-15, 2009, Toulouse, France, pp. 1–4.

- M. Jenihhin, J. Raik, A. Chepurov, R. Ubar, "Simulation-based Verification with APRICOT Framework using High-Level Decision Diagrams". *East-West Design & Test Symposium (EWDTS'09)*, September 18-21, 2009, Moscow, pp. 13–16.

- J. Raik, M. Jenihhin, A. Chepurov, U. Reinsalu, R. Ubar, "APRICOT: a Framework for Teaching Digital Systems Verification". *19th EAEEIE Annual Conference*, 2008, pp. 172–177.

- A. Chepurov, G. Di Guglielmo, F. Fummi, G. Pravadelli, J. Raik, R. Ubar, T. Viilukas, "Automatic Generation of EFSMs and HLDDs for Functional ATPG". *11th Biennial Baltic Electronics Conference (BEC'08)*, 2008, pp. 143–146.

- M. Jenihhin, J. Raik, R. Ubar, A. Chepurov, "On reusability of verification assertions for testing". *11th Biennial Baltic Electronics Conference (BEC'08)*, 2008, pp. 151–154.

- K. Minakova, U. Reinsalu, A. Chepurov, J. Raik, M. Jenihhin, R. Ubar, P. Ellervee, "High-Level Decision Diagram Manipulations for Code Coverage Analysis". *11th Biennial Baltic Electronics Conference (BEC'08)*, 2008, Tallinn, Estonia, pp. 207–210.

- A. Jutman, A. Tsertov, A. Tsepurov, I. Aleksejev, R. Ubar, H.-D. Wuttke, "Teaching Digital Test with BIST Analyzer". *19th EAEEIE Annual Conference*, June 29 July 2, 2008, Tallinn, Estonia, pp. 123–128.

- M. Jenihhin, J. Raik, A. Chepurov, R. Ubar, "Temporally Extended High-Level Decision Diagrams for PSL Assertions Simulation". *Proceedings of the 13th IEEE European Test Symposium (ETS'08)*, 2008, Los Alamitos, USA. IEEE Computer Society Press, pp. 61–68.

- J. Raik, R. Ubar, M. Jenihhin, A. Chepurov, "PSL Assertion Checking with Temporally Extended High-Level Decision Diagrams". 9th IEEE Latin American Test Workshop (LATW'08), February 17-20, 2008, Puebla, Mexico, pp. 49–54.

- M. Jenihhin, J. Raik, A. Chepurov, R. Ubar, "Assertion Checking with PSL and High-Level Decision Diagrams". *Proceedings of the IEEE 8th Workshop on RTL and High Level Testing (WRTLT'07)*, 2007, Beijing, China, IEEE Computer Society Press.

- A. Jutman, A. Tsertov, A. Tsepurov, I. Aleksejev, R. Ubar, H.-D. Wuttke, "BIST Analyzer: a Training Platform for SoC Testing". Frontiers In Education Conference Global Engineering: Knowledge Without Borders, Opportunities Without Passports, 2007. 37th Annual Frontiers in Education Conference (FIE'07), October 10-13, 2007, Milwaukee, USA. IEEE Computer Society Press, pp. 1534–1539.

- V. Tihhomirov, A. Chepurov, S. S. Abrar, M. Jenihhin, J. Raik, "VHDL Design Debug Framework Based on zamiaCAD". *In University Booth section of Design, Automation and Test in Europe*, Grenoble, France, March 18-22, 2013. p. 1.

- A. Chepurov, V. Tihhomirov, S. A. Syed, M. Jenihhin, J. Raik, "Applications of the Open Source HW Design Framework zamiaCAD". *In University Booth section of Design, Automation and Test in Europe (DATE'12)*, March 12-16, 2012, Dresden, Germany, p. 1.

- A. Tsepurov, M. Jenihhin, J. Raik, "zamiaCAD: Open Source Platform for Advanced Hardware Design". *In University Booth section of Design, Automation and Test in Europe (DATE'11)*, March 14-18, 2011, Grenoble, France, pp. 1–2.

- A. Tsepurov, M. Jenihhin, J. Raik, "Simulator for ZamiaCAD Integrated Hardware Design Environment". *In University Booth section of Design, Automation and Test in Europe (DATE'10)*, March 8-12, 2010, Dresden, Germany, pp. 1–2.

- A. Chepurov, "Interface between VHDL and High-level Decision Diagram model descriptions", Master thesis, Tallinn University of Technology, Tallinn, June 2008, pp. 1–74.

- A. Chepurov, "Hybrid BIST Cost Visualization Tool", Bachelor thesis, Tallinn University of Technology, Tallinn, June 2006, pp. 1–34.

(30 publications in total)

# **List of Abbreviations**

ABS Anti-lock Braking System

ADD Assignment Decision Diagram

ASIC Application-Specific Integrated Circuit

ASM Algorithmic State Machine

AST Abstract Syntax Tree

BDD Binary Decision Diagram

CAD Computer-Aided Design

CPU Central Processing Unit

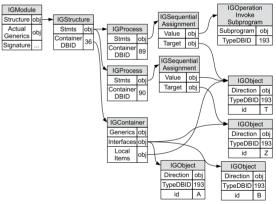

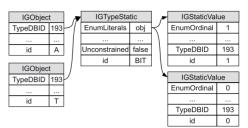

DBID Database Identifier

DD Decision Diagram

DUV Design Under Verification

EDA Electronic Design Automation

EFSM Extended Finite State Machine

EHM Extensible Hash Map FSM Finite State Machine

FSMD Finite State Machine with a Datapath

GRLIB Gaisler Research Library

GUI Graphical User Interface

HDL Hardware Description Language

HIF HDL Intermediate Format

HLDD High-Level Decision Diagram

IBM International Business Machines

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

IG Instantiation GraphIP Intellectual property

ISA Instruction Set Architecture

ITC International Test Conference

MIPS Microprocessor without Interlocked Pipeline Stages

OOM Out Of Memory

OS-VVM Open Source VHDL Verification Methodology

PC Program Counter

PPG Primitive Property Graphs

PSL Property Specification Language

RAM Random Access Memory

RISC Reduced Instruction Set Computer

RO-BDD Reduced Ordered Binary Decision Diagrams

RT Register Transfer

RTL Register-Transfer Level

SAT Satisfiability Problem

SISD Single Instruction Single Data

SMT Satisfiability Modulo Theories

SoC System-on-Chip

SSBDD Structurally Synthesized Binary Decision Diagram

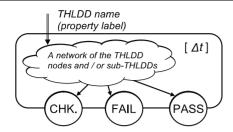

THLDD Temporally Extended High-Level Decision Diagram

TLM Transaction Level Modeling

TUT Tallinn University of Technology

VHDL VHSIC Hardware Description Language

VHSIC Very-High-Speed Integrated Circuits

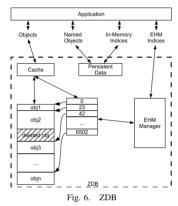

ZDB zamiaCAD Database

# **Contents**

| CHAPTER 1 INTRODUCTION                                      | 21 |

|-------------------------------------------------------------|----|

| 1.1 Motivation                                              | 21 |

| 1.2 Objectives                                              | 23 |

| 1.3 Problem formulation                                     | 24 |

| 1.4 Contributions                                           | 24 |

| 1.5 Thesis structure                                        | 25 |

| CHAPTER 2 BACKGROUND                                        | 27 |

| 2.1 Hardware design flow                                    | 27 |

| 2.1.1 Abstraction levels                                    | 29 |

| 2.2 Hardware modeling with HDLs                             | 30 |

| 2.2.1 VHDL                                                  | 31 |

| 2.2.2 HDLs for verification and debug                       |    |

| 2.3 State-of-the-art models in hardware design and EDA      | 32 |

| 2.3.1 Exploitation of models in industry                    |    |

| 2.3.2 Formal models in research                             | 35 |

| 2.4 HLDD model preliminaries                                | 36 |

| 2.4.1 HLDD model definition                                 |    |

| 2.4.2 Simulation on HLDDs at RTL                            |    |

| 2.5 Summary                                                 | 40 |

| CHAPTER 3 HARDWARE MODELING WITH HIGH-LEVEL                 |    |

| DECISION DIAGRAMS                                           |    |

| 3.1 HLDD generation                                         |    |

| 3.1.1 Handling of hierarchical designs                      |    |

| 3.1.2 Handling of slices and sub-elements                   |    |

| 3.1.3 Handling of memories                                  |    |

| 3.2 Application specific HLDD models                        |    |

| 3.2.1 HLDD for test generation at RTL                       |    |

| 3.2.2 HLDD for code coverage analysis                       |    |

| 3.2.2.1 Compactness levels of HLDD model                    |    |

| 3.2.2.2 Condition coverage measurement                      |    |

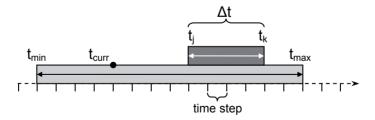

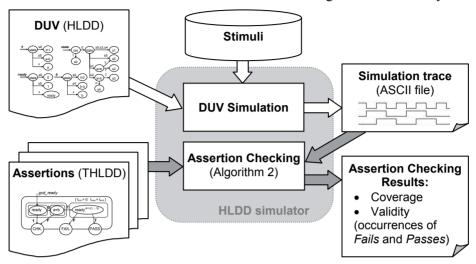

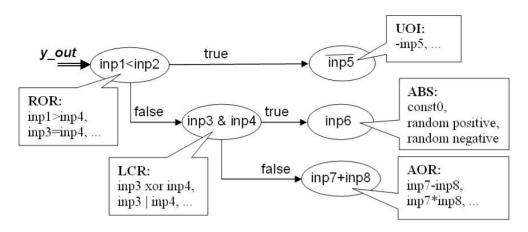

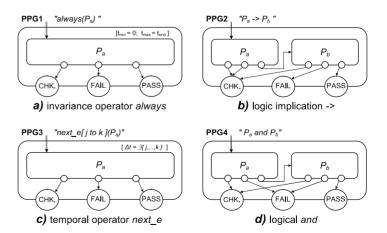

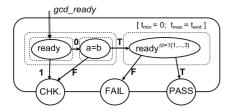

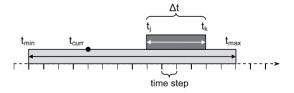

| 3.2.3 Temporally extended HLDD model for assertion checking | 55 |

| 3.2.3.1 Basic definitions                                       | 55  |

|-----------------------------------------------------------------|-----|

| 3.2.3.2 Recursive generation of THLDDs using Primitive Property |     |

| Graphs                                                          | 57  |

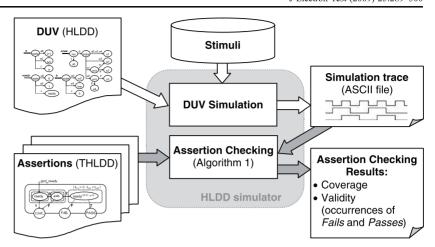

| 3.2.3.3 Assertion checking using THLDDs                         | 59  |

| 3.2.4 HLDD for debug                                            | 61  |

| 3.2.5 HLDD for mutation testing                                 | 63  |

| 3.3 APRICOT verification framework                              | 65  |

| 3.4 Summary                                                     | 71  |

| CHAPTER 4 HARDWARE MODELING WITH INSTANTIATION                  |     |

| GRAPHS                                                          |     |

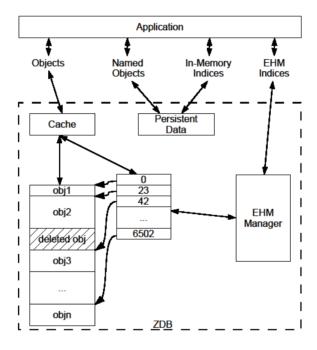

| 4.1 Overview of zamiaCAD framework                              |     |

| 4.1.1 Framework flow                                            | 75  |

| 4.1.2 Persistence and scalability                               |     |

| 4.2 AST model and its limitations                               |     |

| 4.2.1 Applications of AST model                                 | 81  |

| 4.3 IG model                                                    | 81  |

| 4.3.1 Modules in IG                                             | 82  |

| 4.3.2 Objects, types and expressions in IG                      |     |

| 4.4 Application of IG model to verification and debug           |     |

| 4.4.1 Static analysis                                           | 85  |

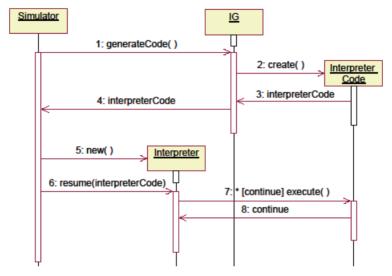

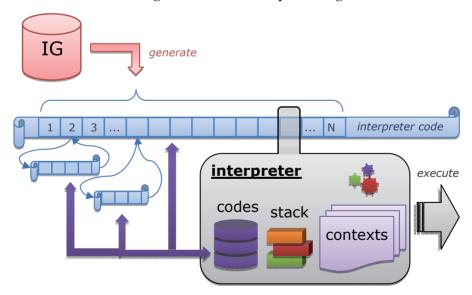

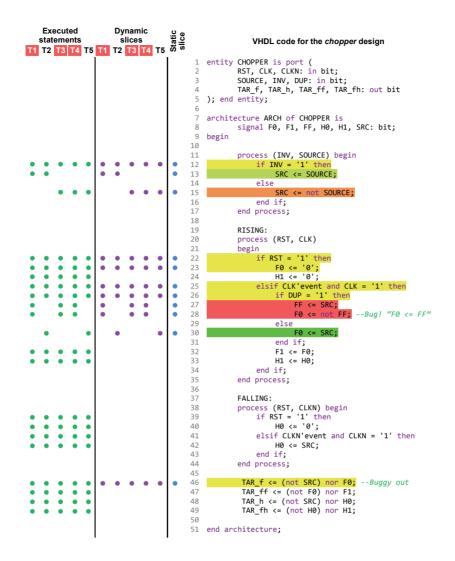

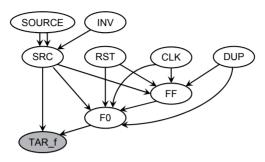

| 4.4.2 Simulation                                                | 87  |

| 4.5 Scalability assessment                                      |     |

| 4.6 Debug                                                       | 92  |

| 4.6.1 Bug localization with zamiaCAD                            | 93  |

| 4.6.1.1 Static slicing                                          | 95  |

| 4.6.1.2 Suspiciousness ranking based on statement and branch    |     |

| coverage metrics                                                |     |

| 4.6.1.3 Hierarchical analysis based on condition coverage       |     |

| 4.6.2 Case study                                                |     |

| 4.6.2.1 ROBSY processor: functional test                        |     |

| 4.6.2.2 Set of documented design errors                         |     |

| 4.6.3 Details of automated bug localization                     |     |

| 4.7 Summary                                                     |     |

| CHAPTER 5 CONCLUSIONS                                           |     |

| 5.1 Contributions                                               | 105 |

| 5.2 Future work                                                 |     |

| REFERENCES                                                      |     |

| CURRICULUM VITAE                                                |     |

| ELULOOKIRJELDUS                                                 |     |

| APPENDIX                                                        | 123 |

# Chapter 1

## **INTRODUCTION**

Modeling is indispensable in science and engineering. The purpose of modeling is to develop a concept and to analyze it through experimenting on it and measuring its properties. Verification of a concept is also an important goal of modeling as it allows correcting the inevitable mistakes on the conceptual level before approaching the real world and (in case of hardware) producing actual physical implementations of the concept.

In this thesis we will contemplate *hardware modeling* with a particular emphasis on those modeling techniques that improve the *quality* of the hardware produced and *speed up* the overall process of product development. In hardware design, the quality is guaranteed by comprehensive verification and testing, while the speed-up is achieved through automation and acceleration of design phases.

### 1.1 Motivation

The impact of embedded and consumer electronics on our life has been so profound we often take it for granted. We proclaim mobile access to the Internet one of our basic human rights. We get angry when our flight is delayed having no idea of how complex the hardware is that ensures our safety when on board. And we never expect the ABS system to fail in our car. Advances in feature scaling have also led to the situation when a dozen of appliances from the 90's are squeezed into a single smartphone of the 00's and it still fits into a pocket. When many were placing their orders for a new 4G phone, only few were listening to the complaints of Ericsson designers how it is next to impossible to debug a 4G cellular router. While many think building such complex hardware is as simple as putting together several Lego blocks, it is way far from that.

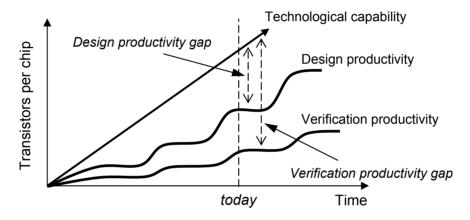

To build today's hardware systems we need the finest production technology and computer-aided design (CAD) tools to harness it. While many design steps are well automated already, we still face the *design productivity gap*, as well as *verification productivity gap* (Figure 1.1). The latter is there for two reasons. First, historically the main focus of CAD research was on automating the design step only. Secondly, the complexity of the verification task itself is much higher than design task complexity [1] with verification reported to occupy between 60% and 80% of design effort [2]. What adds to the importance of verification is the constantly increasing requirements towards the *quality* of verification [3], [4]. The quality requirements are stringent for the hardware systems have become ubiquitous today and even have made it into the many life-critical systems such as mentioned above. That is why, for every designer, the number of verification engineers may vary today from 2 to 4 depending on the design complexity.

Figure 1.1 Productivity gaps

The *reuse* of pre-designed components is a widespread practice in engineering. While CAD tools allow composing enormous circuits out of smaller ones, the correctness of the resulting system still remains hard to guarantee. In 1996 a highly expensive Ariane 5 payload delivery rocket self-destructed just 37 seconds after the launch, because the control unit reused from Ariane 4 was not verified enough to meet the Ariane 5 specification and proved unable to handle Ariane 5's higher acceleration [5]. Pentium FDIV bug is another example of insufficient verification, which presumably cost Intel \$475 million in total [6]. This motivates the creation of more stringent verification metrics and new means of revealing potentially erroneous places in the hardware — all attended closely in this thesis. Choosing the right model for representing hardware during verification in this case is as important as developing the proper algorithms that make use of the model.

Design productivity gap is caused by the weak handling of legacy designs, which are the bottleneck in simulation and verification of the entire system, and by the lack of certain automation. Despite the myth that design process is a single linear pass, it is in fact iterative and suffers most from its least automated phases.

Debug automation is one of such weakest phases. Also, because design is not just a top-down process, but requires both horizontal and vertical feature exploration by the team, re-design is very costly and particularly costly if done late in the process. And absolutely costly if a bug is discovered after the manufacturing, because, contrary to software bugs, hardware bugs cannot be patched. Given the ever more frequent application of embedded systems in the medical domain, bugs can even prove fatal [7].

It is therefore of the highest priority to further raise the quality of hardware through improved *verification accuracy* and to find ways of reducing the cost of development in terms of time and money by e.g. speeding up the *debug* step.

The main problem with today's scientific debug methods is that they rarely take the real life conditions and limitations into consideration. Not only do they scale bad, but they often ask for the availability of a *golden model* normally used in testing and obviously being a legacy thereof. This requirement does not have to be explicitly stated, but more often than not it is deducible from phrases like "It is required that the specification include the expected value of the condition expression" [8], "These dependences are compared with pre-specified dependences" [9] etc. Such phrases reveal that authors forget that during debug we are just in the process of obtaining such a fine-grained specification which, once achieved, will be called an implementation. By definition, the specification conveys information in different notions from those of the implementation and hence never mentions the internal signals and conditions. This can be translated into a "No Golden Model" rule often ignored for simplicity when adopting good old testing methods for the task of debug without thorough consideration.

Satisfying the scalability property is also not a trivial task. It leads to the situation where, on one hand, scientific methods are expected to scale well, but, on the other hand, development of a scalable and robust experimental platform is too hard of an intermediate task. Efficiency of new approaches is often only verified on small designs which have nothing to do with the huge industrial designs.

## 1.2 Objectives

In the previous section we have motivated the importance of raising the quality of verification and further automating the design process, e.g. its debug phase. To meet the demand, the related research should aim at the following objectives:

- Industry needs *efficient* and *accurate verification techniques* to catch all the design bugs before costly or catastrophic effects occur. Such techniques would help closing the verification productivity gap.

- Industry needs *scalable debug automation* to faster locate and correct bugs in designs of current scale. Automation of this frequently repeated design step would help closing the design productivity gap.

• Academia needs an *efficient scalable basis or environment* for carrying out research without ignoring the real life conditions and limitations.

### 1.3 Problem formulation

To reach the objectives formulated in the previous section, in this thesis we are solving the following specific problems:

- Fast and more accurate verification.

- Fast and scalable automated debug.

- A scalable design environment.

We want to improve the verification accuracy by modeling hardware in a way which is verification-friendly because it allows a fine-grained analysis of hardware descriptions expressed in popular hardware description languages (HDLs). We achieve this by extending the High-Level Decision Diagrams (HLDDs) hardware representation model towards stringent HDL code coverage measurement. Another extension introduces a temporal aspect to the HLDD model and allows us to verify design functionality using verification assertions in a fast and accurate way.

To automate the debug process and support the scale of today's designs we introduce the Instantiation Graph (IG) design representation model. We also provide a scalable debug method which employs the IG model and is particularly efficient in detecting bugs in complex conditional statements of HDL code.

Our final goal is also to publish the theory and the important details of HDL description elaboration into the scalable IG model and provide its working implementation as a scalable zamiaCAD platform. We also provide examples of how IG model can be efficiently used both in academic research and in industry.

### 1.4 Contributions

Below we list the main contributions of this thesis.

# HLDD model modifications and extensions for improved verification and debug

- A methodology for automated generation of behavioral HLDD model from a wide subset of VHDL language and structural HLDD model synthesis from behavioral HLDD. *Implementation* of the two methodologies is included.

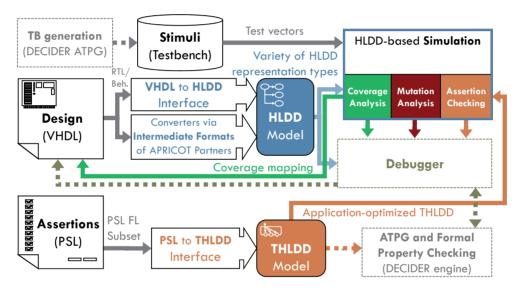

- HLDD model extensions and modifications for accurate code coverage measurement, fast PSL assertion checking (using THLDD model), mutation testing and automated debug. Modifications include different compactness levels of HLDD model, different representation of conditional statements

- and a temporal extension of HLDD model (THLDD). A *methodology and implementation of THLDD generation* from PSL properties are included.

- A unified HLDD-based verification framework APRICOT and its implementation as ApricotCAD tool where all HLDD engines are integrated into a single flow.

## IG model introduction for scalable debug and verification related research

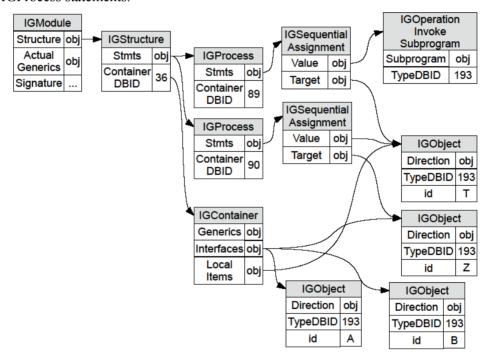

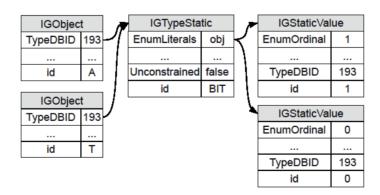

- Introduction of a methodology for HDL descriptions elaboration into a scalable IG model.

- Presentation of the IG-based design and verification platform zamiaCAD well suitable for academic research and industrial use.

- A scalable automated debug method based on IG model and its implementation inside zamiaCAD platform.

### 1.5 Thesis structure

The rest of this thesis is organized as follows.

Chapter 2 contains background information about the contemporary hardware modeling techniques. The typical design flow is described first and the shortcomings of modeling hardware with HDLs are mentioned. Next, a number of application-specific models is discussed, both from industry and from academia. Finally, the background of HLDD model is described.

Chapter 3 is devoted to HLDD-based hardware modeling approaches. It starts by listing the most interesting aspects of the methodology for behavioral HLDD generation from HDL descriptions. The concept of structural HLDD synthesis is mentioned in the section devoted to test generation using HLDDs. Then a list of application-specific modifications and extensions of HLDD model follows. Different compactness levels of the HLDD model and various condition representations are discussed in frames of code coverage measurement. Temporally extended HLDDs are discussed in detail in the context of fast assertion checking. Finally, HLDD-based mutation testing and its application for high-level debug are considered. A dedicated section about APRICOT framework and ApricotCAD tool concludes this chapter.

Chapter 4 is completely devoted to the scalable IG hardware representation model, its elaboration process and application of this model to the task of debug. zamiaCAD platform which implements the IG model is described first. Then the concept of comprehensive HDL elaboration into IG model is discussed and experimental data provided so that the scalability level could be assessed. The details of convenient use of IG for simulation and static analysis are delivered along with a detailed explanation of the scalable and accurate debug approach.

Chapter 5 draws conclusions from the thesis and outlines the directions for future work.

### Remark:

Throughout the thesis we use  $[ref]^{\text{co-auth}}$  and  $[ref]^{\text{auth}}$  superscript suffixes to distinguish co-authored and authored work from the rest of the referenced work.

# Chapter 2

## **BACKGROUND**

In this chapter, we describe the typical process of hardware development and the approaches used for modeling hardware at different stages of this process. We provide a short overview of hardware models employed in academia and stress the problems of modeling hardware of industrial scale. This background information helps for better understanding of the role of verification and debug phases of hardware design we address in this thesis and the models used during these phases.

Since a half of this thesis is devoted to extending high-level decision diagrams model of hardware representation to the area of verification and debug, we also provide in this chapter a detailed description of this model.

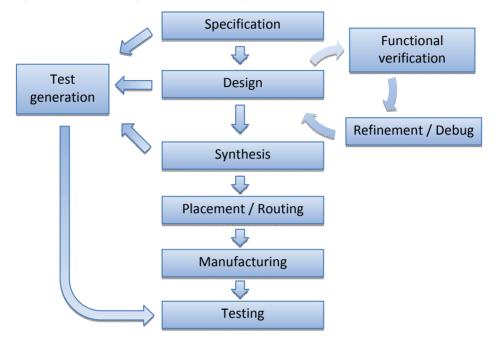

## 2.1 Hardware design flow

Let us consider a typical yet simplified hardware design flow depicted in Figure 2.1. The engineering part of hardware product development starts with composing the *specification* of product requirements in a natural language and setting up the constraints for timing, energy consumption, available chip area etc. Initial high-level *design model* is captured next as an executable behavioral description written in a hardware description language (HDL) or as a software program. This description gets then *verified* against the initial specification to make sure the latter is met. From this moment on, the design model gets decomposed recursively into a structure of lower-level models. This hierarchical *refinement* continues until the lowest level of abstraction is achieved, where the obtained models correspond to the components from the given library of available building blocks. If the product is a soft intellectual property (IP) core, then refinement is stopped when the

required technology independent level is achieved. During this refinement (either manual or using synthesis tools), the obtained models are constantly verified against the source model they were obtained from to make sure the initial functionality is preserved. Importantly, while descending through the levels of abstraction, new details become available and new properties become measurable (e.g. precise timing delays). This way different design properties and design compliance with the imposed constraints get verified.

Figure 2.1 Simplified hardware design flow

To verify a model, two types of functional verification can be considered: formal verification (e.g. theorem proving, algebraic manipulation, symbolic computation) [10] and simulation-based verification [11]. Although formal verification allows proving the equality of two different models of the same design for all possible sets of input values, in practice it can only be applied to small designs because of the task complexity. The industry hence usually resorts to simulation when verifying today's large models due to its realistic runtime. The obvious drawback of simulation is that it can exercise the model with only a limited set of input stimuli. However, the same holds for the formal property checking which is limited to the set of actual properties. Therefore, with simulation just as with formal verification, it is of the utmost importance to develop a decent verification plan which would guide the verification process by accurately specifying what exactly, how and to what extent should be checked to ensure model correctness. It is also the main goal of this thesis: to improve the quality of

verification process and to help with the process of *debug* that follows right after a trouble has been identified during verification.

The *synthesis* step is no more than an automated model refinement which converts behavioral descriptions (of any abstraction level) into structural ones containing components from a given library [12]. One or several physical parameters can be optimized during synthesis, e.g. by minimizing the number of components, chip size, execution time, propagation delay, power consumption etc. While sometimes considered a part of the synthesis step, *placement and routing* are left stand-alone in our case so as to stress how synthesis is more concerned about the semantics of conversion. Placement and routing, on the contrary, are involved in the minimization of wire lengths, signal delays and the total chip area. This step produces a blueprint of the circuit used for circuit's *manufacturing* at the factory.

Finally, every single chip produced at the factory must be *tested* against manufacturing defects. To obtain good quality tests a *test generation* phase is required where information from specification and design models is employed. Thesis contributions to this phase will be discussed in sub-section 3.2.1.

### 2.1.1 Abstraction levels

When modeling hardware, several design representations or views, such as behavioral, structural and physical, are used to emphasize different information about a design. Different representations are used at different stages of the design process. First, behavioral view is used to conveniently describe required functionality of the design. Structural view is then used to describe the way to build or implement this functionality with the given components (transistors). The resulting layout of components and their physical properties are finally described using physical view. Although to manufacture a chip only structural and physical descriptions are needed, the required functionality is much easier and more convenient to be specified using behavioral descriptions, which are also easier to read and comprehend afterwards. Because of that, the process of converting behavioral descriptions into structural was automated and called synthesis [12].

These three different design views may be used at any of the four levels of abstraction or granularity: algorithmic level, register-transfer level (RTL), gate level and transistor level. Abstraction levels are defined by the type of objects they use as structural components. Transistor level uses transistors, resistors and capacitors to represent structure, and differential equations or other types of current-voltage relationships to represent functional behavior. Gate level uses logic gates and flip-flops as structural components described behaviorally with Boolean equations and finite state machines (FSMs). RTL operates with arithmetic and memory units such as adders, comparators, multipliers, counters, registers and multiplexers, and uses flowcharts, instruction sets, generalized FSMs and algorithms to describe the functionality of components when combined together. Finally, the algorithmic level uses processors, memories, controllers and

application-specific integrated circuits (ASICs) which, when combined together as a system, are described behaviorally in a natural language, in an HDL as an executable specification or as a software program.

The design flow depicted in Figure 2.1 goes through all the levels of abstraction from the algorithmic down to the transistor level when going from specification to placement and routing. The design process typically consists of defining/building a library for a certain abstraction level and using synthesis (manual or automated) to convert a behavioral description into a structure that can be implemented with the components from this library [12]. A list of high-level synthesis tools exist that accept algorithmic level of abstraction as an input specification and produce RTL descriptions [13], [14], [15] suitable for well-established RTL synthesis.

At highest levels of abstraction (e.g. algorithmic or system level) the interest lies in modeling interaction between entire processors and ASICs. Transaction-Level Modeling (TLM) [16] helps modeling communication among modules using the concepts of channels (for media) and transactions (for data). TLM allows abstracting away the implementation details of, both, the functional modules and the actual communication architecture and allows designers to concentrate on what to transmit instead of concentrating on how to transmit and how to process it.

All the different levels of abstraction are essentially different models of the design, since they provide some but not all of the information about the design. In this thesis we are only considering behavioral and structural descriptions at RTL, which still remains the most widely used level of abstraction for it is equally well understood by both human designers and logic synthesis tools. In this thesis, different hardware modeling techniques at RTL are considered which help raising the quality of verification and speed up the debug process.

## 2.2 Hardware modeling with HDLs

Originally, hardware description languages were introduced to document the behavior of integrated circuits, thus replacing massive and complex manuals with concise and, most importantly, standardized descriptions. It soon became obvious, however, that these concise descriptions are still subject to implementation-specific details and, hence, suffer from ambiguity issues. This understanding led to the idea of making hardware descriptions interpretable in a standardized way so that finally the first publicly available language-based hardware description method with fixed interpretable semantics appeared in 1987 as the IEEE Standard 1076 [17]. The first hardware model simulators implementing the standardized interpretable semantics followed shortly thereafter, along with the automatic circuit synthesizers.

Nowadays integrated circuits are described using *text models* written in HDLs such as VHDL, Verilog, SystemC. We have chosen VHDL [17] as a reference language. The text models are a very popular means of modeling because they

allow a great level of flexibility, resemble natural languages and can be efficiently processed by the machine. Object-oriented paradigm allows modeling both behavior and structure by text. Structured programming paradigm allows capturing hierarchy and supporting different levels of abstraction. To model the inherent concurrency of hardware, HDLs use concurrent statements. Concurrent execution is mimicked in simulators by representing every atomic time step as a sequence of sub-atomic intervals (delta-cycles) simulated sequentially.

#### 2.2.1 VHDL

VHDL (VHSIC Hardware Description Language) [17] is one of the most widely used HDLs at RTL. It has been designed as a standard language from the ground up by incorporating expertise from many industry players of the time. It targets hardware description, synthesis and simulation on the gate, RT and (partially) algorithmic levels. The language is very general due to a large variety of description possibilities and independence from technologies, production processes and methodologies. This makes VHDL designs highly configurable and reusable.

The disadvantages of VHDL stem from its power and generality. Design descriptions are vague and idiomatic (agreed conventions are needed between designers and synthesis tools). While providing additional safety, strong typing also makes the language verbose which in turn makes designs prone to errors and hard to manage and analyze. Smart and scalable tools are required to both harness the potential of the language and avoid its pitfalls.

## 2.2.2 HDLs for verification and debug

The most important problem with HDLs is that, historically, they were designed to only describe the behavior of circuits. Nobody could envision at the time that aspects other than behavior will soon become of the utmost importance. Nowadays, because of the on-going technology and design scaling, *verification* of even a midsized contemporary design takes much *more effort* than the design process itself (up to 80% of total effort [2]). What adds to this effect is the constantly increasing requirements towards the *quality* of verification. The quality requirements are stringent because the integrated circuits have become ubiquitous today and even have made it into the many life-critical systems [7].

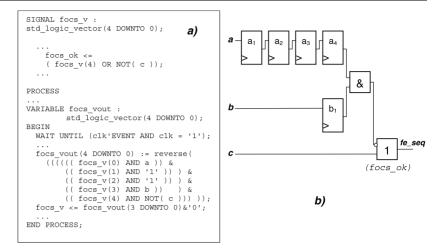

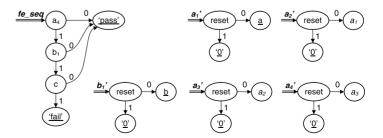

Although convenient for specifying behavior and structure, HDLs do not suit well for verification and debug of concurrent hardware. The awkwardness and even inability of HDLs to represent complex temporal assertions has caused introduction of dedicated hardware verification languages such as *e* [18], OpenVera, SystemVerilog, Property Specification Language (PSL) [19]. These languages in turn are not always supported by simulation tools or this support may be expensive. The attempts to unify design implementation and its properties' representation normally result in creation of large hardware checkers that assume significant

restrictions on the initial assertion functionality. Assertion checkers also impose considerable time and area overheads in case of simulation and emulation, respectively. Moreover, the concurrent nature of HDLs does not allow straightforward and comprehensive verification coverage measurement on HDL descriptions and requires either complicated analysis of HDL code or its transformation into other models [20].

Debugging HDL descriptions is also a tedious and difficult process, and is hard to automate. Because of the concurrent nature of HDLs, multiple execution contexts have to be handled by the designer at the same time, which is not easy for a human. Moreover, in practice synchronous halting of the concurrently operating modules during emulation is also not a trivial task, while the obtained system state dumps may occupy tens of gigabytes of hard to analyze data. Industrially scalable debuggers are only partially automated [21] and offer costly solutions for large businesses, but not for smaller ones. This situation with debugging contrasts with verification approaches where the understanding of the efficiency of verification-enablers has led to the emergence of the Open Source VHDL Verification Methodology (OS-VVM) [22]. OS-VVM helps a lot in creating high-quality testbenches by providing VHDL verification libraries (stimuli randomization and functional coverage evaluation packages) which also hide VHDL complexities. However, as of today these two packages are not enough for creating tests which would explicitly and unambiguously reveal the source of an error if one occurs.

In Chapter 4 of this thesis we will present a scalable method (and its implementation) for automatically localizing bugs in industrial-sized designs.

## 2.3 State-of-the-art models in hardware design and EDA

Electronic design automation (EDA) industry emerged to meet the demand for the tools that could harness the potential of HDLs and cope with complexity of ever-growing integrated circuits (ICs). Among the tasks addressed by the EDA industry are the efficient legacy HDL code exploration and code navigation, coping with verbosity of certain languages (e.g. VHDL) for the sake of design speedup and for fewer design errors, automation of verification, debug and automatic synthesis of HDL descriptions, and also simulation of large-scale ICs.

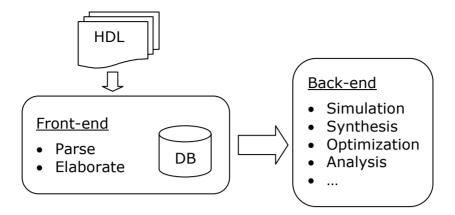

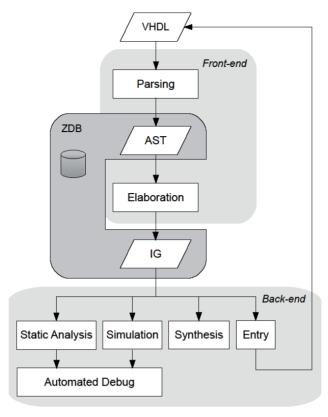

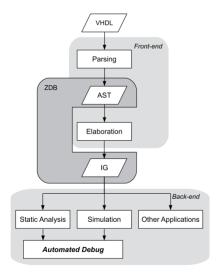

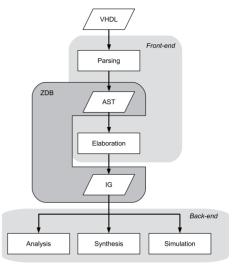

Nowadays the range of the offered EDA solutions is vast. Yet what remains common to all of them is having HDL descriptions as the primary input to these tools — something dictated by many practical concerns and previous experience. At the same time, having a common input format does not mean all these tools use the same underlying models and data structures. Vice versa, each of them relies on its own internal model that represents hardware designs in the most straightforward and convenient way for the given task. To illustrate this, let us consider the typical design flow in EDA tools presented in Figure 2.2.

Figure 2.2 Typical RTL design flow in EDA tools

A typical RTL design flow involves a set of front-end and back-end tools. The *front-end* consists mainly of design parsing and design elaboration and storing the result in a database. Front-end steps are typically language dependent. The *back-end* applications read the elaborated design from the database and process it according to their needs. They might be targeted towards design analysis, design synthesis and optimization or simulation. Generally, to do the job in the most efficient fashion, each such EDA task requires a dedicated intermediate design representation adjusted for the given task and typically generated out of the elaborated design model taken from the database.

The rest of this section presents a brief overview of the different *intermediate* design representation models used by the state-of-the-art EDA tools, both, in industry and academia.

## 2.3.1 Exploitation of models in industry

The enormous size of today's RTL system on chip (SoC) designs together with the predicted technology scaling brings to the front the scalability property of design representation models. Since satisfying the scalability property is not a trivial task, such models are usually kept in-house and are as proprietary as the tools built upon them. This makes it difficult if not impossible to reason about the industrial models beyond what can be deduced from using them as black boxes. We list in this sub-section several common properties of industrial hardware models grouped by the corresponding design tasks the models are applied in.

HDL *code entry* assistance (HDL front-end) could be regarded as the easiest hardware design task. It only requires a parser and a parse tree as an underlying model. Tools like Veditor [23], Sigasi [24], Simplifide [25] propose good Eclipsebased solutions for this and provide code entry, syntax highlighting, code outline

and content assist for VHDL and Verilog. In addition, Simplifide offers hardware specific refactoring features and a coarse-grained design hierarchy view.

When it comes to design navigation and legacy code exploration, tools can no longer rely on a pure parse tree. It alone will allow neither precise navigation (e.g. to find the correct declaration of an overloaded function), nor a decent design comprehension (no elaborated chip hierarchy and other visual representations), nor global signal tracing etc. For such tasks, an elaborated model is required. In certain cases, though, one can still avoid building a proper elaborated model. For instance, it is possible to perform signal tracing, data flow and schematics view to some extent dynamically (e.g. [11]) relying on the testbench quality. However, proper design analysis for these and a set of other analysis tasks (e.g. hierarchy exploration, precise global signal tracing, type checks, sink-less or source-less signals analysis) can be performed only statically [26] and requires generation of a lossless elaborated design model. To grasp the design hierarchy at once and to speed-up the code entry, HDL Designer [27] from Mentor Graphics offers a sophisticated solution for both initial automatic code generation and further visualization and analysis thereof. However, the code gets generated out of nonstandardized tables and graphics, which brings with it all the problems and overheads of invasive approaches, e.g. forces the whole team to use the same tool and only allows a minimal fine-tuning of the generated code afterwards.

The majority of EDA tasks require an elaborated model of the design. For instance Design Compiler [28] by Synopsys, or Verdi Automated Debug System [21] do create such models as an interim step for their further backend processing that are *synthesis* and *debug*, respectively. Verific Parser Platform [29] by itself is a naked *elaboration* engine for both VHDL and Verilog. Verific elaborates designs into a common language-independent HDL database, which is further used as a basis by several commercial hardware design tools.

Finally, when targeting the task of *simulation*, elaborated HDL models have another trait easily observed in such tools as ModelSim [11] and ghdl [30]. Even though the initial compilation/parse of the design is often fast, one has to start the simulator to launch the elaboration and produce the elaborated model for simulation. In practice, this simulation start not only takes a long time to complete, but it often fails by running out of either memory or time in case of large state-of-the-art designs. It confirms the importance of model scalability.

Even in case of industrial tools, the algorithms used in today's front-ends and back-ends are often based on methods developed years ago (Espresso-MV [31], Booledozer [32]) when scalability issues were less of a concern than they are now.

Last, but not least, most of these closed-source EDA tools are of no use to the open source community and of limited use to academia when it comes to building research tools on top of industrially robust models. Scalable hardware models used inside industrial EDA tools are typically kept in-house because of their high value. They are inaccessible to academia which still needs to experiment with large

designs. This leads to pretty severe consequences, namely, to the situation where, on one hand, scientific methods and approaches are required to scale well, and, on the other hand, development of a robust and scalable elaboration engine in the first place (to stay on a par with the industrial scale) is too hard of an intermediate task. No need to say it heavily impairs productivity of researchers and often hinders them from switching to new areas of research where they have no infrastructure yet, no adequate tools to support their work. Even in their area of expertise more often than not their tools can only support small designs which have nothing in common with those in the industry.

One of the contributions of this thesis (entire Chapter 4) lies exactly in filling up this gap. Namely, among other things, the thesis provides a description of a scalable hardware model and the open-source tool zamiaCAD which already implements this model in order to provide a scalable and robust basis for other scientists so that they can build their tools on top of it. The two hence represent what is called a front-end in Figure 2.2.

### 2.3.2 Formal models in research

In this sub-section we provide short descriptions of models widely used across academia to model hardware with the purpose of verification.

Decision Diagrams (DD) have been used in verification for about two decades. Reduced Ordered Binary Decision Diagrams (RO-BDD) [33] as canonical forms of Boolean functions have their application in equivalence checking and in symbolic model checking. Recently, a higher abstraction level DD representation, called Assignment Decision Diagrams (ADD) [34], have been successfully applied to, both, RTL verification and test [35], [36].

The main issue with the BDDs and ADDs is the fact that they only allow either logic or RTL modeling, respectively. In this thesis we consider a different decision diagram representation, High-Level Decision Diagrams (HLDD) that unlike ADDs can be viewed as a generalization of BDDs. HLDDs can be used for representing different abstraction levels from RTL to Transaction Level Modeling (TLM), and when combined with Structurally Synthesized BDDs (SSBDDs) [37], [38] can also support the gate level. Also, although highly useful for synthesis optimization because of their partial uniqueness property [39], ADDs do not suit for the tasks of dynamic verification and debug considered in this thesis. This is because, without labels on the edges, ADDs cannot represent activated paths through the diagram, and they also merge all individual conditions inside conditional statements [40] so that only the final output is known (i.e. atomic representation of conditions) and no debug inside conditional statements becomes possible.

When compared to the RO-BDD models which have worst-case exponential space requirements, HLDD size scales well with respect to the size of the RTL code. The main difference is that traditionally a decision diagram is generated for a

primary output of the system while nodes represent primary inputs. In HLDDs we generate a separate diagram for each variable (signal) v of the VHDL description and nodes represent variables (signals) assigned to v. Note, that the complexity of HLDDs is just O(n) with respect to the number of processes n in the code. And if v is the average number of variables/signals inside a process and c is the average number of conditional branches in a process, then in the worst case the number of nodes in the HLDD model will be equal to  $n \cdot v \cdot c$ . Thus, very large realistic hardware systems can be represented in practice.

At RTL, hardware can also be modeled using algorithmic state machines (ASMs) [41]. ASMs are typically used during the design phase, because they allow specifying exact behavior and timing information for control part and operational part (datapath) in the form of charts, which can be later converted to HDL code. However, attempts exist to also use ASMs for synthesizing fast assertions checkers from PSL properties [42].

Extended finite state machines (EFSMs) [43] are often used for representing control dominated systems. EFSMs allow a more compact representation of design states than traditional FSMs without requiring the explicit enumeration of all the design states. Also, in EFSMs transitions may be associated with internal registers (i.e. not only with primary inputs/outputs, as is the case with conventional FSMs), while the registers themselves are not required to be explicitly represented using states. EFSMs are hence more resistant to the state explosion problem than FSMs. However, traversing an inconsistent EFSM may be more difficult than traversing an FSM [44] and requires solving the inconsistencies.

Petri-net [45] based models are widely used for modeling hardware at levels above RTL. In [46], Petri-net based Representation for Embedded Systems (PRES+) is used to formally verify components and their interaction at TLM. Petrinets allow modeling concurrent interprocess communication while abstracting away the exact implementation of, both, the interconnection and the processes.

Hardware models can also be combined together to achieve a valuable synergic effect. In [47]<sup>co-auth</sup>, EFSM and HLDD models were exploited inside a functional test pattern generator. EFSM model was used for targeting control FSM transitions, while variable-oriented HLDD model targeted bit-coverage faults in the data variables. HLDD-based engine also provided information about untestable areas in the design to the EFSM-based engine, which improved the efficiency and speed of the overall test generation.

## 2.4 HLDD model preliminaries

A High-Level Decision Diagram (HLDD) [38] is a graph representation of a discrete function. It was proposed by Raimund Ubar in 1983 [48] for test generation and simulation due to its ability to efficiently and uniformly describe the

structure, function and faults of digital circuits. HLDDs can be considered as a generalization of Binary Decision Diagrams (BDDs), where as opposed to BDD the variables at the nodes can be of any scalar type, i.e. not just Booleans. HLDD model has proven to be an efficient model for simulation and fault modeling since it provides for a fast evaluation by graph traversal and for easy identification of cause-effect relationships [49], [50].

#### 2.4.1 HLDD model definition

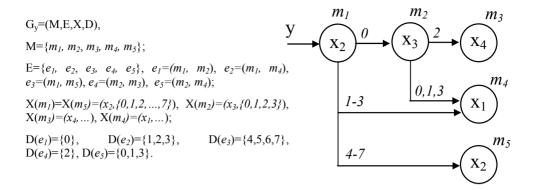

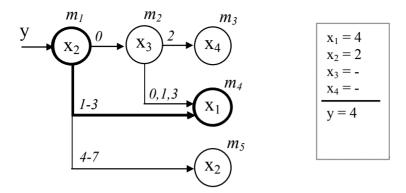

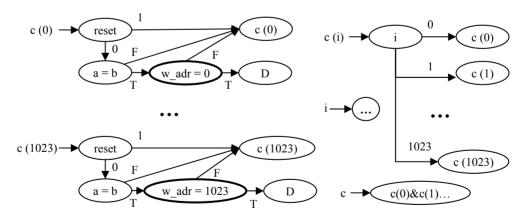

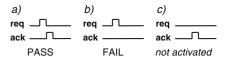

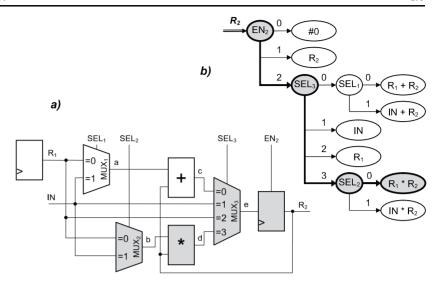

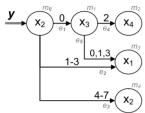

According to [51], a *High-Level Decision Diagram* (HLDD) is a graph representation of a discrete function. A discrete function y = f(x), where  $y = (y_1, ..., y_n)$  and  $x = (x_1, ..., x_m)$  are vectors is defined on  $X = X_1 \times ... \times X_m$  with values  $y \in Y = Y_1 \times ... \times Y_n$ , and both the domain X and the range Y are finite sets of values. The values of variables may be Boolean, Boolean vectors, integers. Figure 2.3 presents an example of a graphical interpretation of an HLDD.

**Definition 1:** A high-level decision diagram is a directed non-cyclic labeled graph that can be defined as a quadruple G=(M,E,X,D), where M is a finite set of vertices (referred to as *nodes*), E is a finite set of *edges*, X is a function which defines the *variables labeling the nodes*, and D is a function on E.

The function  $X(m_i)$  returns the variable  $x_i$ , which is labeling node  $m_i$ . Each node of an HLDD is labeled by a variable. In special cases, nodes can be labeled by constants or algebraic expressions. An edge  $e \in E$  of an HLDD is an ordered pair  $e = (m_1, m_2) \in M^2$ , where  $M^2$  is the set of all the possible ordered pairs in set M. Graphical interpretation of e is an edge leading from node  $m_1$  to node  $m_2$ .

It is said that  $m_1$  is a predecessor node of  $m_2$ , and  $m_2$  is a successor node of the node  $m_1$ , respectively. D is a function on E representing the activating conditions of the edges for the simulating procedures. The value of D(e) is a subset of the domain  $X_i$  of the variable  $x_i$ , where  $e=(m_i,m_j)$  and  $X(m_i)=x_i$ . It is required that  $Pm_i = \{D(e) \mid e = (m_i,m_i) \in E\}$  is a partition of the set  $X_i$ .

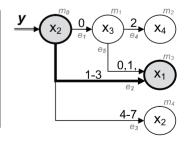

Figure 2.3 presents an HLDD for a discrete function  $y=f(x_1,x_2,x_3,x_4)$ . HLDD has only one starting node ( $root\ node$ )  $m_0$ , for which there are no preceding nodes. The nodes that have no successor nodes are referred to as  $terminal\ nodes\ M^{term}\in M$  (nodes  $m_3,\ m_4$  and  $m_5$  in Figure 2.3). In HLDD models representing digital systems the non-terminal nodes correspond to conditions or to control signals, and the terminal nodes represent operations (functional units), register transfers and constant assignments. Design representation by high-level decision diagrams in general case is a system of HLDDs rather than a single HLDD. During the simulation in HLDD systems the values of some variables labeling the nodes of an HLDD are calculated by other HLDDs of the system.

Figure 2.3 An HLDD for a function  $y=f(x_1,x_2,x_3,x_4)$

#### 2.4.2 Simulation on HLDDs at RTL

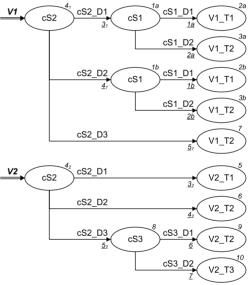

According to [50], simulation on decision diagrams takes place as follows. Consider a situation where all the node variables are fixed to some value. For each non-terminal node  $m_i \notin M^{erm}$  according to the value  $v_i$  of the variable  $x_i = X(m_i)$  a certain output edge  $e = (m_i, m_j)$ ,  $v_i \in D(e)$  will be chosen which enters into its corresponding successor node  $m_j$ . Let us call such connections between nodes activated edges under the given values. Succeeding each other, activated edges form in turn activated paths. For each combination of values of all the node variables there exists always a corresponding activated path from the root node to some terminal node. This path is referred to as the main activated path. The simulated value of the variable represented by the HLDD will be the value of the variable labeling the terminal node of the main activated path.

In Figure 2.4 simulation on the HLDD presented in Figure 2.3 is shown. Assuming that variable  $x_2$  is equal to 2, a path (marked by bold arrows) is activated from node  $m_1$  (the root node) to a terminal node  $m_4$  labeled by  $x_1$ . The value of variable  $x_i$  is 4, thus,  $y=x_i=4$ . Note that this type of simulation is event-driven since we have to simulate those nodes only (marked by bold circles in Figure 2.4) that are traversed by the activated path. This gives HLDDs advantages over netlists of primitive functions in terms of efficiency in simulation and diagnostic modeling because of the direct representation of cause-effect relationships. In fact, HLDD based simulation algorithms have also been shown to outperform commercial event-driven HDL simulators in 12 - 30 times and cycle-based simulators in 4 to 6 times [49]. This is achieved due to combining event-driven (path activation in the HLDD graphs) and cycle-based (HLDDs are synthesized into cycle-accurate models) paradigms. In other words, only a part of HLDDs should be traced during simulation (the activated path) and the time specific information inherent in HDL descriptions can be (and is) neglected during simulation [50]. Timing information is only considered once during HLDD generation.

Figure 2.4 Design simulation on HLDDs

As it was previously mentioned, when representing systems and functions by decision diagram models, in general case, a network of HLDDs rather than a single HLDD is required. During the simulation in HLDD systems, the values of some variables labeling the nodes of an HLDD are calculated by other HLDDs of the system. The detailed algorithm for HLDD based system simulation was proposed in [49] and is presented in Figure 2.5. The algorithm supports both behavioral and structural design representations at RTL.

In the structural RTL style, the algorithm takes the previous time step value of variable  $x_j$  labeling a node  $m_i$  if  $x_j$  represents a clocked variable in the corresponding HDL. Otherwise, the present value of  $x_j$  will be used. In the case of behavioral HDL coding style, HLDDs are generated and ranked in a specific order to ensure causality. For variables  $x_j$  labeling HLDD nodes the previous time step value is used if the HLDD diagram calculating  $x_j$  is ranked after current decision diagram. Otherwise, the present time step value will be used.

```

For each diagram G in the model

m_{Current} = m_0

Let x_{Current} be the variable labeling m_{Current}

While m_{Current} is not a terminal node

If x_{Current} is clocked or its DD is ranked after G then

Value = previous time-step value of x_{Current}

Else

Value = present time-step value of x_{Current}

End if

For each edge e in m_{Current}

If Value \in D(e_{active}), e_{active} = (m_{Current}, m_{Next}) then

m_{Current} = m_{Next}

End if

End for

End while

Assign x_G = x_{Current}

End for

```

Figure 2.5 Algorithm 1. Simulation on structural and behavioral HLDDs

# 2.5 Summary

In this chapter we have provided an overview of the typical hardware design flow and the hardware description models employed in the individual steps of this flow. We have shown how hardware is formally modeled in academic research and what problems appear when modeling hardware of industrial scale.

In particular, the background information about the high-level decision diagrams academic model was presented for better understanding of Chapter 3 where the HLDD model and its applications are extended beyond simulation and test generation covered so far by the model.

The rest of this thesis is devoted to solving the design problems mentioned in this chapter. Namely, in Chapter 3 and Chapter 4 we tackle the problems of scalability, accurate verification and fast debug with the help of academic high-level decision diagrams model and industrial scale instantiation graph model.

# Chapter 3

# HARDWARE MODELING WITH HIGH-LEVEL DECISION DIAGRAMS

This chapter discusses application of HLDD model to the tasks of hardware verification and debug.

Design representation with HLDDs was shown efficient for functional simulation and RTL test generation. One of the contributions of the author of this thesis lies in extending the use of HLDDs by:

- developing methods for automated synthesis of behavioral and structural HLDDs from VHDL code, which allowed obtaining HLDD representations for larger designs than could be manually constructed before;

- extending the application of HLDD model to other design tasks such as verification and debug by both participating in the development of the appropriate theories for HLDD exploitation in new areas and by adapting the model itself according to the given theory;

- 3) participating in the creation of a unified verification framework APRICOT and its implementation as ApricotCAD tool where all HLDD engines are integrated into a single solution.

All the three points are described in detail in sections 3.1, 3.2 and 3.3, respectively.

# 3.1 HLDD generation

The process of HLDD generation was described in detail in [52] auth.

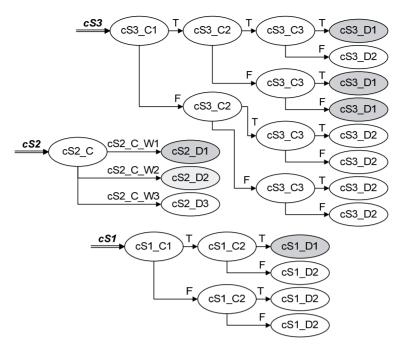

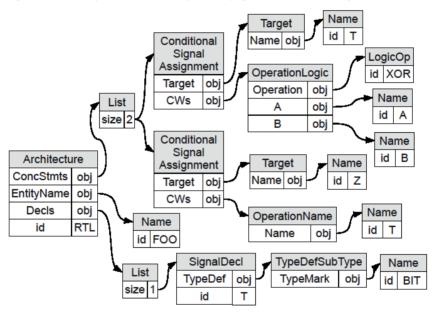

To represent behavioral RTL descriptions, a separate HLDD diagram is generated for each VHDL signal, variable or output port. For those variables that change their value several times per clock a separate diagram is generated for each such value change. HLDD graph generation from VHDL code happens as follows:

- 1. Conditions from *if/case* statements or conditional assignments are represented by a non-terminal node with its edges marked by decisions of the condition.

- 2. Right-hand sides of assignments are represented by terminal nodes.

- 3. Those branches of conditional statements, where no assignment is made to the signal of interest, are filled with a default sub-graph. The default sub-graph is a graph constructed from preceding parallel assignment statements if such exist. Otherwise it is a value retaining terminal node. A warning is issued to inform about implicit latches when a value retaining terminal node is filled for a non-clocked variable.

- 4. The resulting HLDD graphs are topologically sorted to ensure causality during behavioral simulation (*Algorithm 1* in Figure 2.5).

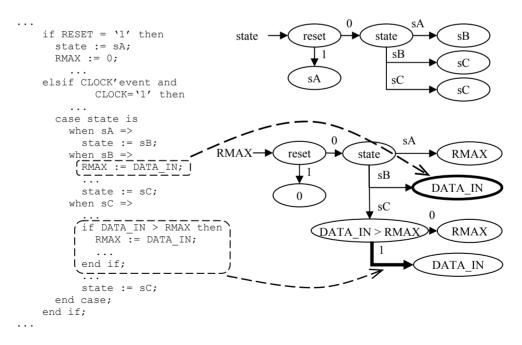

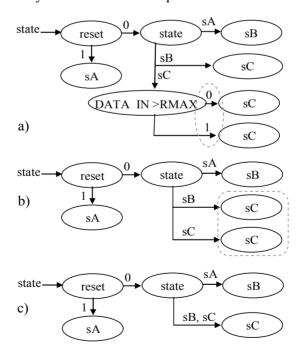

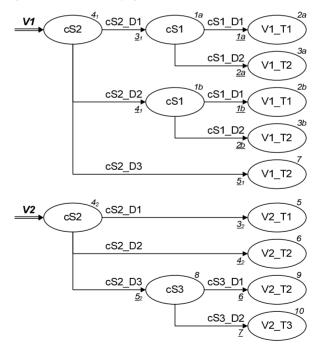

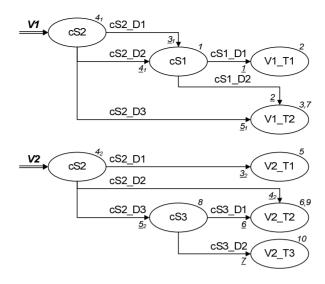

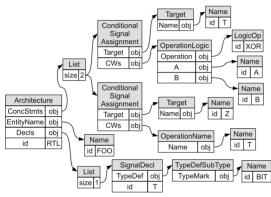

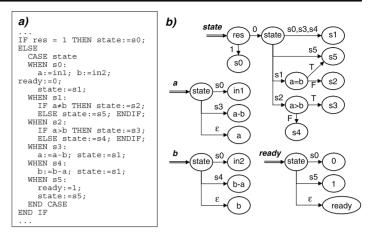

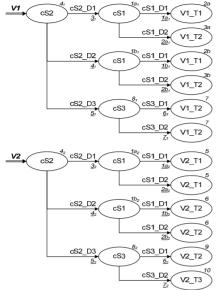

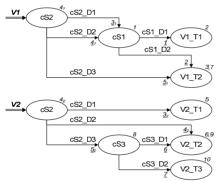

Figure 3.1 presents an example of an HLDD generated for two variables, *state* and *RMAX* in the ITC99 benchmark b04.

Figure 3.1 b04 example: behavioral HLDDs for variables state and RMAX

Several compactness levels of HLDD representations provide different tradeoffs between the HLDD-based analysis stringency and simulation speed with memory requirements. The three options of *model compactness* (full tree, reduced and minimized) will be discussed in sub-section 3.2.2.1 in frames of code coverage measurement. Different options for representing *conditional statements* are discussed in sub-section 3.2.2.2 in frames of condition coverage measurement. In HLDDs, conditional statements can be represented as built-in functions, as functions plus extra-graphs, as expansion graphs and as flattened graphs.

From modeling perspective, when generating HLDDs from VHDL descriptions, the appropriate selection among compactness levels and conditional statements representations depends on the target application.

In the following sub-sections we will add more details on HLDD generation not mentioned in [52]<sup>auth</sup> because they had not been addressed at the time. The four new aspects are the support of design hierarchy, generation of temporal verification assertions and efficient handling of memories and assignments to signal slices/sub-elements. The synthesis of temporal assertions into special Temporally Extended HLDD graphs will be discussed in detail in section 3.2.3.

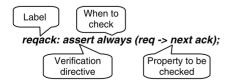

### 3.1.1 Handling of hierarchical designs