# Fault Simulation and Code Coverage Analysis of RTL Designs Using High-Level Decision Diagrams

ULJANA REINSALU

#### TALLINN UNIVERSITY OF TECHNOLOGY

#### Faculty of Information Technology Department of Computer Engineering

Dissertation was accepted for the defense of the degree of Doctor of Philosophy in Computer and Systems Engineering on May 11, 2013

Supervisors: Prof. Peeter Ellervee

Prof. Jaan Raik

Dr. Aleksander Sudnitsõn

Opponents: Dr. Graziano Pravadelli, University of Verona, Italy

Dr. Juha Plosila, University of Turku, Finland

Defence of the thesis: June 12, 2013

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted for any academic degree.

/Uljana Reinsalu/

European Union European Social Fund

Investing in your future

Copyright: Uljana Reinsalu, 2013

ISSN 1406-4731

ISBN 978-9949-23-476-9 (publication)

ISBN 978-9949-23-477-6 (PDF)

### INFORMAATIKA JA SÜSTEEMITEHNIKA C86

# Rikete simuleerimine ja koodikatte analüüs register-siirde tasemel kasutades kõrgtaseme otsustusdiagramme

ULJANA REINSALU

## **Abstract**

This thesis addresses hardware testing issues as well as simulation-based hardware verification issues applied at register-transfer and behavioral levels of design abstraction. Particularly the main topics are Register-Transfer Level (RTL) fault simulation and structural coverage measurement exploiting advantages of High-Level Decision Diagrams (HLDD) design representation model.

First, a novel method for fault simulation at RTL based on the HLDD model is presented. The method is based on deductive fault simulation algorithm brought to higher level of abstraction and applied to the design represented by HLDDs. Efficient data structure was implemented into the algorithm in order to make fast bitwise operations with fault lists and this way to accelerate the fault simulation. Fault simulation is widely used in test stimuli generation for digital circuits. Other tasks as fault diagnosis, test stimuli compaction, built-in-self test optimization incorporate fault simulation as part of the process. Thus efficient fault simulation algorithm is very important for solving these tasks.

Second, a novel method for structural code coverage analysis based on the HLDD model is presented. Traditional code coverage metrics as statement coverage, branch coverage and toggle coverage are mapped onto HLDD constructs. With the help of fast HLDD-based simulation the measuring of these coverage is efficient. The method also implies manipulations with HLDDs for finding better HLDD model representation targeting different aspects in code coverage analysis. Moreover, observability coverage metric is implemented into HLDD simulation engine. This metric measures not only activation of the bugs but also evaluates the propagation of these bugs to the observable points. Observability coverage metric makes possible to better analyze the test stimuli and circuit's design.

All proposed methods rely on a HLDD-based simulation engine. Previous research works in TUT (Tallinn University of Technology) show that HLDDs are efficient models for digital circuits' simulation as well as convenient for diagnosis and debugging. The performed experiments confirm feasibility and efficiency of the proposed methods.

# Kokkuvõte

Käesolev töö käsitleb nii digitaalriistvara testimise kui ka simuleerimisel põhineva verifitseerimise küsimusi register-siirde ja käitumuslikul tasemel. Töös pakutud lähenemised rikete simuleerimiseks register-siirde tasemel ning struktuurse katte mõõtmiseks kasutavad kõrgtaseme otsustusdiagrammide (KTOD) eeliseid skeemide esitamisel.

Kõigepealt on esitatud uudne meetod rikete simuleerimiseks register-siirde tasemel, mis põhineb KTOD mudelil. Meetod tugineb deduktiivsele rikete simuleerimisalgoritmile, mis on viidud kõrgemale abstraktsioonitasemele ning rakendatud KTOD-na esitatud digitaalriistvarale. Algoritmi on lisatud efektiivne andmestruktuur selleks, et kiirendada bitioperatsioone rikete nimekirjadega ning järelikult kiirendada rikete simulatsiooni tervikuna. Rikete simuleerimist kasutatakse laialt digitaalriistvara testi stiimulite genereerimisel. Sellised ülesanded nagu rikete diagnostika ja testi stiimulite kokkupakkimine isetestivate arhitektuuride projekteerimine vajavad oma töös rikete simuleerimist. Seega on efektiivne rikete simuleerimise algoritm väga tähtis nende ülesannete lahendamisel.

Teiseks on esitatud uudne meetod struktuurseks koodikatte analüüsiks, mis samuti põhineb KTOD mudelil. Traditsioonilised koodikatte mõõdud nagu lausete, harude ja andmevoo kated seoti KTOD struktuuriga. KTOD-põhine kiire simuleerimine võimaldab mõõta neid katteid efektiivselt. Samuti sisaldab pakutud meetod KTOD mudeli teisendusi, mis on suunatud koodikatte analüüsi erinevatele aspektidele. Lisaks on KTOD simulaatori jaoks realiseeritud jälgitavuse katte mõõt. See mõõt mõõdab mitte ainult vigade aktiveerimist vaid ka hindab nende levimist vaadeldavatesse punktidesse. Jälgitavuse katte mõõt võimaldab paremini analüüsida testi stiimuleid ning digitaalriistvara disaini.

Pakutud meetodid toetuvad KTOD-l põhinevale simulaatorile. Eelnev uurimistöö TTÜ-s on näidanud, et KTOD on efektiivne mudel simuleerimise läbiviimiseks ning sobilik digitaalsüsteemide diagnostikat ja silumist silmas pidades. Töös teostatud eksperimendid tõestavad pakutud lähenemiste rakendatavust ja efektiivsust.

# Acknowledgements

I would like to express my sincere gratitude to everybody who have supported and advised me during my PhD studies.

First of all, I would like to thank my supervisors. I appreciate the support and advices of Prof. Peeter Ellervee. He is always open to discussions and helps in solving different problems. I am thankful to Prof. Jaan Raik for his guiding and consulting during the work on this thesis and also his joyful encouraging to continue working and to finish this thesis. His attitude to life gives me the energy in doing things. I would like to thank Aleksander Sudnitsõn for his remarks concerning this thesis. I would like to thank Prof. Raimund-Johannes Ubar for his help and wise advices.

Special thanks to the head of the Department of Computer Engineering Margus Kruus for creating outstanding environment for productive work and study.

I also would like to thank all my colleagues from Department of Computer Engineering for their interesting discussions and ideas. In particular I would express my appreciation to Sergei Devadze, Maksim Jenihhin, Artur Jutman, Marina Brik.

Moreover, I would like to acknowledge the organizations that have supported my PhD studies: Tallinn University of Technology, National Graduate School in Information and Communication Technologies (IKTDK), Estonian IT Foundation (EITSA), Centre of Integrated Electronic Systems and Biomedical Engineering (CEBE), FP7 STREP projects DIAMOND, FP6 STREP project VERTIGO.

Finally, I would like to thank my great family for the patience and support. In particular I would like to mention all my parents for their valuable support in my family nest, also my beloved husband Juri for his philosophical discussions and support and express my gratitude to my sweet children Artur and Timur for giving me chance for development.

Uljana Reinsalu, Tallinn, May 2013

# **Table of Contents**

| Abstract                                       | <i>7</i> |

|------------------------------------------------|----------|

| Kokkuvõte                                      | 9        |

| Acknowledgements                               | 11       |

| List of Publications                           | 15       |

| Author's Contribution to the Publications      | 17       |

| List of Abbreviations                          |          |

| Chapter 1 INTRODUCTION                         | 21       |

| 1.1 Motivation                                 | 21       |

| 1.2 Problem formulation                        | 25       |

| 1.3 Contributions                              | 27       |

| 1.4 Thesis organization.                       | 28       |

| Chapter 2 BACKGROUND                           | 31       |

| 2.1 Design representation by decision diagrams | 31       |

| 2.1.1 Binary decision diagrams                 | 32       |

| 2.1.2 High-level decision diagrams             | 34       |

| 2.1.2.1 HLDD model definition                  | 34       |

| 2.1.2.2 Modeling RTL designs by HLDDs          | 38       |

| 2.1.2.3 Basic simulation on HLDDs              | 38       |

| 2.2 Fault Simulation                           | 40       |

| 2.2.1 The role of Testing                      | 41       |

| 2.2.2 Top-Down Design and Test Methodology     | 42       |

| 2.2.3 Fault modeling                           | 43       |

| 2.2.4 Fault simulation.                        |          |

| 2.2.4.1 Serial Fault Simulation                | 47       |

| 2.2.4.2 Parallel Fault Simulation              | 48       |

| 2.2.4.3 Deductive Fault Simulation                  | 50 |

|-----------------------------------------------------|----|

| 2.2.4.4 RTL Fault Simulation                        | 52 |

| 2.2.5 Applications                                  | 53 |

| 2.3 Design Verification                             | 55 |

| 2.3.1 Simulation-based verification                 | 57 |

| 2.3.2 Coverage metrics                              | 59 |

| 2.4 Chapter summary                                 | 60 |

| Chapter 3 HLDD-BASED FAULT SIMULATION               | 61 |

| 3.1 Overview                                        |    |

| 3.2 Deductive Fault Simulation on HLDDs             | 63 |

| 3.2.1 Algorithm Structure                           | 64 |

| 3.2.2 Example of deductive fault simulation on HLDD | 69 |

| 3.2.3 Internal Data Representation                  | 71 |

| 3.2.4 Analysis of the algorithm                     | 72 |

| 3.3 Experimental results                            | 73 |

| 3.4 Chapter summary                                 | 74 |

| Chapter 4 HLDD-BASED CODE COVERAGE                  | 75 |

| 4.1 Overview                                        | 75 |

| 4.2 Coverage metrics on HLDD                        | 76 |

| 4.2.1 Simulation algorithm                          | 77 |

| 4.2.2 Mapping standard coverage metrics on HLDDs    | 78 |

| 4.3 HLDD manipulations for code coverage            |    |

| 4.4 Experimental results                            | 81 |

| 4.5 Chapter summary                                 | 84 |

| Chapter 5 HLDD-BASED OBSERVABILITY COVERAGE         |    |

| 5.1 Overview                                        |    |

| 5.2 HLDD-based observability coverage               | 88 |

| 5.2.1 Integration into a tool                       |    |

| 5.2.2 Simulation results                            |    |

| 5.3 Observability coverage metric discussion        | 92 |

| 5.4 Chapter summary                                 | 94 |

| Chapter 6 CONCLUSIONS AND FUTURE WORK               | 95 |

| 6.1 Conclusions                                     |    |

| 6.2 Future work                                     | 96 |

| References                                          |    |

| Appendix                                            |    |

| Curriculum Vitae in English                         |    |

| Curriculum Vitae eesti keeles                       |    |

## **List of Publications**

#### Papers included in the thesis

- Reinsalu, U.; Raik, J.; Ubar, R. (2010). Register-Transfer Level Deductive Fault Simulation Using Decision Diagrams. *In: Proceedings* of the 12th Biennial Baltic Electronic Conference BEC2010, Tallinn, Estonia, 2010, pp. 193 – 196

- 2. Reinsalu, Uljana; Raik, Jaan; Ubar, Raimund; Ellervee, Peeter (2011). Fast RTL Fault Simulation Using Decision Diagrams and Bitwise Set Operations. *Proceedings of 26th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems*. Vancouver, Canada, 2011, pp. 164-170

- 3. Raik, J.; Reinsalu, U.; Ubar, R.; Jenihhin, M.; Ellervee, P. (2008). Code Coverage Analysis using High-Level Decision Diagrams. *In: Proceedings of the 11th IEEE Workshop on Design and Diagnostics of Electronic Systems (DDECS), 16-18 April 2008*, Bratislava, Slovakia

- Minakova, K.; Reinsalu, U.; Chepurov, A.; Raik, J.; Jenihhin, M.; Ubar, R.; Ellervee, P. (2008). High-Level Decision Diagram Manipulations for Code Coverage Analysis. *The 11th Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, Oct. 2008, pp. 207 210

#### System level modeling

- 5. Reinsalu, U.; Arhipov, A.; Ellervee, P. (2008). Architectural Exploration Tasks for On-Chip Embedded Systems. *The 11th Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, Oct. 2008., pp. 171 174

- 6. Ellervee, P.; Reinsalu, U.; Arhipov, A. (2007). Translating Behavioral VHDL for Emulation. *25th NORCHIP Conference*, Aalborg, Denmark, Nov. 2007

7. Ellervee, P.; Arhipov, A.; Reinsalu, U. (2007). Using Emulation for System Model Analysis. *DATE'07 Friday Workshop on "Diagnostic Services in Network-on-Chips"*, Nice, France, April 2007, pp. 280 – 282

#### Educational topics

- 8. Raik, J.; Jenihhin, M.; Chepurov, A.; Reinsalu, U.; Ubar, R. (2008). APRICOT: a Framework for Teaching Digital Systems Verification. *19th EAEEIE Annual Conference*, Tallinn, Estonia, 2008, pp. 1 6

- 9. Ellervee, P.; Reinsalu, U.; Arhipov, A.; Ivask, E.; Tammemäe, K.; Evartson, T.; Sudnitson, A. (2008). HDL-s and FPGA-s in Digital Design Education. *The 19th EAEEIE Annual Conference*, Tallinn, Estonia, June 2008, pp. 37 41

- Reinsalu, U.; Arhipov, A.; Evartson, T.; Ellervee, P. (2007). HDL-s for Students with Different Background. *International Conference on Microelectronic Systems Education (MSE'07)*, San Diego, CA, USA, June 2007, pp. 69 – 70

- 11. Ellervee, P.; Reinsalu, U.; Arhipov, A. (2006). Teaching HDL for IT-Students. *The 6th European Workshop on Microelectronics Education* (EWME'2006), Stockholm, Sweden, June 2006, pp. 112 115

## **Author's Contribution to the Publications**

**Research paper I [64]** Reinsalu, U.; Raik, J.; Ubar, R. (2010). Register Transfer Level Deductive Fault Simulation Using Decision Diagrams. *In: Proceedings of the 12th Biennial Baltic Electronic Conference BEC2010*, Tallinn, Estonia, 2010, pp. 193 – 196

The author modified the deductive fault simulation algorithm for RTL abstraction. The author implemented this algorithm using HLDDs. The author carried out the experiments with selected set of benchmarks and analyzed the results from the experiments. The author prepared the publication of the paper and presented this paper at the conference.

**Research paper II [63]** Reinsalu, Uljana; Raik, Jaan; Ubar, Raimund; Ellervee, Peeter (2011). "Fast RTL Fault Simulation Using Decision Diagrams and Bitwise Set Operations.", *Proceedings of 26th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems.* Vancouver, Canada, 2011, pp. 164-170

The author proposed new data structure for storing the fault list required during RTL deductive fault simulation algorithm work. This data structure is efficient for making bitwise set operations. The author integrated this new data structure into the previously implemented RTL deductive fault simulation algorithm. The author carried out the experiments with selected set of benchmarks and analyzed the results from the experiments. The author prepared the publication of the paper and presented this paper at the conference.

Research paper III [59] Raik, J.; Reinsalu, U.; Ubar, R.; Jenihhin, M.; Ellervee, P. (2008). Code Coverage Analysis using High-Level Decision Diagrams. In: Proceedings of the 11th IEEE Workshop on Design and Diagnostics of Electronic Systems (DDECS), 16-18 April 2008, Bratislava, Slovakia

The author proposed the mapping of structural code coverage metrics onto high-level decision diagrams. The author integrated proposed metrics into existing HLDD simulation engine. The author carried out the experiments with selected

set of benchmarks and analyzed the results from the experiments. The author helped preparing the publication of the paper and presented this paper at the conference.

**Research paper IV [54]** Minakova, K.; Reinsalu, U.; Chepurov, A.; Raik, J.; Jenihhin, M.; Ubar, R.; Ellervee, P. (2008). High-Level Decision Diagram Manipulations for Code Coverage Analysis. *The 11th Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, Oct. 2008, pp. 207 – 210

The author proposed the set of experiments with different modifications of HLDDs for code coverage analysis. The author supervised the experiments and helped in analysis the results. The author helped in preparation of the paper.

# List of Abbreviations

AGM Alternative Graph Model

APRICOT Assertions, PRopertIes, Coverage and Test

ASIC Application Specific Integrated Circuit

ATPG Automatic Test Pattern Generator

BDD Binary Decision Diagram

BIST Built-In Self-Test

CAD Computer Aided Design

CMOS Complementary metal-oxide-semiconductor

CUT Circuit Under Test

DD Decision Diagram

DUV Design Under Verification

EDA Electronic Design Automation

EDIF Electronic Design Interchange Format

FPGA Field Programmable Gate Array

GCD Greatest Common Devisor

GUI Graphical User Interface

HDL Hardware Description LanguageHLDD High-Level Decision Diagrams

IEEE Institute of Electrical and Electronics Engineers

PC Personal Computer

RTL Register Transfer Level

SSF Single Stuck-Fault

TLM Transaction Level Modeling

TPG Test Pattern Generation

TUT Tallinn University of Technology

VHDL VHSIC (Very-High-Speed Integrated Circuit) Hardware

Description Language

VLSI Very Large Scale Integration

### Latin and English abbreviations:

*aka* - also known as

e.g. - for example

et al. - and other co-authors

etc. - and the resti.a. - among others

*i.e.* - that is vs. - versus

# Chapter 1 INTRODUCTION

This thesis presents hardware testing issues as well as simulation-based hardware verification issues. Particularly, the main topics are Register-Transfer Level (RTL) fault simulation and structural coverage measurement exploiting advantages of the High-Level Decision Diagrams (HLDD) design representation model.

This chapter begins with motivation to this work, followed by the problem formulation. Then, summary of the main contributions and an overview of the thesis structure are described.

#### 1.1 Motivation

Different electronic devices have become a part of everyday's life. Nowadays electronic devices are developed not only for specific fields such as military, avionics, space, medical applications, etc., but also in quantity for general use such as mobile phones, tablet PCs, and many others. Although some devices have quite simple functionality, a huge amount of surrounded electronics has become more complex with wide range of functionality. This is thanks to the tremendous progress in the CMOS (Complementary metal-oxidesemiconductor) technology. According to the famous Moore's law [55][40], the number of transistors on integrated circuits doubles every two years. Thus complexity of integrated circuits grows, devices become smaller, density of transistors grows, which allow using a lot of functionality within one circuit. Despite the fact that such complex devices need more man power resources to implement, time-to-market imposes even shorter time than it demanded before for less complex devices. This fact raises the need for efficient EDA (Electronic

Design Automation) tools. The more automation included into the tools, the easier the process of finding the suitable solutions.

In this thesis, only the digital part of the systems is taken into account. During the last ten years digital electronic devices have become an important part of daily life. People have got dependent on surrounding electronics and its correct functionality. Strong reliability issues are a must for space, automotive applications, however reliability issues have become very significant for consumer electronics as well. Nobody wants a malfunctioning mobile phone during a very important talk or a tablet PC turning off while critical work is done on it. Also, consumers want to have manifold functionalities on their devices and new features can be desirable only if basic functionality does not fail. This obligates producers to spend more effort on reliability issues. In order to reach a certain level of reliability, considerable testing of electronic devices is required.

The cost of a hardware error is very high for the industry. It cannot be easily fixed by applying a patch as it is usually done for software products. A new device must be reproduced with errors fixed by withdrawing the previous version, which is extremely costly for the producer. There are many causes of errors: errors in specification, errors at any level of implementation, physical defect of manufacturing. Moreover, errors in hardware can appear during the lifetime of a device in consequence of a variety of reasons, such as high temperature or radiation for example. Therefore, it is strongly important to verify a design at every stage of implementation by fixing the bugs at any cost before manufacturing. Also, testing the devices for manufacturing defects is obligatory for every device [13].

Design cycles of the circuit are divided into several abstraction levels. Usually top-down design methodology is used. Thus a lot of decisions should be done at higher level of abstraction in order to shorten time-to-market. Therefore, many design tasks, which were used to be implemented at the gate level, are transferred to the register-transfer level (RTL) and higher levels. Sure, at this level one can not have exact data, however sufficient estimation can be done, which allows throwing out unsuitable solutions very early. Also, verification is mandatory after each step of design flow, detecting errors as early as possible and avoiding propagation of errors to lower levels of abstraction, thereby saving time and money.

One of the topics of the current thesis is improving fault simulation techniques, which is one of the most important issues in digital testing. Fault simulation is brought to the behavioral level of abstraction of the circuit design in order to speed up the design cycle by preparing valuable test suits for testing already at this level of abstraction. Fault simulation is heavily used by many test-oriented tasks. These are automatic test generation, fault diagnosis, test quality assessment, test suite compaction and other problems. If fault simulation is efficient, then accomplishment of all these tasks will gain in speed while keeping the quality.

Other topic of the current thesis is code coverage analysis at the register-transfer level as one of the simulation-based verification tasks. With the growth of digital devices' complexity a huge effort is required to verify the functionality of the device including finding the errors and localizing them. The exhaustive stimulus for today's designs is huge. It is mostly impossible to generate and exercise this stimulus due to the fact that it will take millions of years to execute [43]. Therefore, a coverage model is built to identify key stimulus values. These input values and their sequence allows sufficiently exercise design functionality. To measure the verification effort, different coverage metrics are employed to show whether the design is verified enough. Coverage metrics should be on one hand simple so that it would be quick to run the simulation using the metric and get an answer, on the other hand they should be sophisticated in order to thoroughly examine the design. Usage of the well-defined coverage metrics is widespread because they are integrated into simulation engines. The code coverage analysis process is fully automated.

#### Testing and fault simulation

The terms testing and verification differ. Testing does not refer to checking the correctness of design implementation, i.e., functional verification. Testing of electronic devices is a process of checking the manufacturing correctness [92]. Usually testing is done after each and every device is fabricated in silicon to ensure that the device is free of manufacturing defects that can appear during the manufacturing process. The types of physical defects depend on technology.

Usually during the testing phase ready-made stimuli is applied to the manufactured device and output responses are collected. Correct output values are also given with the set of input stimuli and compared to the real device outputs. If any mismatch in outputs has happened then a failure has occurred. The device can be sent to diagnosis for finding the defect. If it is possible then repair of the device is done. In the worst case the device is thrown away.

During preparation of the set of input stimuli, the device has not been manufactured yet, only the model of the device exists. Therefore, a model of defects is required to simulate actual physical defects. This model is called a

fault model. It imitates the behavior of actual physical defects as close as possible. At the same time it is mathematically simple enough for fast computation. To determine the effectiveness of test vectors regarding detectability of faults, fault simulation is employed. During fault simulation test vectors are applied to implemented device one after other and for each test vector, detected faults are determined. One of the outputs of fault simulation is fault coverage, which is the ratio of faults detected by the test stimuli out of all possible faults in the device. The higher the fault coverage, the better the quality of test stimuli is. Obviously, the fault simulation process is computationally expensive and both memory and time consuming. Thus, it is very important to accelerate this process, which is used as a basic task in different test-oriented tasks mentioned above for improving their performance.

One possible approach is to use fault simulation at the RT (Register-Transfer) level that is to build RTL fault model, which is closely related to the gate-level fault model and to compute fault coverage already at this level of abstraction. The obtained set of test vectors can be reused at lower levels of abstraction, which makes the application of test-oriented tasks at lower levels of abstraction easier and faster. The current thesis is focused on fault simulation at the RTL using the RTL bit-coverage fault model, which is well correlating with the stuck-at fault model [29].

#### Verification and code coverage analysis

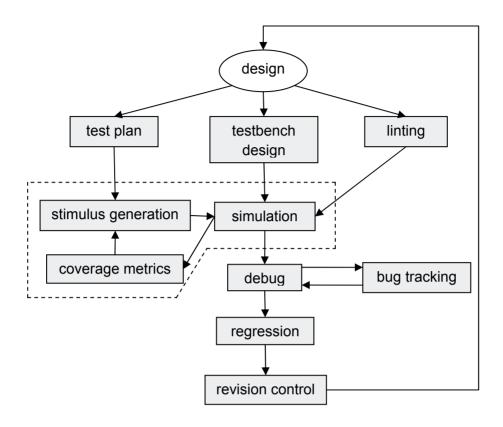

With the increase in complexity of modern integrated circuits, it has become imperative to address critical verification issues in the design cycle. The process of verifying correctness of designs takes roughly 70% of the design time [35]. For every designer the number of verification engineers can vary from 2 to 4 depending on the design complexity. The following aspects are the causes for the huge amount of resources spent on verification. First, design complexity increases. Second, historically more attention has been devoted to design process improvements that have produced significant progress in the design part, for example applying different automated tools for synthesis. However, verification process was not improved as much and has become a bottleneck.

For hardware verification, two types of methods are usually applied. These are formal methods and simulation-based verification. Formal methods use mathematical models to prove the correctness of the described model. Formal verification algorithmically and exhaustively explores all possible input values over time. However, formal verification can be performed only for limited design sizes due to the excessive time needed for proving the design correctness [66]. Thus, formal methods are applied only to some parts of the whole design

implementation. Simulation-based verification relies on design simulation under a set of stimuli. Usually simulation-based verification assumes comparison of current implementation against the specification or against the implementation on another abstraction level [43]. In this thesis only simulation-based hardware verification is considered. Both, formal methods and simulation-based verification only detect the presence of an error in the design implementation, often providing description of the cases causing this incorrect behavior. Finding an error and fixing it is usually the manual work of verification engineer.

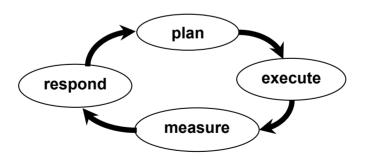

In order to verify the correctness of a design, different test cases are generated. Due to the fact that it is impossible to verify exhaustively all possible inputs and states of a design, the confidence level regarding the quality of the design must be quantified to control the verification effort. The fundamental question is: "How do I know if I have verified or simulated enough?" Verification coverage is a measure of confidence and it is expressed as a percentage of items verified out of all possible items. Different definitions of items give rise to different coverage measures or coverage metrics [43].

Various coverage metric classes exist such as code coverage, parameter coverage and functional coverage. Today, coverage-driven verification methodology is widespread, where verification progress is measured by achieving the coverage described by the coverage model. Coverage model consists of a set of various verification metrics and is built at the beginning of the design cycle. New methodology improves visibility into the verification process.

In this thesis, only code coverage would be used, which provides insight into how thoroughly the code of a design is exercised by a suite of simulations. The main disadvantage of code coverage metrics lies in the fact that they only measure the quality of the test case in stimulating the implementation and do not necessarily prove its correctness with respect to the specification. On the other hand, code coverage analysis is a well-defined, well-scalable procedure and, thus, applicable to large designs.

#### 1.2 Problem formulation

Traditional design implementation is done using hardware description languages such as VHDL [90] or Verilog [89] for example. In this thesis, simulation-based verification issues and fault simulation at RTL using high-level decision diagrams (HLDDs) as the design representation model are addressed. Previous research works, including [84][85], have shown that

HLDDs are an efficient model for hardware design simulation and fault modeling since it provides a fast evaluation by graph traversal and easy identification of cause-effect relationships. Methods presented in this work are based on HLDD representation. This representation gives us opportunity to find some uncovered holes in verification by providing an alternative view compared to traditional methods.

Efficient fault simulation algorithms for combinational circuits are known for decades. However, sequential fault simulation which is frequently used in test and fault tolerance applications remains a very time-consuming task, in particular for larger circuits [23]. In order to contend the complexity, the research community has turned towards developing methods at higher design abstraction levels. In this work, a new approach, which is applicable directly at the RTL, is proposed. Three typical methods of fault simulation at the gate-level exist: parallel, deductive and concurrent fault simulation. Deductive fault simulation is faster than the parallel one and consumes less memory resources than the concurrent one. However, to the best of author's knowledge, it has never been used at higher level of abstraction than gate-level. In this work, deductive fault simulation algorithm is transformed for the register-transfer level and applied to HLDD-based designs, which allows accelerating the fault simulation.

Comprehensive verification coverage metrics help evaluating verification progress and managing verification effort [65]. In this thesis, a method and a tool for fast analysis of classical code coverage metrics, such as statement, branch and toggle coverage, are presented. All these metrics are built into a simulation tool working on HLDD design representation. Correspondingly, those classical coverage metrics are mapped to HLDD constructs. Also HLDDs can be seamlessly applied to observability coverage analysis. Commonly used code coverage metrics only point controllability of items in implemented design while ignoring their observability at outputs [4]. Taking into account the observability of a coverage item gives more information to the verification engineer. An observability coverage metric based on the toggle coverage metric is also built into the simulation tool based on HLDDs.

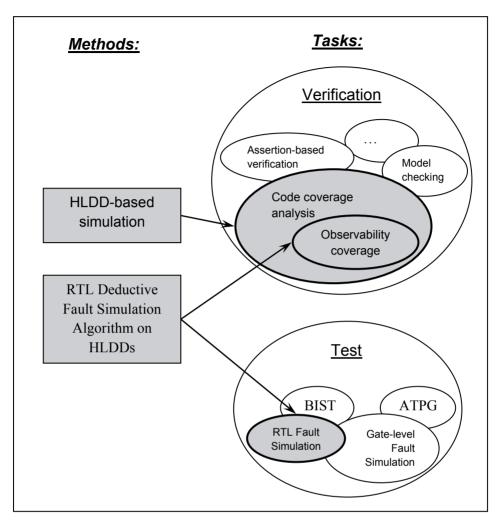

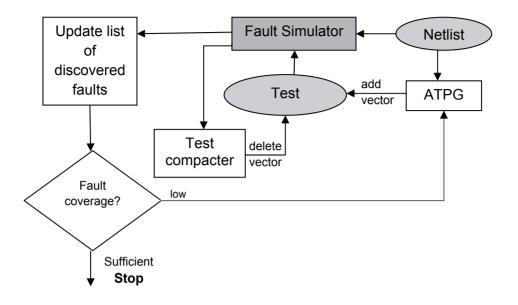

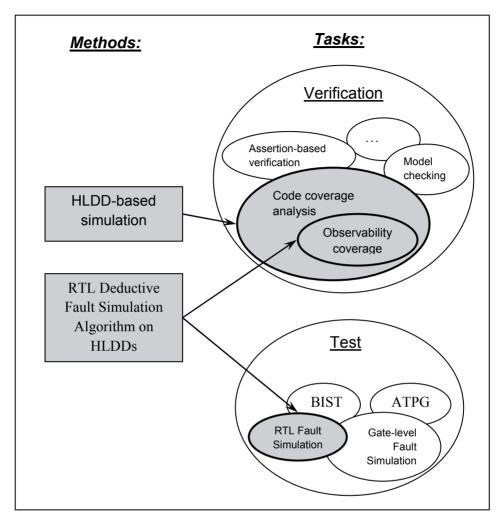

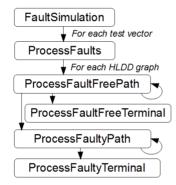

Figure 1.1 Developed methods & tasks (grey background) in general verification and test steps

#### 1.3 Contributions

The main contributions of this thesis are summarized below.

A new method for RTL fault simulation using High-Level Decision Diagrams was developed. This method was implemented using the deductive fault simulation algorithm. The initial deductive fault simulation algorithm, proposed by Armstrong for gate-level designs [3], was brought to RTL, where not only bits are taken into account when making decisions for fault lists propagation but word-level variables and arithmetic operations too. For fault

simulation, RTL bit coverage fault model is used, which has proven to provide a good correspondence with gate-level structural faults [29].

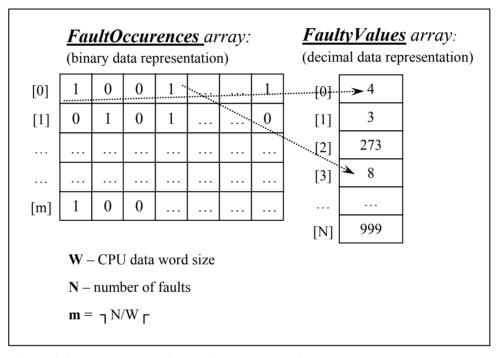

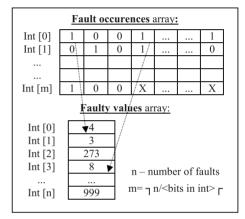

An efficient data structure implementation to speed up set operations in deductive fault simulation algorithm at RTL was developed. The faults are coded with bits the way that it would be possible to make fast bitwise set operations with fault lists. Faulty data of the faults is stored in an array, which is closely related to faults IDs.

Fast HLDD-based simulation was extended to support code coverage analysis, such as node coverage, edge coverage, toggle coverage. A method of mapping traditional code coverage metrics to High-Level Decision Diagrams (HLDD) was described.

Manipulations on HLDDs to find the best representation for code coverage analysis were defined.

An observability coverage metric based on the bit-coverage fault model was presented, which takes into account not only the controllability of an internal point of the design, but also the observability at the outputs. The observability coverage metric gives more information to verification engineer and allows detection of testability problems at an early stage of a design cycle. This metric was implemented on HLDDs using toggle coverage as a basis for bugs insertions. The proposed deductive fault simulation algorithm on RTL is applied as the bugs propagation algorithm.

All above described methods were successfully integrated into a single tool, which is based on the HLDD simulation engine. General view of the tool methods and implemented tasks is depicted in Figure 1.1. Developed methods and tasks are colored in grey. In this figure one can see that code coverage analysis is one of the verification tasks, where observability coverage is part of a code coverage analysis. For implementation of these tasks in the thesis the HLDD-based simulation and the RTL deductive fault simulation algorithm were used. Also, the RTL deductive fault simulation algorithm was used for RTL fault simulation, which is one of the test tasks.

#### 1.4 Thesis organization

This thesis consists of 6 chapters and 1 appendix.

Chapter 2 provides background information on related topics to this work. First, design representation by decision diagrams is presented including description of the High-Level Decision Diagram (HLDD) model. Second,

introduction to fault simulation is described, where different fault models are shown and different levels of abstraction for circuit design are presented. Also, classic fault simulation algorithms for the gate-level are described. Third, introduction to verification is given, where necessary definitions are presented.

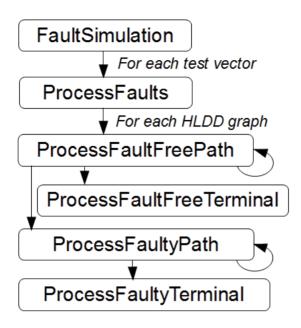

Chapter 3 starts with an overview of fault simulation. Then a new approach for fault simulation at the RTL using the HLDD design representation is presented in detail. The deductive fault simulation algorithm implemented at RTL is explained. An efficient implementation of algorithm's internal data structure for bitwise set operations is described. Then, results comparing RTL and gate-level fault simulations are presented.

Chapter 4 starts with an overview of code coverage for hardware designs. Code coverage metrics implemented on the HLDD simulation engine are presented. Then it is explained, how traditional code coverage metrics map to HLDDs and which representation of HLDDs better suits code coverage analysis. Experimental results for code coverage analysis are presented.

Chapter 5 starts with an overview of observability coverage analysis. Observability coverage metric presented in this thesis is defined. It is explained, how this observability coverage metric is built into the tool, implemented as the framework of this thesis. Experiments with measuring the observability coverage are shown and analysis of this metric is presented.

Chapter 6 concludes the thesis and discusses possible directions for future research.

The appendix presents research papers that form the basis for this thesis.

# Chapter 2 **BACKGROUND**

This chapter presents background on the topics related to the current research. First, the High-Level Decision Diagram (HLDD) model is introduced. Register-transfer level fault simulation and HDL code coverage presented in this work take advantage of a design representation by High-Level Decision Diagrams developed at Tallinn University of Technology [61]. HLDDs themselves are not contributions of this thesis. However, most of the contributions in this research rely on these models. Second, digital test concepts are introduced. Classical fault simulation methods based on the stuck-at fault model are presented. The algorithm for RTL fault simulation proposed in this thesis is based on a classical deductive fault simulation algorithm. Third, verification concepts are introduced, where code coverage related topics are described in details.

#### 2.1 Design representation by decision diagrams

The history of decision diagrams [61] based design representation goes back to seventies when the basic concept of *Binary Decision Diagrams* (BDD) was introduced. It was done by two authors, Raimund J. Ubar and Sheldon B. Akers, independently from each other in 1976 [81] and 1978 [2], respectively. In [81] decision diagrams were originally referred to as *alternative graphs*. During the following years, a number of works about using decision diagrams for test and simulation purposes were published, including [80] and [82]. However, it was not until the efficient Boolean manipulation method was presented by Randal E. Bryant in [11] when this type of representations became widely accepted by the research community.

Later, different special classes of binary decision diagrams have been proposed. They include Reduced Ordered BDDs (ROBDD) [11], multi-terminal

BDDs [17], edge-valued BDDs [42], binary moment diagrams [12], multivalued decision diagrams [72], functional decision diagrams (FDD) [41] and others.

There is a number of word-level Decision Diagrams based models used for design representation at the Register-Transfer and higher levels. *High-Level Decision Diagrams* (HLDDs) were proposed by Raimund Ubar in [83] and further developed by Jaan Raik in [60] and [61] and Anton Karputkin and Mati Tombak in [38]. The other examples are multi-terminal DDs (MTDDs) [17] and Assignment DDs (ADDs) [16] are some of them. However, in MTDDs the non-terminal nodes hold Boolean variables only. The principal difference between HLDDs and ADDs lies in the fact that ADDs' edges are not labeled by activating values. They are rather used as connecting signals to represent structure. In HLDDs, the selection of a node activates a path through the diagram, which derives the needed value assignments for variables. Furthermore, ADD model includes four types of nodes (read, write, operator, assignment decision). In HLDD the nodes are divided into non-terminal (control) and terminal (data) ones.

The following two subsections provide an introduction to BDD and to HLDD models correspondingly.

#### 2.1.1 Binary decision diagrams

This subsection presents the traditional BDDs, which are commonly used for representing Boolean functions. The general concept of BDD is explained and a widely used special class of BDDs, Reduced Ordered BDDs (ROBDD), is introduced.

A BDD is defined [61] as a directed acyclic graph with two terminal nodes, which are the *0-terminal* and *1-terminal* nodes. Each non-terminal node is labeled by an input variable of the Boolean function, and has two outgoing edges, called *0-edge* and *1-edge*.

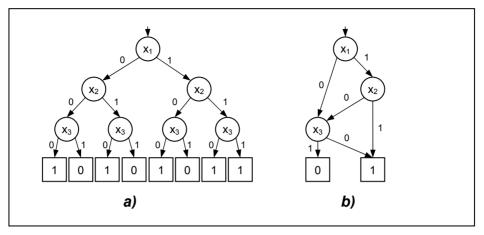

Figure 2.1 BDD representations for a Boolean expression  $(x_1 \cdot x_2) \lor \neg x_3$ ;

#### a) full tree BDD; b) ordered BDD

*Ordered BDD* (OBDD) is a BDD, where the input variables appear in a fixed order on all the paths of the graph and no variable appears more than once in a path. Figure 2.1 shows an example of a full tree BDD (a) and ordered BDD (b) corresponding to a Boolean function  $f = (x_1 \cdot x_2) \vee \neg x_3$ . In the binary tree, 0-and 1-terminal nodes represent logic values 0 and 1, and each node represents the *Shannon's expansion* of the Boolean function:

$$f = (\overline{x_i}.f_0) \lor (x_i.f_1),$$

where i is the index of the variable and  $f_0$  and  $f_1$  are the functions of the nodes pointed to by 0- and 1-edges, respectively.

*Reduced Ordered BDD (ROBDD)* is created by applying the following reduction rules to OBDD [11]:

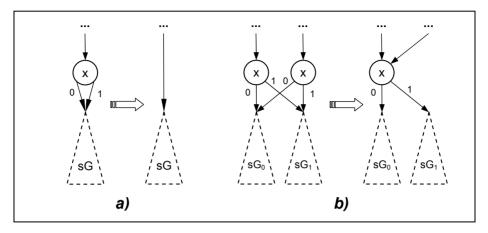

Reduction rule1: Eliminate all the redundant nodes where both edges point to the same node (Figure 2.2a).

*Reduction rule2*: Share all the equivalent sub-graphs (Figure 2.2b).

An important feature of ROBDDs is that they provide canonical forms for Boolean functions. This allows us to check the equivalence of two Boolean functions by merely checking isomorphism of their ROBDDs. This is a widely used technique in formal verification.

High-Level Decision Diagrams are derived from BDDs and used at a higher abstraction level of design representation, namely at word-level rather than Boolean-level. Below, explanation of this model is provided.

Figure 2.2 BDD reduction rules: a) reduction rule 1: eliminate all the redundant nodes, where both edges point to the same node; b) reduction rule 2: share all the equivalent sub-graphs

#### 2.1.2 High-level decision diagrams

In this subsection, description of the HLDD model is provided. High-Level Decision Diagrams can be viewed as a generalization of BDDs. HLDDs can be used for representing different abstraction levels from RTL to behavioral.

#### 2.1.2.1 HLDD model definition

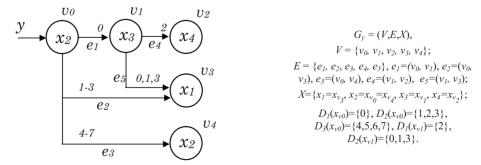

Below the High-Level Decision Diagram (HLDD) data structure is defined based on [38]. Consider a digital system (Z, F) as a network of subsystems or components, where Z is the set of variables (Boolean, Boolean vectors or integers), which represent connections between components, primary inputs and primary outputs of the network, and F is a set of discrete functions. Let  $Z = X \cup Y$ , where X is the set of function arguments and Y is the set of function values, where  $Q = X \cap Y$  is the set of state variables. D(z) denotes the finite set of all possible values for  $z \in Z$  and D(Z') is the set of all possible vectors for all  $Z' \subseteq Z$ . Obviously, if  $Z' = \{z_1, \ldots, z_n\}$  then  $D(Z') = D(z_1) \times \ldots \times D(z_n)$ . Let F be a set of discrete functions:  $y_k = f_k(X_k)$ , where  $y_k \in Y$ ,  $f_k \in F$ , and  $X_k \subseteq X$  (k iterates over all elements in F).

**<u>Definition 1.</u>** The high-level decision diagram representing a function

$f_k: D(X_k) \to D(y_k)$  is a directed acyclic graph G = (V, E) with one root node and a set of terminal nodes where:

- Each non-terminal node is labeled by some input or control variable  $x \in X$ . We shall denote the variable of node v by  $x_v$ .

- Each terminal node w is labeled by some function  $g_w : D(X_w) \to D(y_k)$  (possible a constant or single variable), where  $X_w \subseteq X_k$ .

- Each edge e from node v to u is labeled by a non-empty set of constants  $C \in D(x_v)$ . We denote such edge by (v, u, C).

- Each two edges  $e_1 = (v, u_1, C_1)$  and  $e_2 = (v, u_2, C_2)$  going from the same source node are labeled by different constants  $C_1 \cap C_2 = \emptyset$ .

- If the node v is labeled by  $x_v$  then the number of edges going from this node is  $|D(x_v)|$ .

In simple words, HLDD is a data structure similar to BDD, but with many edges originating from a particular node and a number of functions at the end, instead of constants 0 and 1. We shall denote the set of terminal nodes by  $V^T$ , the set of non-terminal nodes by  $V^N$  and the set of all successors of the v by  $\Gamma(v)$ . For non-terminal nodes  $v \in V^N$  an onto function exists between the values  $c \in D(x_v)$  of labels  $x_v$  and the successors  $v^c \in \Gamma(v)$  of v. By  $v^c$  we denote the successor of v for the value  $x_v = c$ .

The edge e, which connects nodes v and  $v^c$ , is called *activated* iff there exists an assignment  $x_v = c$ . Activated edges, which connect  $v_i$  and  $v_j$ , make up an *activated path*  $l(v_i, v_j) \subseteq V$ . An activated path  $l(v_0, v^T)$  from the root node  $v_0$  to a terminal node  $v^T$  is called the *main activated path* and  $v^T$  itself is referred to as the *activated terminal node*.

**Remark 1.** Every BDD is an HLDD as well, with two terminal vertices labeled by constant functions 0 and 1, and  $D(x) = \{0, 1\}$  for every variable x.

Without loss of generality we assume further that each variable has at least two values, i.e.  $\forall z \in Z$ , D(z) > 1. Let  $D_i$  designate a subset of  $D(x_v)$  labeling node v, such that assignments from it will activate its successor node  $v_i$ .  $D(x_v)$  is partitioned into non-intersecting sets  $D_1$ , ...,  $D_m$ , where  $m = |\Gamma(v)|$ . More formally,

$$\bigcup_{i=1}^{m} D_{i} = D(x_{v}) \wedge \forall i, j, i \neq j \rightarrow D_{i} \cap D_{j} = \emptyset.$$

<sup>&</sup>lt;sup>1</sup> Some of these variables are in fact atomic predicates but are treated as Boolean variables as there is no difference between a variable and a predicate in current context.

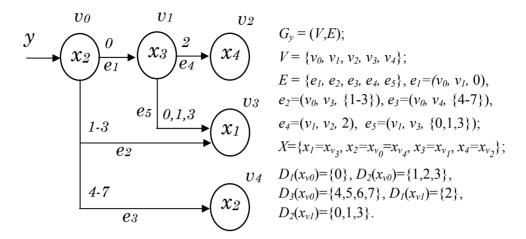

Figure 2.3 Graphical representation of a HLDD for function  $y=f(x_1, x_2, x_3, x_4)$

In other words, with every value assignment to variable  $x_v$  one and only one successor node will be activated. In the following graphical examples the edges are merged according to their successor node  $v_i$  and labeled by the corresponding domain partition  $D_i$ .

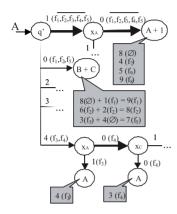

Figure 2.3 depicts a HLDD  $G_y$  representing a discrete function  $y=f(x_1,x_2,x_3,x_4)$ . The diagram contains five nodes  $v_0, \ldots, v_4$ . The root node  $v_0$  is labeled by variable  $x_2$  which is an integer with a range from 0 to 7. The node has three outgoing edges entering the nodes  $v_1, v_3$  and  $v_4$ . The node  $v_1$  is labeled by  $x_3$  with a range from 0 to 3. It has two outgoing edges  $e_4$  and  $e_5$  entering terminal nodes  $v_2$  and  $v_3$ , respectively. The edge  $e_4$  is activated by  $x_3=2$ , while the edge  $e_5$  is activated by  $x_3$  having a value 0, 1 or 3.

**<u>Definition 2.</u>** A HLDD  $G_k = (V, E)$  represents a function  $y_k = f_k(X_k)$ , iff for each assignment of variables in  $X_k$ , a main activated path exists, so that  $y_k = z(v^T)$  is valid.

Each function  $f_k \in F$  in the system (Z, F) is represented by a decision diagram  $G_k$ . Depending on the class of digital system (or level of its representation), we may have various DDs, in which nodes have different interpretations and relationships to the system structure. In RT level we usually decompose digital systems into control and data paths parts. State and output variables of the control part serve as addresses or control words, and the variables in the data paths part serve as data words. The functions of RTL components in the data paths are described by arithmetic operations on the word-level data variables. Non-terminal nodes in HLDDs correspond to control

paths and they are labeled by control variables or logical conditions, whereas terminal nodes correspond to data paths, and they are labeled by the data or functions on data.

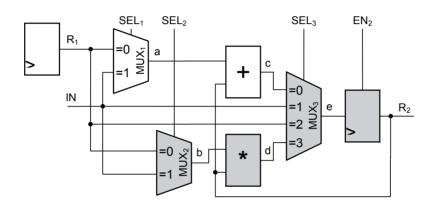

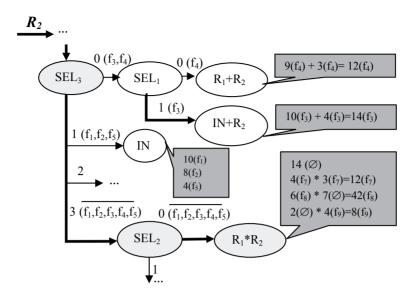

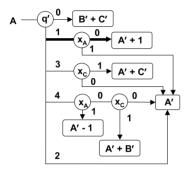

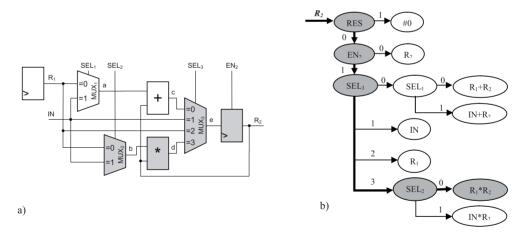

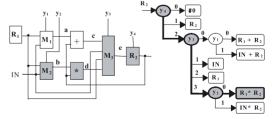

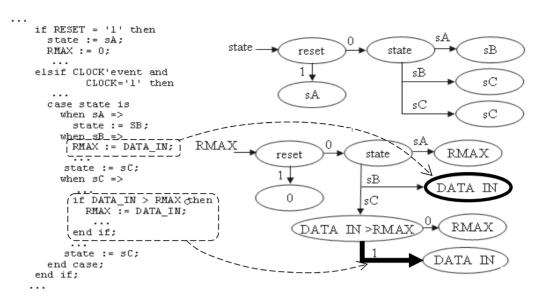

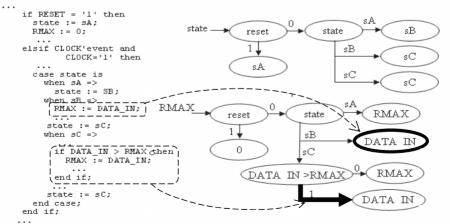

Figure 2.4 a) RTL schematic and b) its HLDD-based representation

## 2.1.2.2 Modeling RTL designs by HLDDs

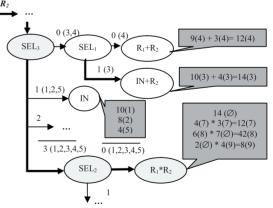

In Fig. 2.4a the datapath is depicted and its corresponding HLDD representation shown in Fig. 2.4b. Here, *R1* and *R2* are registers (*R2* is also a primary output), *MUX1*, *MUX2* and *MUX3* are multiplexers, + and \* denote addition and multiplication operations, *IN* is an input bus, *SEL1*, *SEL2*, *SEL3* represent multiplexer address signals, *EN2* serves as the signal for register *R2*, and *a*, *b*, *c*, *d* and *e* denote internal buses, respectively. In the HLDD, the control variables *RES*, *SEL1*, *SEL2*, *SEL3* and *EN2* are labeling internal decision nodes of the HLDD. The terminal nodes are labeled by a constant #0 (reset of *R2*), by word-level variables *R1* and *R2* (data transfers to *R2*), and by expressions related to the data manipulation operations of the network.

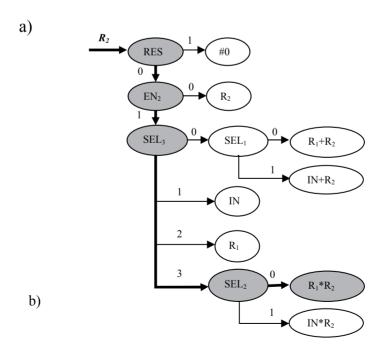

Consider, simulating HLDD with some values assigned to the variables. Let the value of SEL2 be 0, the value of SEL3 be 3, the value of EN2 be 1 and the value of RES be 0 in the current simulation run. By bold lines and grey nodes, a main activated path in the HLDD is shown from RES to R1\*R2, which corresponds to the pattern RES=0, EN2=1, SEL3=3, and SEL2=0. The activated part of the network at this pattern is denoted by grey boxes.

The main advantage and motivation of using HLDDs compared to the netlists of primitive functions is the increased efficiency of simulation and diagnostic modeling because of the direct and compact representation of cause-effect relationships. For example, instead of simulating the control word SEL1=0,  $SEL_2=0$ , SEL3=3, EN2=1, RES=0 by computing the functions a=R1, b=R1, c=a+R2, d=b\*R2, e=d, and R2=e, we only need to trace the nodes RES, EN2, SEL3 and SEL2 on the HLDD and compute a single operation R2=R1\*R2. In case of detecting an error in R2 the possible causes can be defined immediately along the simulated path through RES, EN2, SEL3 and SEL2 without complex diagnostic analysis inside the corresponding RTL netlist. The activated path provides the fault candidates, i.e. variables that are suspected to contain faults causing the error at R2 during current simulation run. Further reasoning should be based on analyzing sources of these signals.

#### 2.1.2.3 Basic simulation on HLDDs

Simulation on decision diagrams takes place as follows. Consider a situation, where all the node variables are fixed to some value. For each non-terminal node  $v_i \in V^N$  according to the value of the variable  $x_v = c$  certain output edge  $e = (v_i, v_i, C)$ ,  $v_i \in \Gamma(v_i)$  will be chosen, which enters into its corresponding

successor node  $v_j$ . Let us call such connections *activated edges* under the given values.

Succeeding each other, activated edges form in turn activated paths. For each combination of values of all the node variables there exists always a corresponding activated path from the root node to some terminal node. We refer to this path as the main activated path. The simulated value of variable represented by the HLDD will be the value of the function result of constant labeling the terminal node of the main activated path.

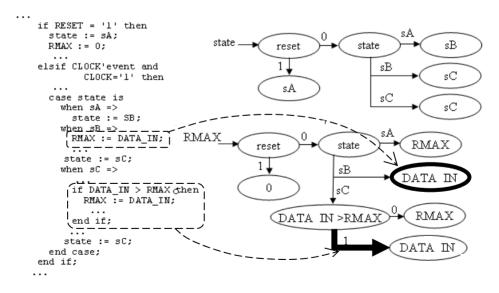

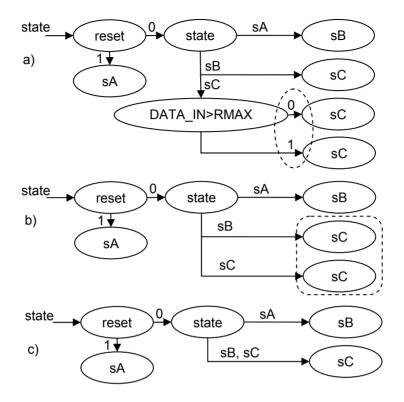

Algorithm in figure 2.5 presents the HLDD based simulation engine for RTL, behavioral and mixed HDL description styles and has been proposed in [85].

When representing systems by decision diagram models, in general case, a network of HLDDs rather than a single DD is required. During the simulation in HLDD systems, the values of some variables labeling the nodes of a HLDD are calculated by other HLDDs of the system.

Starting from the root node the outgoing successor is found according to the value of variable  $x_0$  labeling a node  $v_0$ . While the terminal node is not reached value of variable  $x_{current}$  activates edge  $e_{active}$  to the next successor node  $v_{next}$ . In the RTL style, the algorithm takes the previous time step value of variable  $x_{current}$  labeling a node  $v_{current}$  if  $x_{current}$  represents a clocked variable in the corresponding HDL. Otherwise, the present value of  $x_{current}$  will be used. In the case of behavioral HDL coding style HLDDs are generated and ranked in a specific order to ensure causality. For variables  $x_{current}$  labeling HLDD nodes the

```

for each diagram G in the model

v_{current} = v_0

Let x_{current} be the variable labeling v_{current}

while v_{current} is not a terminal node

if x_{current} is clocked or its DD is ranked after G then

v_{current} to else

v_{current} value = present time-step value of v_{current}

end if

v_{next} \in \Gamma(v_{current}), where v_{current}, v_{next} is a function then calculate a function;

assign v_{current} to the DD variable v_{current}

```

Figure 2.5 Algorithm1. Simulation engine on HLDDs

previous time step value is used if the HLDD diagram calculating  $x_{current}$  is ranked after current decision diagram. Otherwise, the present time step value will be used. Reaching the terminal node value of terminal variable is assigned to the graph variable y calculating first resulting value of a function if terminal node labels a function.

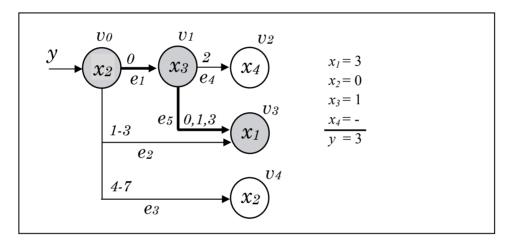

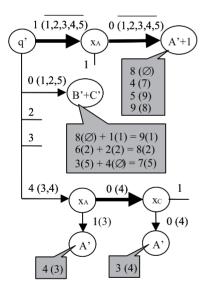

In Figure 2.6 example of simulation on the high-level decision diagram presented in Figure 2.3 is shown. Let assume that variable  $x_2$  is equal to 0, variable  $x_3 = 1$  and variable  $x_1 = 3$ . A path (marked by bold arrows) is activated from node  $v_0$  (the root node) to a terminal node  $v_3$  labeled by  $x_1$ . Thus,  $y=x_1=3$ . Note, that this type of simulation is event-driven since we have to simulate only those nodes that are traversed by the main activated path (marked by grey color in Figure 2.6).

Figure 2.6 Example of design simulation on HLDD

## 2.2 Fault Simulation

In this subsection introduction to fault simulation is done. First, role of testing is described. Then, different fault models are presented, which mathematically describe defects of the circuit. Afterwards, the most widespread algorithms for fault simulation are presented. Also, applications of fault simulation are defined.

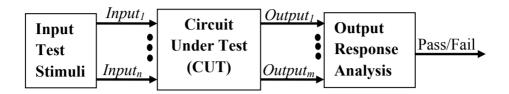

Figure 2.7 Basic testing approach [92]

## 2.2.1 The role of Testing

Reliability and testing techniques have become of increasing interest to different applications, including consumer electronics. A key requirement for obtaining reliable electronic systems is the ability to determine that the system is errorfree [9]. A test is a procedure which allows one to distinguish between good and bad parts. In this work we concentrate only on digital testing, i.e. input and output signals of the circuit can only take on the value 'logic 0' or 'logic 1'. Testing a circuit prior to its manufacturing is known as design verification. The question is not whether one should verify but how well to verify in order to have confidence that the device will comply with its specification [56]. This topic would be discussed in the next subchapter. The stress of this subchapter is testing a circuit after it is manufactured. Even though a circuit is designed errorfree, manufactured circuit may not function correctly. Since the manufacturing process is not perfect, some defects such as short-circuits, open-circuits, open interconnections, pin shorts, etc., may be introduced. Davis [20] points out that the cost of detecting a faulty component increases ten times at each step between prepackage component test and system warranty repair. Therefore, testing has become a very important aspect of any VLSI manufacturing system.

Testing typically consists of applying a set of test stimuli to the inputs of the *circuit under test* (CUT) while analyzing the output responses, as illustrated in figure 2.7. Circuits that produce the correct output responses for all input stimuli pass the test and are considered to be fault-free. Those circuits that fail to produce a correct response at any point during the test sequence are assumed to be faulty. Testing is performed at various stages in the lifecycle of a VLSI device [92]. In addition, a diagnosis of the failing circuit can be performed in order to identify the location and type of the defect.

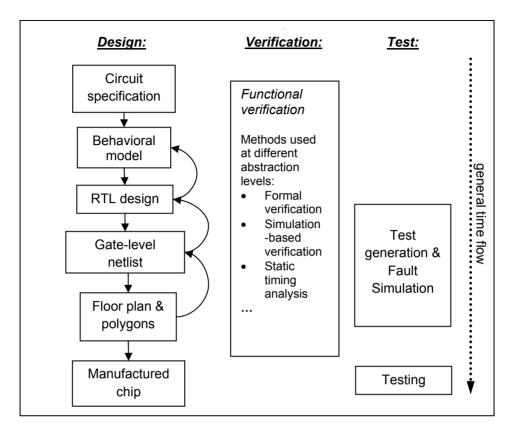

Figure 2.8 Top-Down design & test methodology

# 2.2.2 Top-Down Design and Test Methodology

A VLSI design can be described at different levels of abstraction. The design process is essentially a process transforming a higher level description of design to a lower level description either with a help of synthesis tools or by hand. One possible top-down design and test methodology is described in Figure 2.8. Starting from a circuit specification, a behavioral model of a circuit is developed in VHDL, Verilog, C or other language, program and simulated to determine if it is functionally equivalent to the specification. At the behavioral level functionality is modeled without regard to the hardware structure, electrical signals and detailed timing. Such models are useful as a proof-of-concept. The design is then described at the *register-transfer level* (RTL), which contains more structural information in terms of the sequential and combinational logic functions to be performed in the data paths and control

circuits. The RTL modules are validated as stand-alone components before integrating them into a system. The RTL description must be verified with respect to the functionality of the behavioral description before proceeding with logic synthesis to the gate level. Logic synthesis transforms the RTL description into an optimized technology-specific hardware description, generally in the form of a gate-level netlist (connectivity description of Boolean gates). The gate level structure of the design stabilizes only after the synthesized circuit has been verified through logic simulation. Once the design is verified, gate-level SSF (Single Stuck-Fault) models are used for test generation and fault simulation using the technology-specific (gate-level) netlist. In addition, the gate-level netlist serves as a common database for various post-synthesis steps such as timing simulation, placement, routing, static timing analysis, etc., until a prototype is fabricated.

## 2.2.3 Fault modeling

Below, some definitions of basic terms are presented.

**Definition 2.1.** A defect in an electronic system is the unintended difference between the implemented hardware and its intended design [13].

Defects occur either during manufacturing process or during the use of the device. Some typical defects are [13]:

- Process defects (imperfection of manufacturing process: missing of contact windows, parasitic transistors, oxide break-down, etc.)

- Materials defects (surface impurities, bulk defects, etc.)

- Age defects (electromigration, dielectric breakdown, etc.)

- Package defects.

**Definition 2.2**. A wrong output signal produced by a defective system is called an **error**. An error is an "effect" whose cause is some "defect" [13].

**Definition 2.3.** A representation of a "defect" at the abstracted function level is called a **fault**.[13]

**Definition 2.4.** *Test vector* is an input pattern applied to the circuit under test (CUT), and its responses are compared to the known good responses of a fault-free circuit.

In order to completely test a circuit, a sequence of test vectors is required; however, it is difficult to know how many test vectors are needed and the order

of test vectors in a sequence to guarantee a satisfactory reject rate. The effectiveness of the test sets is usually measured by the *fault coverage* and is defined as:

$$fault\ coverage = \frac{number\ of\ detected\ faults}{total\ number\ of\ faults}$$

The set of test vectors is complete if its fault coverage is 100%. This level of fault coverage is desirable but rarely attainable in most practical circuits. Moreover, 100% fault coverage does not guarantee that the circuit is fault-free. The fault coverage is calculated using a *fault simulator*.

**Definition 2.5** Fault simulator is a logic simulator in which faults are injected at the appropriate nets of the circuit, usually one at a time. The responses of the circuit to test vectors are compared with the good responses of the circuit. The fault is considered detected if at least one of the test pattern has a response different from the good circuit response.

Fault simulator typically works with a specific fault model. Because of the diversity of physical defects, it is impractical to work with real defects. *Fault models* were introduced to offer a simplified mathematical description of the erroneous behavior. Although most of the fault models do not provide exact description of the erroneous behavior of the circuit, they are very useful for generating and evaluating the quality of tests. A good fault model should satisfy two criteria: it should accurately reflect the behavior of defects, and it should be computationally efficient in terms of fault simulation and test pattern generation. Many fault models have been proposed, e.g. single stuck-at faults, transition faults, gate-delay faults, bridging faults [13], but, unfortunately, no single fault model accurately reflects the behavior of all possible defects that can occur. As a result, a combination of different fault models is often used.

Generally any fault model can be divided into two classes: single-fault model and multiple-fault model. For single-fault model it is assumed that only single fault can occur in the circuit at the time. A multiple-fault represents a condition caused by simultaneous presence of a group of single faults. For a given fault model let m be different type of faults that can occur at potential fault site and n be possible fault sites. Then for single-fault model number of possible faults equal to m\*n and for multiple-fault model number of possible faults equal to  $(m+1)^n$  -1. Because latter amount of faults is too large even for small values of m and n, the single-fault assumption is usually considered in practice. Fortunately, tests for single stuck-at faults are known to cover a very high percentage (greater than 99.6%) of multiple stuck-at faults when the circuit is large and has several outputs [13].

Modeling of faults is closely related to the modeling of the circuit. Different levels of abstraction are used in the top-down design methodology. The *behavioral level* has fewer implementation details and fault models at this level may have no obvious correlation to manufacturing defects. Behavioral level fault models play greater role in the simulation-based design verification, than in testing. The *RTL level* faults usually imitate gate level stuck-at faults at the higher level of abstraction. Commonly this is not one to one correspondence. The *logic level* or *gate level* consists of a netlist of gates and the stuck-at faults at this level are the most popular fault models in digital testing. Other fault models at this level are bridging faults and delay faults. *Transistor* and other *lower levels* include technology-dependent faults, e.g. stuck-open faults.

Behavioral faults: Usually, the behavior of electronic system is described in a programming language, e.g. C, or in some hardware description language such as VHDL, Verilog. At the behavioral level the variables are not necessarily electrical, but correspond to a specific application domain. Behavioral faults refer to incorrect execution of the language constructs used in the program. Examples of behavioral faults are assertion faults, branch faults, and instruction faults. At the behavioral level, different coverage metrics (statement coverage, branch coverage, toggle coverage) can be used to measure efficiency of the test, although these do not conform to any specific fault model [13].

**RTL faults**: Straightforward extension to the stuck-at-fault model is to replace the concept of a signal line that is stuck with that of an internal RTL variable being stuck. Further it is possible to differentiate between *data faults* and *control faults*, depending on the type of the stuck variable [1].

- Typical *data faults* are register or memory bits that are stuck. Data faults are stuck-at-0 and stuck-at-1 faults: when the fault is present, the affected object (a signal or a variable representing memory element) loads the correct value, except for one bit that remains stuck to 0 or 1.

- Control faults are defined on variables that control conditional operations. These are stuck-at-then and stuck-at-else faults for *if* statements and selection faults for *case* statements. It is allowed having a stuck fault to the result of any expression that is part of a condition or the entire condition itself.

**Logical faults** represent the effect of physical faults on the behavior of the modeled system. Many physical faults can be modeled by the same logical fault. Logical faults affect the state of logical signals. Normally, the state is modeled

as {0, 1, X, Z}, and a fault transform the correct value to any other value. Several types of faults can be modeled at this level. However, the term *logical fault* often implies stuck-at faults.

Lower level faults are not part of this work therefore their description is out of the scope of the thesis. As the Single Stuck-Fault (SSF) model is used as the basis for RTL level faults model, more detailed description of the SSF model is provided below.

SSF (Single Stuck-at Fault) model is a logical fault model that is most commonly used in digital testing [35]. A stuck-at fault is assumed to affect only the interconnections between gates. A single stuck-at fault (stuck-at-0 or stuck-at-1) represents a line in the circuit that is fixed to logic value 0 or 1, irrespective to the correct logic output of the gate driving it.

The SSF model is widely used, its usefulness results from the following attributes [1]:

- It represents many physical faults.

- It is independent on technology, as the concept of a signal line being stuck at a logic value can be applied to any structural model.

- Experience has shown that SSFs detect many non-classical faults as well.

- Compared to other fault models, the number of SSFs in the circuit is small. Moreover, the number of faults to be explicitly analyzed can be reduced by fault-collapsing techniques.

- SSFs can be used to model other types of faults.

- High SSFs coverage provides a high multiple stuck-at faults coverage.

In this work, two fault models: the SSF model and the RTL bit coverage fault model [29] - are used for fault simulations. A detailed description of fault simulation methods and experiments will be provided in the next chapter. Comparative table of the properties of the fault models is given below. It is important to mention that there is no one to one correspondence between SSF faults and RTL faults because for a given RTL description several gate-level implementations exist.

**Table 1 Properties of fault models**

| Gate level SSF model                                        | RTL bit coverage fault model [29]                   |

|-------------------------------------------------------------|-----------------------------------------------------|

| Boolean components are assumed to                           | Language operators are assumed to be                |

| be fault-free                                               | fault-free                                          |

| Signal lines contain faults:                                | Variables contain faults:                           |

| • Stuck-at-0 fault when the logic level is fixed at value 0 | • Stuck-at-0 fault when the bit is fixed to value 0 |

| • Stuck-at-1 fault when the logic level is fixed at value 1 | • Stuck-at-1 fault when the bit is fixed to value 1 |

| According to SSF assumption, only                           | Single fault assumption: only one fault             |

| one fault is applied at a time when the                     | is applied at a time when the test set is           |

| test set is evaluated                                       | evaluated                                           |

#### 2.2.4 Fault simulation

Simulation is the process of predicting the behavior of a circuit design before it is manufactured. For digital circuits, simulation serves dual purposes. First, during the design stage, logic (fault-free) simulation helps the designer verify that the design works according to the functional specifications. Verification with the help of simulation techniques will be part of the next subchapter. Second, during test development, fault simulation is applied to simulate faulty circuits. Definition of fault simulator is given in the previous subchapter. To summarize, a fault simulator must classify given modeled faults in a circuit as detected or undetected with given test vectors. Fault simulator determines the efficiency of test vectors in detecting the modeled faults of interest.

The section below presents the key fault simulation techniques based on the single stuck-at fault model. These techniques can be reused with modifications on other fault models as well as at other abstraction levels. Since these algorithms were developed for SSF model the explanations would be given on this model. Further, RTL fault simulation features would be shown.

#### 2.2.4.1 Serial Fault Simulation

Serial fault simulation is the simplest fault simulation technique. First, the circuit is simulated in a fault-free mode for all test vectors and fault-free output values are stored. Then the fault simulator simulates faults one by one. For each

fault, fault injection is performed, which modifies original circuit to mimic the circuit behavior in the presence of the fault. As simulation proceeds, the output values of fault simulation are compared with stored fault-free output values for all test vectors. All faults are simulated serially in this way. This kind of simulation is very time consuming. To improve the fault simulation performance, fault dropping is used. Halting the simulation as soon as comparison indicates detection of the target fault is called fault dropping.

The major advantage of serial fault simulation is its ease of implementation. It can simulate wide range of fault models, as long as the fault effect can be properly injected into the circuit. The major disadvantage of serial fault simulation is its low performance. There exists more intelligent algorithm to reduce the effort of fault simulation. These general algorithms are parallel [67], deductive [3] and concurrent [87] fault simulation techniques. They differ from the serial method in two fundamental aspects [1]:

- They determine the behavior of the circuit in the presence of faults without explicitly changing the model of the circuit.

- They are capable of simultaneously simulating a set of faults.

Two of these algorithms will be described in the following sections.

#### 2.2.4.2 Parallel Fault Simulation

Parallel fault simulation benefits on the bitwise parallelism of logical operations in a digital computer in order to reduce computational time. For example, for a 32-bit machine word, logic operations such as AND, OR, XOR etc. can be performed on all 32 bits at once. The idea of parallel fault simulation belongs to [67]. It is assumed that signals work on logic 0 and/or 1. It is possible to expand 2-bit signal logic to wider coding such as X and Z values, but this method would require special encoding.

In parallel fault simulation w-I faults would process in one pass, where w is the machine word size. One bit of w is used for fault-free value and other w-I bits are values of signals in the faulty circuits for w-I faults. Each bit of a word represents a signal value in a different circuit. The injection of a fault is done by changing the value of a bit corresponding to a signal value in a circuit. If the number of simulated faults is more than the machine word size, then more than one pass of fault simulation is required to simulate all faults. The technique of fault dropping can be applied in parallel fault simulator as well as in serial fault simulator to reduce computational time, however the simulation pass would

Figure 2.9 Parallel fault simulation

terminate only when all faults of the pass would be detected. Therefore, serial fault simulation gains more by fault dropping.

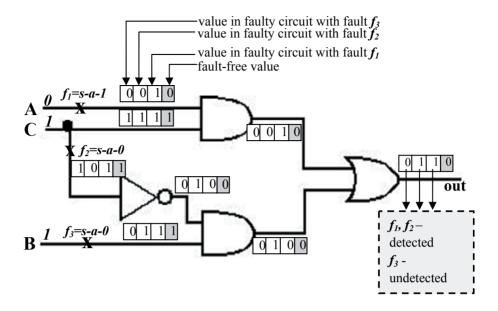

Consider an example of a multiplexer at the gate level (Figure 2.9). In this example, test vector ACB=011 is applied to the inputs. Three faults  $f_1$  (s-a-1),  $f_2$  (s-a-0),  $f_3$  (s-a-0) are injected into the circuit. Therefore, a packet of 4 bits is required for logic operations of parallel simulation, where 3 bits are used to encode values of the signals in faulty circuits and 1 bit is used for the fault-free circuit. To simulate in parallel, the signal of each line in a circuit is expressed as a word where 4 left-most bits are useful for simulation in this example. The bit, which represents faulty value of a signal in faulty circuit, is changed to the stuck-at value, other bits remain the same. During the simulation, the effect of the faulty value propagates towards the output. For example, fault  $f_1$  is present only in the first circuit, thus second bit of signal A is changed to 1. Performing logic operations we obtain output out=0110. Faults  $f_1$  and  $f_2$  are detected because bits in the output signal representing faulty circuits with these faults differ from fault-free bit value; fault  $f_3$  is not detected because its bit value is equal to the fault-free bit value.

Parallel fault simulation is approximately w times faster in comparison with serial fault simulation. However, it has limitations as well. It becomes impractical for multi-valued logic. And as it was mentioned above, the fault dropping technique is not as effective as for serial fault simulation.

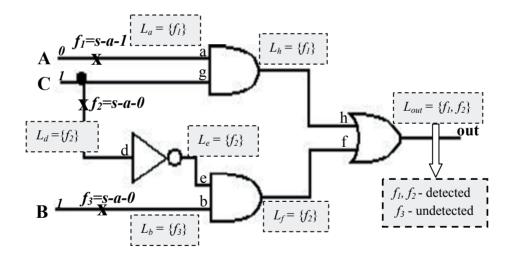

#### 2.2.4.3 Deductive Fault Simulation

In deductive fault simulation [3] only the fault-free circuit is simulated and the behavior of all faulty circuits is based on logic reasoning. All signal values of faulty circuits are deduced from fault-free circuit signal values and the structure of a circuit. All deductions are carried out simultaneously and only one fault-free simulation is performed. Thus deductive fault simulation can be very fast. It is possible theoretically to deduce all signal values, however practically this depends on the size of the available memory. Fault effects are represented by the fault list. A *fault list*  $L_i$  is associated with every signal i.  $L_i$  is a set of faults that cause the value of signal i to differ from its fault-free value. If signal i is a primary output then the fault list associated with i is the set of faults detected at this output. Thus the aim of the deductive fault simulator is eventually to construct a set of detected faults by uniting fault lists of all primary outputs. Based on logic reasoning, the process of deriving the fault list of a gate output from those of the gate inputs is called *fault list propagation* [92].

Let us see the procedure of fault list propagation in general. In deductive fault simulation it is important to know either the gate input holds a controlling value or a non-controlling value. The *value* of an input is said to be *controlling* if it determines the value of the gate output regardless of the values of the other inputs [1]. For example, a controlling value for an AND gate is 0 (because appearance of 0 at least in one of the inputs of an AND gate will force the output of the gate into 0), for an OR gate is 1, etc. Let I be a set of inputs of a gate Z. Let C be a set of inputs with controlling value C, where  $C \subseteq I$ . C is an output signal of gate C. The fault list C0 gate C1 is computed as follows where 2 cases are recognized:

1) If

$$C = \emptyset$$

then  $L_Z = \{ \bigcup_{i \in I} L_i \} \cup \{ fault z \}$

This means, that if all inputs have non-controlling values, then all faults observed at the inputs propagate to the output of the gate adding a fault of the output signal line. In the example in Fig. 2.10 this is computation of  $L_{out}$ , because the OR gate has inputs 00, which both are non-controlling values for the OR gate.

2) If

$$C \neq \emptyset$$

then  $L_Z = \{\bigcap_{j \in C} L_j\} - \{\bigcup_{j \in I - C} L_j\} \cup \{fault z\}$

This means, that if some of the inputs has the controlling value c, only faults of these inputs propagate to the output taking into account the self-masking effect - the appearance of the same fault at any of non-controlling inputs, which faults are excluded at the fault list of the gate

output. As in the previous case, the fault of the output signal line is added. In the example in Fig. 2.10,  $L_h$  and  $L_f$  are calculated with this formula, because both AND gates have in one input the controlling value 0 and in the other input non-controlling value 1.

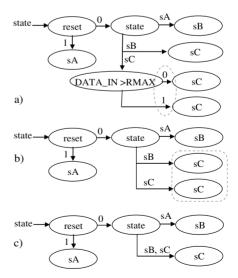

Consider the same multiplexer example (Figure 2.10). Let input vector to the schematic be the same ACB = 011. Also, the same faults f1 (s-a-1), f2 (s-a-0), f3 (s-a-0) are injected into the circuit. Faults are propagated by computation of fault lists at every signal line of a circuit: