### THESIS ON INFORMATICS AND SYSTEM ENGINEERING C42

# Simulation-Based Hardware Verification with High-Level Decision Diagrams

MAKSIM JENIHHIN

### TALLINN UNIVERSITY OF TECHNOLOGY

Faculty of Information Technology Department of Computer Engineering Chair of Computer Engineering and Diagnostics

This dissertation was accepted for the defence of the degree of Doctor of Philosophy in Computer and Systems Engineering on November 5, 2008

Supervisors: Dr. Jaan Raik

Prof. Raimund Ubar

Opponents: Prof. Franco Fummi, University of Verona, Italy

Dr. Rainer Dorsch, IBM, Böblingen, Germany

Defence: December 8, 2008

### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted before for any degree or examination.

/Maksim Jenihhin/

Copyright: Maksim Jenihhin, 2008

ISSN 1406-4731

ISBN 978-9985-59-863-4

### INFORMAATIKA JA SÜSTEEMITEHNIKA C42

# Simuleerimisel põhinev riistvara verifitseerimine kõrgtaseme otsustusdiagrammidel

**MAKSIM JENIHHIN**

### **Abstract**

This thesis addresses the main simulation-based hardware verification issues that are speed and accuracy of the verification process. In particular we target aspects of assertion checking and coverage measurement by exploiting advantages of High-Level Decision Diagrams (HLDD) design representation model.

First, we present a novel method for assertion checking based on HLDD model. The presented approach proposes a temporal extension for the existing HLDD model aimed at supporting temporal properties expressed in Property Specification Language (PSL). Other contributions of this method are methodology for direct conversion of PSL properties to HLDD and HLDD-based simulator modification for assertions checking support.

Second, we present a novel method for verification structural coverage analysis based on HLDD model. The main contributions of this method include approaches for mapping traditional code coverage metrics such as statement, branch and data flow coverage to HLDD constructs. Another contribution is an approach for condition coverage metric analysis. It employs a hierarchical decision diagrams model consisting of HLDDs and BDD-based representations of the conditional statements. The method also implies HLDD model manipulations targeting different aspects of verification coverage analysis.

The proposed methods rely on homogeneous hardware verification flow based on HLDD model. Previous research works have shown that HLDDs are an efficient model for simulation and convenient for diagnosis and debug. The performed experiments demonstrate feasibility and efficiency of the proposed approaches.

### Kokkuvõte

Antud töö on suunatud simuleerimisel-põhineva digitaalriistvara verifitseerimise kiiruse ja täpsuse tõstmisele. Töös on pakutud lähenemised väidete kontrolli ja verifitseerimise katte mõõtmise jaoks, mis rakendavad kõrgtaseme otsustusdiagrammide (KTOD) eeliseid skeemide esitamisel.

Esiteks on esitatud uudne meetod väidete kontrolliks, mis põhineb KTOD mudelil. Esitatud lähenemine pakub välja temporaalse laienduse olemasolevale KTOD mudelile, mis on mõeldud Property Specification Language (PSL) keeles esitatud omaduste toetamiseks. Lisaks on töös esitatud metodoloogia PSL omaduste vahetuks konverteerimiseks KTOD mudelisse ja KTOD simulaatori edasiarendus väidete kontrolli toetamiseks.

Teiseks on dissertatsioonis välja töötatud meetod verifitseerimise struktuurse katte KTOD mudelil põhinevaks analüüsiks. Meetodi peamiseks panuseks on traditsiooniliste kattemõõtude, nagu lausete, harude ja andmevoo katete sidumine KTOD struktuuriga. Lisatulemuseks on lähenemine tingimuste katte analüüsiks. Vimmane kasutab hierarhilist otsustusdiagrammide mudelit, mis koosneb KTOD-dest ja tingimuslike lausete binaarsetel otsustusdiagrammidel põhinevast esitusest. Samuti sisaldab pakutud meetod KTOD mudeli teisendusi, mis on suunatud verifitseerimise katte analüüsi erinevatele tasemetele.

Pakutud meetodid toetuvad homogeensele KTOD-l põhinevale riistvara verifitseerimise voole. Eelnev uurimistöö on näidanud, et KTOD on efektiivne mudel simuleerimise läbiviimiseks ning sobilik digitaalsüsteemide diagnostikat ja silumist silmas pidades. Dissertatsioonis teostatud katsed tõestavad pakutud lähenemiste rakendatavust ja efektiivsust.

## Acknowledgements

I would like to express my sincere gratitude to everybody who has either directly or indirectly contributed to my PhD studies and this thesis.

In particular, I would like to thank my supervisors. I very much appreciate the support and advice of Dr. Jaan Raik. He has been guiding me through my PhD studies and has been not only an excellent teacher but also a friend. I am very much thankful to Prof. Raimund Ubar for bringing me to the exiting world of science and research. I was always getting a wise advice from him just at the time when it was needed.

I would also like to thank all my colleagues from Tallinn University of Technology and especially from Dept. of Computer Engineering who contributed to my work with discussions and ideas. In particular I would like to mention here in alphabetical order: Anton Chepurov, Sergei Devadze, Prof. Peeter Ellervee, Dr. Gert Jervan, Dr. Artur Jutman, Uljana Reinsalu and Assoc.Prof. Aleksander Sudnitsõn.

A special thank should go to the director of Dept. of Computer Engineering Dr. Margus Kruus for his support with many practical and administrative issues.

I would like to acknowledge several organizations that have supported my PhD studies, including the research presented in this thesis. They are Tallinn University of Technology, Enterprise Estonia funded ELIKO Development Centre, European Commission FP6 research project VERTIGO, National Graduate School in Information and Communication Technologies (IKTDK) and Estonian Information Technology Foundation (EITSA).

Finally, I would like to thank my family for all the patience and support. In particular I would like to mention my parents Vyacheslav and Olga, sister Anastasia and my beloved fiancée Anna. Thank you!

Maksim Jenihhin, Tallinn, October 2008

# **Table of Contents**

| Chapter 1 INTRODUCTION                                  | 1  |

|---------------------------------------------------------|----|

| 1.1 Motivation                                          | 1  |

| 1.2 Problem formulation                                 | 3  |

| 1.3 Contributions                                       | 4  |

| 1.4 Thesis organization                                 | 4  |

| 1.4.1 Formatting remarks                                | 5  |

| Chapter 2 BACKGROUND                                    | 7  |

| 2.1 Design representation by decision diagrams          | 7  |

| 2.1.1 Binary decision diagrams                          | 8  |

| 2.1.2 High-level decision diagrams                      | 10 |

| 2.1.2.1 HLDD model definition                           | 10 |

| 2.1.2.2 Basic simulation on HLDDs                       | 11 |

| 2.1.2.3 Pure RTL designs representation by HLDDs        | 12 |

| 2.1.2.4 Behavioural RTL designs representation by HLDDs | 15 |

| 2.1.2.5 HLDD vs. ADD representations comparison         | 18 |

| 2.1.2.6 HLDD model advantages for debug in verification | 20 |

| 2.2 Property specification language                     | 21 |

| 2.2.1 PSL organization                                  | 22 |

| 2.2.1.1 Flavors                                         | 23 |

| 2.2.1.2 Modes                                           | 23 |

| 2.2.1.3 Layers                                          | 24 |

| 2.2.1.4 Styles                                          | 25 |

| 2.2.2 PSL properties                                    | 25 |

| 2.2.2.1 Operators                                       | 26 |

| 2.2.2.2 Strong vs. weak operators                       | 28 |

| 2 2 2 3 Vacuous pass                                    | 28 |

| 2.2.2.4 PSL flexibility and common equivalences             | 28 |

|-------------------------------------------------------------|----|

| 2.2.3 PSL simple subset                                     | 30 |

| 2.3 Chapter summary                                         | 31 |

| Chapter 3 ASSERTION-BASED VERIFICATION                      | 33 |

| 3.1 Overview                                                | 34 |

| 3.1.1 Design flow                                           | 34 |

| 3.1.2 Design verification                                   | 35 |

| 3.1.3 Assertion-based verification                          | 36 |

| 3.1.3.1 Diversity of assertion checking                     | 38 |

| 3.1.4 State of the art                                      | 38 |

| 3.1.4.1 An experience with FoCs                             | 40 |

| 3.1.5 APRICOT                                               | 42 |

| 3.2 Temporal extension for the HLDD model                   | 44 |

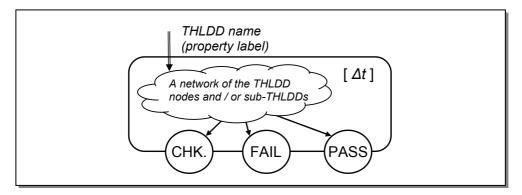

| 3.2.1 THLDD model definition                                |    |

| 3.2.2 THLDD interface                                       | 46 |

| 3.2.3 THLDD temporal relationships                          | 47 |

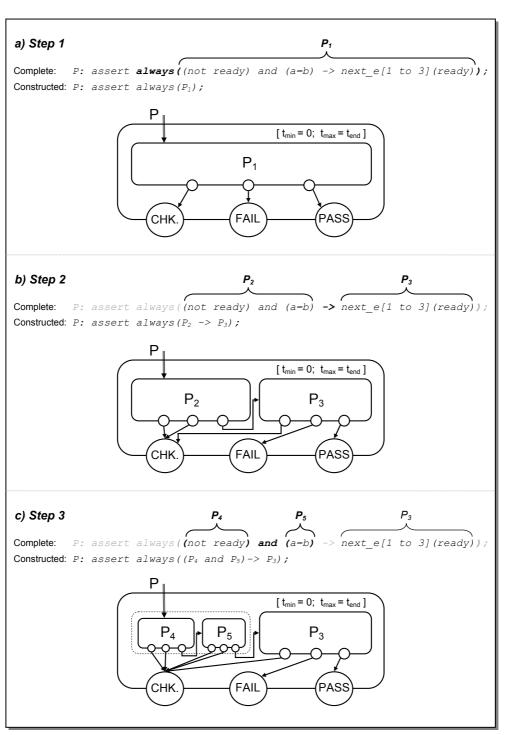

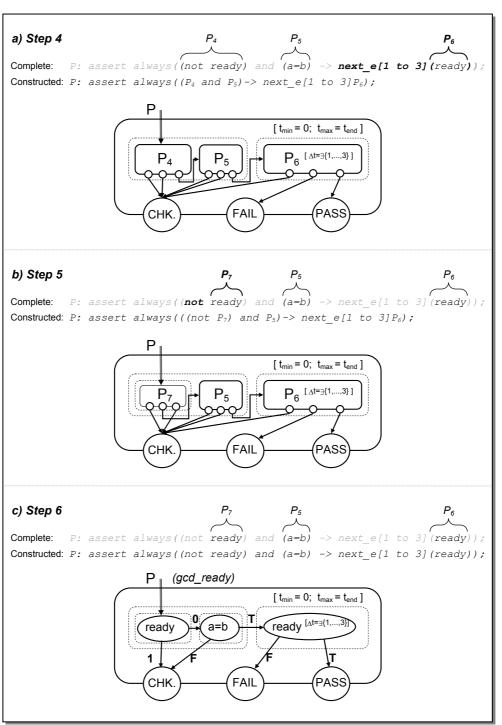

| 3.3 PSL to THLDD conversion method                          | 48 |

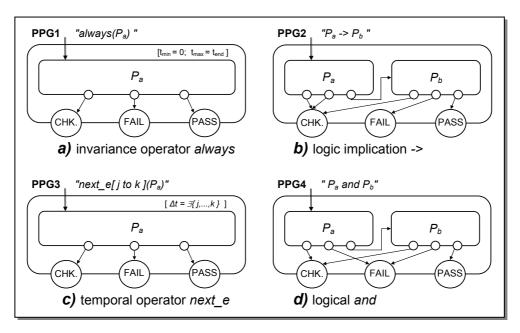

| 3.3.1 Primitive Property Graphs                             | 48 |

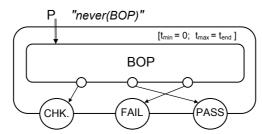

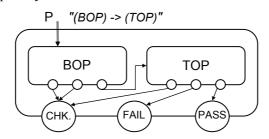

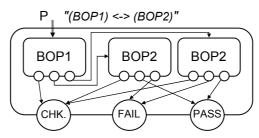

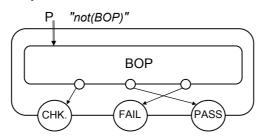

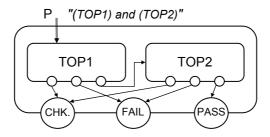

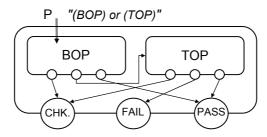

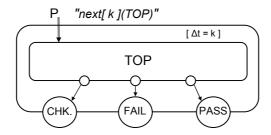

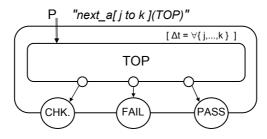

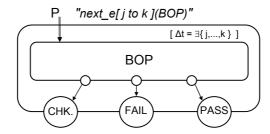

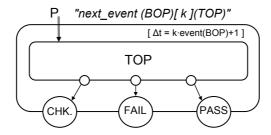

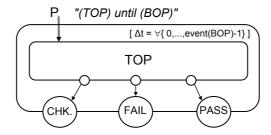

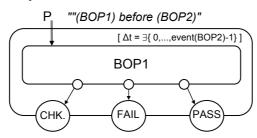

| 3.3.1.1 PPG Library                                         | 49 |

| 3.3.2 Parser                                                | 50 |

| 3.3.3 Constructor                                           | 51 |

| 3.3.4 Representation types of THLDD properties              | 55 |

| 3.4 The method for assertions checking with HLDDsim         |    |

| 3.4.1 HLDDsim algorithm                                     | 58 |

| 3.4.2 HLDDsim modification for assertions checking          | 59 |

| 3.4.3 THLDD assertions checking timing issues               | 61 |

| 3.5 Experimental results                                    | 63 |

| 3.6 Verification assertions reuse for manufacturing testing | 65 |

| 3.6.1 Assumption-based test generation                      | 66 |

| 3.6.2 Assertion-based BIST                                  | 68 |

| 3.6.3 Assertion-based DfT by test points insertion          | 69 |

| 3.7 Chapter summary                                         | 70 |

| Chapter 4 VERIFICATION COVERAGE ANALYSIS                    | 71 |

| 4.1 Verification coverage overview                          |    |

| 4.1.1 Verification coverage classification                  |    |

| 4.1.2 Sufficiency of verification coverage                  | 74 |

| 4.1.3 Assertion coverage                                    |    |

| 4.2 HLDD-based analysis of code coverage                    | 76 |

| 4.2.1 Statement coverage mapping                                       | 77  |

|------------------------------------------------------------------------|-----|

| 4.2.2 Branch coverage mapping                                          | 78  |

| 4.2.3 Toggle coverage mapping                                          | 80  |

| 4.2.4 State coverage mapping                                           |     |

| 4.2.5 Data flow coverage mapping                                       | 81  |

| 4.2.6 Condition coverage mapping                                       | 81  |

| 4.3 A hierarchical approach for HLDD-based condition coverage analysis | 82  |

| 4.4 HLDD model reduction manipulations for code coverage analysis      | 85  |

| 4.5 Experimental results                                               | 89  |

| 4.6 Chapter summary                                                    | 91  |

| Chapter 5 CONCLUSIONS AND FUTURE WORK                                  | 93  |

| 5.1 Conclusions                                                        | 93  |

| 5.1.1 Contributions                                                    | 93  |

| 5.1.2 Advantages                                                       | 94  |

| 5.2 Future work                                                        | 95  |

| References                                                             | 97  |

| Appendix A PPG LIBRARY                                                 | 107 |

| Appendix B AGM FORMAT                                                  | 123 |

### **List of Publications**

### HLDD-based functional verification flow

- Maksim Jenihhin, Jaan Raik, Anton Chepurov, Raimund Ubar "Temporally Extended High-Level Decision Diagrams for PSL Assertions Simulation", *Proc. of 13th IEEE European Test Symposium (ETS'08)*, Verbania, Italy, May 25-29, 2008, pp. 61-68

- Maksim Jenihhin, Jaan Raik, Anton Chepurov, Raimund Ubar, "PSL Assertion Checking with Temporally Extended High-Level Decision Diagrams", *Proc. of 9th IEEE Latin American Test Workshop (LATW'08)*, Puebla, Mexico, February 17-20, 2008, pp. 49-54

- Maksim Jenihhin, Jaan Raik, Anton Chepurov, Raimund Ubar, "Assertion Checking with PSL and High-Level Decision Diagrams", *Digest of the IEEE 8th Workshop on RTL and High Level Testing (WRTLT'07)*, Beijing, China October 12-13, 2007, pp. 105-110

- Maksim Jenihhin, Jaan Raik, Anton Chepurov, Raimund Ubar, "PSL Assertion Checking Using Temporally Extended High-Level Decision Diagrams", Journal of Electronic Testing: Theory and Applications (JETTA) [submitted on September 30, 2008]

- Jaan Raik, Maksim Jenihhin, Anton Chepurov, Uljana Reinsalu, Raimund Ubar, "APRICOT: a Framework for Teaching Digital Systems Verification", *Proc. of 19th EAEEIE Annual Conference, IEEE*, Tallinn, Estonia, June 29 July 2, 2008, pp. 1-6

- Jaan Raik, Uljana Reinsalu, Raimund Ubar, Maksim Jenihhin, Peeter Ellervee, "Code Coverage Analysis using High-Level Decision Diagrams", *Proc. of the 11th IEEE Workshop on Design and Diagnostics of Electronic Systems (DDECS'08)*, April, 2008, pp. 201-206

- Karina Minakova, Uljana Reinsalu, Anton Chepurov, Jaan Raik, Maksim Jenihhin, Raimund Ubar, Peeter Ellervee, "High-Level Decision Diagram

- Manipulations for Code Coverage Analysis", *Proc of the 11th IEEE Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, October 2008, pp. 207 210

- Jenihhin, Maksim, "PSL Assertions based Verification with HLDD Tools", *Proc. of the 2nd IKTDK Conference*, Viinistu, Estonia, May 11-12, 2007, pp. 17 20

- Maksim Jenihhin, "Assertion-based verification and testing with Decision Diagrams", *PhD Forum (abstract + poster)*, *Design, Automation and Test in Europe (DATE'08)*, Munich, Germany, March 10-14, 2008

### Assertion-based manufacturing test

- Maksim Jenihhin, Jaan Raik, Raimund Ubar, Anton Chepurov, "On reusability of verification assertions for testing", *Proc. of 11th IEEE Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, October 2008, pp. 151 154

- Knut Hermann, Jaan Raik, Maksim Jenihhin "TTBist: a DfT Tool for Enhancing Functional Test for SoC", *Proc. of the Baltic Electronics Conference*, Laulasmaa, Estonia, 2006, pp. 191-194

- Jaan Raik, Maksim Jenihhin, Rain Adelbert, "Sequential Circuits BIST Synthesis from Signal Specifications", *Proc. of IEEE Norchip Conference*, Oulu, Finland, November 21-22, 2005, pp.196 199

- Jenihhin, Maksim, "On reusability of verification assertions for testing", *Proc. of the 3rd IKTDK Conference*, Voore, Estonia, April 25-26, 2008, pp. 43-46

### High-level and hierarchical manufacturing test

- Jaan Raik, Raimund Ubar, Taavi Viilukas, Maksim Jenihhin, "Mixed Hierarchical-Functional Fault Models for Targeting Sequential Cores", *Journal of Systems Architecture*, 54(3-4), Elsevier, 2008, pp. 465 477

- Giuseppe Di Guglielmo, Franco Fummi, Maksim Jenihhin, Graziano Pravadelli, Jaan Raik, Raimund Ubar, "On the Combined Use of HLDDs and EFSMs for Functional ATPG", *Proc. of IEEE East-West Design and Test Symposium*, Yerevan, Armenia, September 7-10, 2007, pp. 503 508

- Raimund Ubar, Jaan Raik, Artur Jutman, Maksim Jenihhin, Marina Brik, Martin Instenberg, Heinz-Dieter Wuttke, "Diagnostic Modeling of Microprocessors with High-Level Decision Diagrams", *Proc. of 11th IEEE Biennial Baltic Electronics Conference (BEC'08)*, Tallinn, Estonia, October 2008, pp. 147 150

- Raimund Ubar, Jaan Raik, Artur Jutman, Maksim Jenihhin, Martin Instenberg, Heinz-Dieter Wuttke, "Modeling Microprocessor Faults on High-Level Decision Diagrams", *Proc. of 2nd Workshop on Dependable and Secure Nanocomputing (WDSN'08)*, Anchorage Hilton Hotel, AK, USA, June 2008, pp. 1 6

- Raimund Ubar, Sergei Devadze, Maksim Jenihhin, Jaan Raik, Gert Jervan, Peeter Ellervee, "Hierarchical Calculation of Malicious Faults for Evaluating the Fault-Tolerance", *Proc. of IEEE International Symposium on Electronic Design, Test and Applications (DELTA'08)*, Hong Kong, January 23 25, 2008, pp. 222-227

- Raimund Ubar, Gert Jervan, Jaan Raik, Maksim Jenihhin, Peeter Ellervee, "Dependability Evaluation in Fault-Tolerant Systems with High-Level Decision Diagrams", *Proc. of the Computer Science meets Automation: 52. IWK Internationales Wissenschaftliches Kolloquium*, Ilmenau, Germany, 10-13 September, 2007, pp. 147 152

### Manufacturing test targeting physical defects

- Maksim Jenihhin, Jaan Raik, Raimund Ubar, Witold Pleskacz, Michal Rakowski, "Layout to Logic Defect Analysis for Hierarchical Test Generation", *Proc. of 10th IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems(DDECS'07)*, Kraków, Poland, April 11-13, 2007, pp. 35-40

- Witold Pleskacz, Maksim Jenihhin, Jaan Raik, Michal Rakowski, Raimund Ubar, Wieslaw Kuzmicz, "Hierarchical Analysis of Short Defects between Metal Lines in CMOS IC", Proc. of the 11th Euromicro Conference on Digital System Design (DSD) Architectures, Methods and Tools, Parma, Italy, September 2008, pp 729 734

- Jenihhin, Maksim, "Case Study: Defect-Oriented Testing of a Combinational Circuit", *Proc. of the 1st IKTDK Conference*, Jäneda, Estonia, May 12-13, 2006, pp. 78 81

### Built-in self test optimization

- Gert Jervan, Petru Eles, Zebo Peng, Raimund Ubar, Maksim Jenihhin "Test Time Minimization for Hybrid BIST of Core-Based Systems", *Journal of Computer Science and Technology*, 21(6), 2006, pp. 907 912

- Raimund Ubar, Maksim Jenihhin, Gert Jervan, Zebo Peng "Hybrid BIST Optimization for Core-based Systems with Test Pattern Broadcasting", *Proc. of the IEEE International Workshop on Electronic Design, Test and Applications (DELTA 2004)*, Perth, Australia, January 28-30, 2004, pp. 3 8

- Raimund Ubar, Maksim Jenihhin, Gert Jervan, Zebo Peng "An Iterative Approach to Test Time Minimization for Parallel Hybrid BIST Architecture" *Proc. of 5th IEEE Latin-American Test Workshop (LATW'04)*, Cartagena, Colombia, March 8-10, 2004, pp. 98 103

- Gert Jervan, Petru Eles, Zebo Peng, Raimund Ubar, Maksim Jenihhin "Hybrid BIST time minimization for core-based systems with STUMPS architecture", *Proc. of the 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems (DFT 2003)*, Boston, MA, USA, November 3-5, 2003, pp. 225 232

- Gert Jervan, Petru Eles, Zebo Peng, Raimund Ubar, Maksim Jenihhin "Test Time Minimization for Hybrid BIST of Core-Based Systems", *Proc. of the 12th IEEE Asian Test Symposium (ATS03)*, Xian, China, November 17-19, 2003, pp. 318 323

- Raimund Ubar, Maksim Jenihhin, Gert Jervan, Zebo Peng "Test Time Minimization for Hybrid BIST with Test Pattern Broadcasting", *Proc. of the 21st NORCHIP Conference*, Riga, Latvia, November 10-11, 2003, pp. 112-116

- Maksim Jenihhin, "Test Time Minimization for Parallel Hybrid BIST Architectures", *Master thesis, Tallinn University of Technology*, Tallinn, June 2004

- Maksim Jenihhin, "Test Time Minimization for Hybrid BIST of Systems-on-Chip", *Bachelor thesis, Tallinn University of Technology,* Linköping, June 2003

## **List of Abbreviations**

ABV Assertion-Based Verification

AGM Alternative Graph Model

APRICOT Assertions, PRopertles, Coverage and Test

ASIC Application Specific Integrated Circuit

ATPG Automatic Test Pattern Generator

BDD Binary Decision Diagram

BIST Built-In Self-Test

CAD Computer Aided Design

CTL Computation Tree Logic

DD Decision Diagram

DfT Design for Testability

DfV Design for Verifiability

DUV Design Under Verification

EDIF Electronic Design Interchange Format

FL Foundation Language

FoCs Formal Checkers

FPGA Field Programmable Gate Array

GCD Greatest Common Devisor

GDL General Description Language

GUI Graphical User Interface

HDL Hardware Description Language

HIF HDL Intermediate Format

HLDD High-Level Decision Diagrams

IEEE Institute of Electrical and Electronics Engineers

LTL Linear Time temporal Logic

OBE Optional Branching Extension

PC Personal Computer

PPG Primitive Property Graph

PSL Property Specification Language

RTL Register Transfer Level

SERE Sequential Extended Regular Expressions

SSBDD Structurally Synthesized Binary Decision Diagrams

THLDD Temporally extended High-Level Decision Diagrams

TLM Transaction Level Modelling

TPG Test Pattern Generation

TUT Tallinn University of Technology

VHDL VHSIC (Very-High-Speed Integrated Circuit) Hardware

Description Language

WG Working Group

### Latin and English abbreviations:

*aka* - also known as

*e.g.* - for example

et al. - and other co-authors

etc. - and the resti.a. - among others

*i.e.* - that is

vs. - versus

# Chapter 1 **INTRODUCTION**

This thesis addresses several simulation-based hardware verification issues. The main emphasis is put on assertion checking and structural coverage measurement exploiting advantages of High-Level Decision Diagrams (HLDD) design representation model.

This introductory chapter first presents the motivation behind the presented work, followed by more detailed problem formulation. This is followed by a summary of the main contributions and an overview of the thesis structure.

#### 1.1 Motivation

Nowadays, it is not easy to realize that mobile phones, so ordinary today, have got a wide spread only ten years ago as well as consumer digital cameras just five years ago. Not to mention the times (slightly more than 15 years ago) when usual people lived without the Internet. The technology advances very rapidly and today we are surrounded by complex electronic devices and embedded systems that have become a common part of our lives. We rely on them and accept their correct behaviour as granted. At the same time we are becoming more and more dependent on them. Minor failures may annoy us while a major one may have a serious catastrophic effect and even cost human lives.

There are known famous cases of a fault occurrence in electronic devices. One of them is the flight tragedy of the European Space Agency's first Ariane 5 launcher on June4, 1996. Its first flight, known as Flight 501, has failed with the rocket self-destructing 37 seconds after launch. This case is sometimes called one of the most expensive "computer bugs" in history. The tragedy was caused purely by the system design error. Further, the official investigation report on this case [87] has concluded: "The extensive reviews and tests carried out during the Ariane 5 Development Programme did not include adequate analysis and testing ..., which could have detected the potential failure".

Another well known case is the "Pentium FDIV bug" in several Intel's original Pentium processors' families [88]. Because of this fault, some particular floating point division operations performed with these processors could produce incorrect results. This fault was also one of the most expensive "computer bugs" and cost Intel Corp. \$475 million.

The rapid development of the digital systems requires a huge increase of efforts to verify the functionality, i.e. ascertain that the implemented design meets the intended specification. It is obvious that, an exhaustive functional verification of an average digital hardware design requires exercising an extremely large amount of possible input combinations. For example (the example is from [5]), let us consider a digital hardware design that has 10 inputs and 100 flip-flops (i.e. a bit more than three 32-bit registers). This design would require in the worst case  $(2^{10})^{100}$ , i.e.  $2^{1000}$ , test vectors to try. If we simulate 1000 test vectors per second, it would take us:  $(2^{1000}/(60^2*24*365.25))/1000 = 339,540,588,380,062,907,492,466,172,668,391,072,376,037,725,208,993,588,689,808,600,264,389,893,757,743,339,953,988,382,771,724,040,525,133,303,203,524,078,771,892,395,266,335,942,544,299,458,056,845,215,567,848,460,205,301,551,163,124,606,262,994,092,425,972,759,467,835,103,001,336,717,048,865,167,147,297,613,428,902,897,465,679,093,821,978,784,398,755,534,655,038,141,450,059,156,501 years to execute. Therefore, methods to overcome the complexity, yet provide acceptable results, are vital.$

The cause of an electronic system's failure observable by its final user can hide behind a wide set of the system's aspects. They include correctness of its software part, physical implementation, analog hardware part, the system timing issues etc. In this thesis we address digital hardware design verification against incorrect implementation of its intended functionality. This is type of design verification is usually referred to as hardware design functional verification. Several other design verification types as well as classification of hardware design functional verification are discussed in more detail in the introduction to Chapter 3.

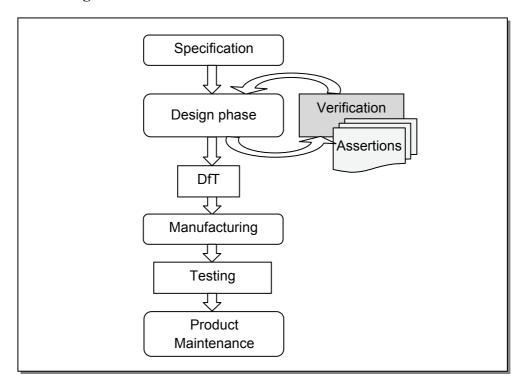

The growing complexity of the state-of-the-art hardware designs has made their verification a very important phase in the complete development process. As it was estimated in the last International Technology Roadmap for Semiconductors report [102], verification takes roughly 70% of design time, and therefore demands a huge amount of expensive resources such as man- or CPU-hours. This part of complete system development is often the most expensive phase. According to [102], the problem is caused by a pair of recent processes. They are, first, rapid design complexity increase and, second, the historically greater emphasis on other aspects of the design process that has produced significant progress in this area (e.g. automated tools for logic synthesis) leaving verification as the bottleneck.

Hardware verification is usually divided into two types. They are, first, formal, which assumes theorem proving and other formal methods of mathematics and, second, simulation-based, which relies on design simulation with the provided set of test vectors (aka stimuli). In this thesis we focus on the second type. Simulation-

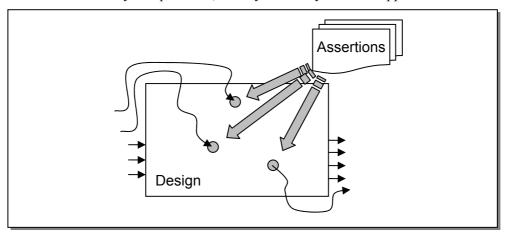

based hardware verification usually assumes comparison of one implementation against specification or another implementation (alternative or simplified, e.g. at a higher abstraction level). The other way is not to compare against a reference but to narrowly aim at specific design properties. The second approach is usually referred as Assertion-Based Verification (ABV). This thesis considers both of the possibilities but in different order.

ABV can be considered as one of the Design-for-Verifiability (DfV) techniques. They assume application of complementary parts of Hardware Description Language (HDL) code introduced especially for design verification assistance. In case of ABV this complementary code is assertions. ABV allows discovering design's misbehaviour (causing assertions violation) earlier and more effective.

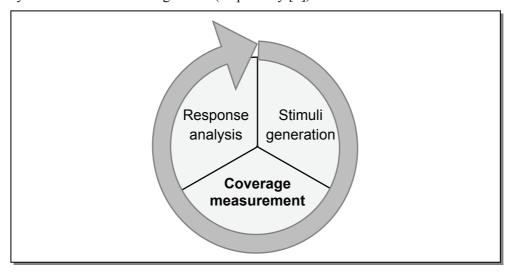

On the other hand comprehensive verification coverage metrics help to estimate the verification progress and more effectively manage verification efforts. Coverage measurement addresses an important question of "when the design is verified enough".

### 1.2 Problem formulation

Traditional design representation models are based on HDLs (e.g. VHDL or Verilog). However, there are known a number of drawbacks related to application of HDLs-based models in verification.

The awkwardness and usually even inability of HDLs to represent complex temporal assertions has caused introduction of languages especially dedicated for this purpose such as Property Specification Language (PSL). The latter one in turn is not always supported by design simulation tools or this support may be expensive. The attempts to unify design implementation and its properties' representations normally result in creation of large hardware checkers that assume significant restrictions on the initial assertion functionality. At the same time a comprehensive verification coverage measurement based on HDL model may require complicated HDL code manipulations resulting in inefficient resource consumption.

In this thesis we address the main simulation-based hardware verification issues that are speed and accuracy of the verification process. In particular we target aspects of assertion checking and coverage measurement by exploiting decision diagrams based model advantages. The proposed approaches use a homogeneous hardware verification flow based on high-level decision diagrams design representation model. Previous research works, including [44],[45], have shown that HLDDs are an efficient model for design simulation and convenient for diagnosis and debug.

### 1.3 Contributions

The main contributions of this thesis are summarised as follows:

### A new approach for HLDD-based assertions checking

- A temporal extension for the existing HLDD model. The new extended model is aimed at temporal properties expression and named Temporally extended High-Level Decision Diagrams (THLDD). The extension supports a set of commonly used temporal constructs that can be used to express a wide set of possible complex temporal relationships.

- A methodology for direct conversion of assertions expressed in Property Specification Language (PSL) to THLDD. The proposed hierarchical approach introduces an extendable library of Primitive Property Graphs (PPG Library). The components of this library serve as building blocks for a complex THLDD property construction.

- An approach for HLDD-based assertion checking. A modification of the existing HLDD-based simulator (HLDDsim) is proposed to support THLDDs and assertion checking. This part is supported by explanations of temporal issues and different varieties of THLDD properties.

A minor contribution includes discussions of verification assertions reuse for manufacturing testing.

#### A new approach for HLDD-based coverage analysis

- An approach for mapping traditional verification structural coverage metrics to HLDD-based coverage. In addition to the base code coverage metrics such as statement and branch coverage, the approach considers also more sophisticated ones, including FSM and data flow coverage metrics.

- An approach for *condition coverage* analysis. The approach employs a *hierarchical decision diagrams* model consisting of HLDDs and BDD-based representations of the conditional statements.

- An approach for *HLDD model manipulations* targeted to different aspects of verification coverage analysis.

### 1.4 Thesis organization

This thesis consists of 5 main chapters. The rest of it is organized as follows.

Chapter 2 provides background information required for discussion of the further proposed approaches. First, design representation by decision diagrams is presented. It includes a brief introduction to Binary Decision Diagrams (BDD) and

description of High-Level Decision Diagrams (HLDD) model. Further Property Specification Language (PSL) is discussed with respect to its application for the proposed approaches.

Chapter 3 starts with an overview of hardware functional verification, focusing on assertion-based verification. This section also includes the discussion of the related works and a brief presentation of Tallinn University of Technology verification framework APRICOT. Further, the approach for HLDD-based assertion checking is presented in the following sections. The sections are temporal extension to HLDD model, PSL to HLDD conversion method and the method for assertion checking with HLDDsim simulator for HLDD. The following section presents the experimental results proving the feasibility and efficiency of the proposed approach. A discussion of verification assertions reuse ideas is provided at the end of the chapter.

Chapter 4 starts with discussion of verification coverage metrics basic classification and the main aspects related to their measurement while keeping the main focus on structural coverage. It is followed by proposal of an approach for mapping traditional verification coverage metrics to HLDD coverage. Further, an approach employing a hierarchical decision diagrams' model for the condition coverage measurement is presented. Finally, HLDD model manipulations for the verification coverage analysis are discussed. The chapter is concluded with experimental results which demonstrate the feasibility and efficiency of HLDD-based coverage analysis approach.

Chapter 5 draws conclusions for this thesis and discusses possible directions for future work.

Two appendix sections are also included at the end of the thesis. The first one presents library of Primitive Properties' Graphs (PPG library) as one of the HLDD-based assertion checking approach contributions. The library is used for THLDD properties construction. The second appendix provides syntax for an internal file format AGM used for HLDD and THLDD models representation.

### 1.4.1 Formatting remarks

The text of the thesis has the following hierarchy of division:

- 1 Chapter

- 1.1 Section

- 1.1.1 Subsection

- 1.1.1.1 Clause

All co-authored references are emphasized in the work by a superscript suffix as follows: [ref.]<sup>co-auth.</sup>.

# Chapter 2 **BACKGROUND**

The approaches for hardware verification presented in this work take the advantage of design representation by High-Level Decision Diagrams (HLDDs) developed in Tallinn University of Technology. The purpose of this chapter is to introduce this model. Traditional Binary Decision Diagrams (BDDs) are also described in this chapter. BDD and HLDD themselves are not contributions of this thesis. However, most of the contributions rely on these models or are their extensions.

This chapter introduces also IEEE standard Property Specification Language (PSL) applied for expressing assertions. Within this work PSL is not just a choice among available properties' expression languages, but also serves in frames of this work as a reference for the supported set of assertions and their classification.

### 2.1 Design representation by decision diagrams

The history [9] of decision diagrams based design representation model development goes back to seventies when the basic concept of *Binary Decision Diagrams* (BDD) was introduced. It was done by two authors, Raimund J. Ubar and Sheldon B. Akers, independently from each other in 1976 [36] and 1978 [37] respectively. In [36] decision diagrams were originally referred to as *alternative graphs*. During the following years a number of works about using decision diagrams for test and simulation purposes were published, including [38] and [39]. However, it was not until the efficient Boolean manipulation method was presented by Randal E. Bryant in [40] when this type of representations became widely accepted by the research community.

Further, a number of special classes of binary decision diagrams have been proposed. They include popular Reduced Ordered BDDs (ROBDD) [40], multi-terminal BDDs [49], edge-valued BDDs [50], binary moment diagrams [51], multi-

valued decision diagrams [52], zero-suppressed BDDs [53], functional decision diagrams (FDD) [54], Kronecker FDDs [55] and others.

Structurally Synthesized BDDs (SSBDDs), formerly structural alternative graphs, are a class of BDD that have been proposed by Raimund Ubar in [36], [41]. This model is used for design representation at gate level and supported by a set of testing tools developed in Tallinn University of Technology and known as Turbo Tester ([58] and [90]).

There is a number of word-level Decision Diagrams based models used for design representation at Register-Transfer and higher levels. High-Level Decision Diagrams (HLDDs) were proposed by Raimund Ubar in [41] and further developed by Jaan Raik in [9] and [42], [19]<sup>co-auth</sup>. The other examples are multiterminal DDs (MTDDs) [49], K\*BMDs [56] and Assignment DDs (ADDs) [57] are some of them. However, in MTDDs the nonterminal nodes hold Boolean variables only. K\*BMDs, where additive and multiplicative weights label the edges are useful for compact canonical representation of functions on integers (especially wide integers). However, the main goal of HLDD representations is not canonicity but simulation and implications. The principal difference between HLDDs and ADDs lies in the fact that ADDs' edges are not labelled by activating values. They are rather used as connecting signals to represent structure. In HLDDs, the selection of a node activates a path through the diagram, which derives the needed value assignments for variables. Furthermore, ADD model includes four types of nodes (read, write, operator, assignment decision). In HLDD the nodes are divided into non-terminal (control) and terminal (data) ones. There is a comparison example of HLDD vs. ADD representation of the same design provided in Clause 2.1.2.5

The following two subsections provide a brief introduction to BDD and a more comprehensive one to HLDD models correspondingly.

### 2.1.1 Binary decision diagrams

BDD is a common representation for Boolean functions. A BDD is defined [9] as a directed acyclic graph with two terminal nodes, which are the *0-terminal* and *1-terminal* nodes. Each non-terminal node is labelled by an input variable of the Boolean function, and has two outgoing edges, called *0-edge* and *1-edge*.

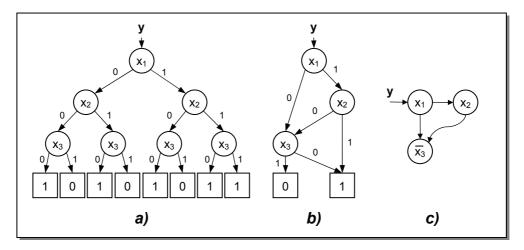

Ordered BDD (OBDD) is a BDD, where the input variables appear in a fixed order on all the paths of the graph and no variable appears more than once in a path. Figure 2.1 shows 3 different representations for a BDD corresponding to a Boolean function  $f = (x_1 \cdot x_2) \vee \neg x_3$ . Figure 2.1a shows a full tree BDD, Figure 2.1b shows an OBDD and Figure 2.1c shows the same OBDD from Figure 2.1b but in alternative description style.

Figure 2.1. Different BDD representations for a Boolean function  $y = (x_1 \cdot x_2) \lor \neg x_3$

Alternative description style differs from the traditional BDD description style by the following. Logic '1' and '0' constants holding terminals are omitted. Instead of them, a convention exists, that the right-hand edge of a node corresponds to 1-edge and the lower-hand edge to 0-edge. Exiting the BDD rightwards corresponds to the solution y = '1', while exiting downwards corresponds to y = '0'. In this type of description style the nodes can be labelled by both, variables and their inversions (see  $\neg x_3$  in Figure 2.1c).

Figure 2.2. BDD reduction rules

Reduced Ordered BDD (ROBDD) is created by applying the following reduction rules to OBDD [40]:

Reduction rule1: Eliminate all the redundant nodes where both edges point to the same node (Figure 2.2a).

Reduction rule2: Share all the equivalent sub-graphs (Figure 2.2b).

The important feature of ROBDDs is that they provide for canonical forms of Boolean functions. This allows us to check the equivalence of two Boolean functions by merely checking isomorphism of their ROBDDs. This is a widely used technique in formal verification.

The mentioned above *Structurally Synthesized BDDs* (SSBDDs) model is not directly used in frames of this thesis and therefore it is not discussed in detail. However, for the approaches where a hierarchical design representation is convenient, SSBDD model can complement HLDDs by representing the design's modules at the gate level. As it will be shown in the next subsection HLDDs are applied for design representation at RTL and higher abstraction levels.

### 2.1.2 High-level decision diagrams

The HLDD model description provided in this subsection is mostly based on the description provided in [9] and considers minor refinements made in ([19] and [13]) co-auth.

Figure 2.3. A high-level decision diagram representing a function  $y = f(x_1, x_2, x_3, x_4)$

### 2.1.2.1 HLDD model definition

A High-Level Decision Diagram (HLDD) is a graph representation of a discrete function. A discrete function y = f(x), where  $y = (y_1, ..., y_n)$  and  $x = (x_1, ..., x_m)$  are vectors is defined on  $X = X_1 \times ... \times X_m$  with values  $y \in Y = Y_1 \times ... \times Y_n$ , and both, the domain X and the range Y are finite sets of values. The values of variables may be Boolean, Boolean vectors, integers. Figure 2.3 presents an example of a graphical interpretation of a HLDD.

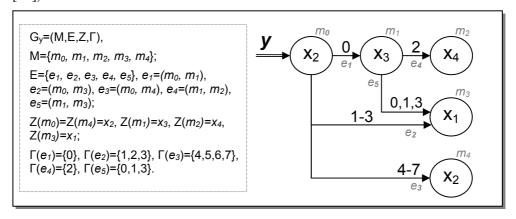

<u>Definition 1</u>: A high-level decision diagram is a directed non-cyclic labelled graph that can be defined as a quadruple  $G=(M,E,Z,\Gamma)$ , where M is a finite set of vertices (referred to as *nodes*), E is a finite set of *edges*, E is a function which defines the *variables labelling the nodes*, and E is a function on E.

The function  $Z(m_i)$  returns the variable  $x_k$ , which is labelling node  $m_i$ . Each node of a HLDD is labelled by a variable. In special cases, nodes can be labelled by constants or algebraic expressions. An edge  $e \in E$  of a HLDD is an ordered pair  $e = (m_{pc}, m_{sc}) \in E^2$ , where  $E^2$  is the set of all the possible ordered pairs in set E. Graphical interpretation of e is an edge leading from node  $m_{pc}$  to node  $m_{sc}$ . It is said that  $m_{pc}$  is a predecessor node of  $m_{sc}$ , and  $m_{sc}$  is a successor node of the node  $m_{pc}$ , respectively.  $\Gamma$  is a function on E representing the activating conditions of the edges for the simulating procedures. The value of  $\Gamma(e)$  is a subset of the domain  $X_k$  of the variable  $x_k$ , where  $e = (m_i, m_j)$  and  $Z(m_i) = x_k$ . It is required that  $Pm_i = \{ \Gamma(e) \mid e = (m_i, m_j) \in E \}$  is a partition of the set  $X_k$ .

Figure 2.3 presents a HLDD for a discrete function  $y=f(x_1,x_2,x_3,x_4)$ . HLDD has only one starting node (*root node*)  $m_0$ , for which there are no preceding nodes. The nodes that have no successor nodes are referred to as *terminal nodes*  $M^{term} \in M$  (nodes  $m_2$ ,  $m_3$  and  $m_4$  in Figure 2.3). Design representation by high-level decision diagrams, in general case, is a system of HLDDs rather than a single HLDD. During the simulation in HLDD systems, the values of some variables labelling the nodes of a HLDD are calculated by other HLDDs of the system.

In this thesis we propose to emphasize the connection between HLDD label (i.e. the graph name, bold y for the example in Figure 2.3) and the root node of the graph by a *double arrow* to distinguish it from the edges connecting the HLDD's nodes. In case of design representation by a system of HLDDs the notations of variables labelling the terminal nodes  $M^{term}$  are proposed to be *underlined* or remain *normal* for the explicit variables (i.e. input signals) and set off in *italics* for implicit variables (the ones referring to another HLDD graph in a system of HLDDs). An example of a system of HLDDs can be found in Figure 2.7.

### 2.1.2.2 Basic simulation on HLDDs

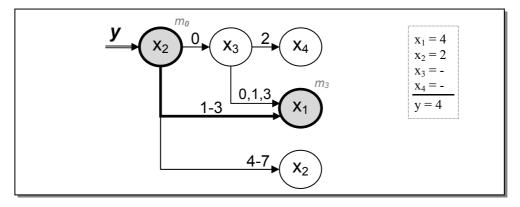

Simulation on decision diagrams takes place as follows. Consider a situation, where all the node variables are fixed to some value. For each non-terminal node  $m_i \notin M^{term}$  according to the value  $v_k$  of the variable  $x_k = Z(m_i)$  certain output edge  $e = (m_i, m_j)$ ,  $v_k \in \Gamma(e)$  will be chosen, which enters into its corresponding successor node  $m_j$ . Let us call such connections *activated edges* under the given values and denote them by  $m_i^{v_k}$ . Succeeding each other, activated edges form in turn *activated paths*. For each combination of values of all the node variables there exists always a corresponding activated path from the root node to some terminal node. We refer to this path as the *main activated path*. The simulated value of variable represented by the HLDD will be the value of the variable labelling the terminal node of the main activated path.

Figure 2.4. Design simulation on high-level decision diagrams

In Figure 2.4 simulation on the high-level decision diagram presented in Figure 2.3 is shown. Assuming that variable  $x_2$  is equal to 2, a path (marked by bold arrows) is activated from node  $m_0$  (the root node) to a terminal node  $m_3$  labelled by  $x_1$ . Let the value of variable  $x_1$  be 4, thus,  $y=x_1=4$ . Note, that this type of simulation is event-driven since we have to simulate only those nodes that are traversed by the main activated path (marked by grey colour in Figure 2.4).

When representing systems by decision diagram models, in general case, a network of HLDDs rather than a single DD is required. During the simulation in HLDD systems, the values of some variables labelling the nodes of a HLDD are calculated by other HLDDs of the system. The detailed algorithm for HLDD based systems simulation is provided in Subsection 3.4.1.

### 2.1.2.3 Pure RTL designs representation by HLDDs

Let us consider a design represented in a HDL at the *Register-Transfer Level* (RTL) of abstraction. We distinguish 2 styles of RTL description - *pure RTL* and *behavioural RTL*. While the first one more precisely targets the desired architecture, the second one describes the design in a more natural way. This and the following clauses introduce RTL design representations by HLDDs for these two description styles correspondingly.

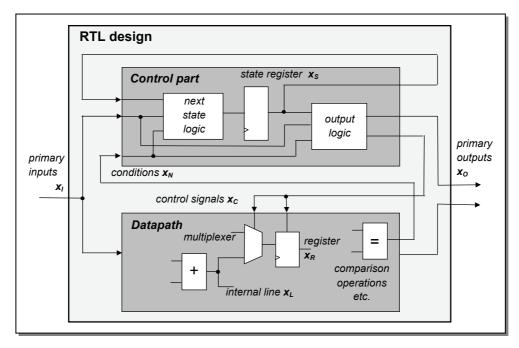

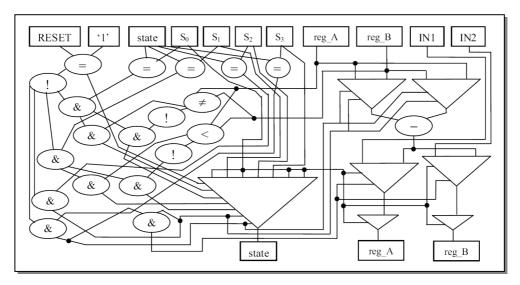

A deign described in the pure RTL style is assumed to be partitioned into a *datapath* and a *control part*. Figure 2.5 shows this type of architecture. Here, the control part is a Finite State Machine (FSM) with a state register (represented by variable  $x_S$  in the corresponding HLDD model), next state logic and output logic. As input signals to the FSM are the primary inputs of the design (variables  $x_I$ ), conditional signals originating from the datapath (variables  $x_N$ ) and current value of the state variable  $x_S$ . Outputs of the FSM are the primary outputs of the design (variables  $x_O$ ), control signals (variables  $x_C$ ) and the next value of  $x_S$ . The signals' variables notations introduced for Figure 2.5 are used throughout this clause.

Figure 2.5. RLT view of a digital design

The *datapath* can be viewed as a network consisting of modules or blocks. These include registers, multiplexers and functional units (for implementing operations).

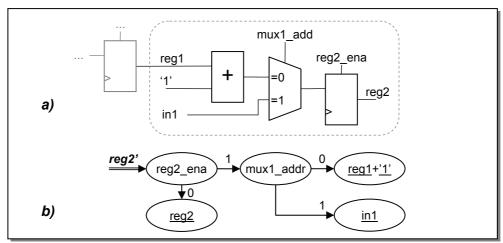

Figure 2.6. A datapath fragment (a) and its HLDD representation (b)

All the registers and some internal lines of the datapath can be represented by variables in the RTL HLDD model (variables  $x_R$  and  $x_L$ , respectively). Inputs for the datapath are the primary inputs  $x_I$  and control signals  $x_C$  (e.g. multiplexer

addresses and register enable signals). Outputs are the primary outputs  $x_O$  as well as conditional signals  $x_N$  (e.g. from comparison operators) leading to the control part FSM.

In HLDDs representing the datapath, the non-terminal nodes correspond to control signals (labelled by variables  $x_C$ ). The terminal nodes represent operations (functional units). Register transfers and constant assignments are treated as special cases of operations. Figure 2.6 shows a simple example of a HLDD representation (Figure 2.6b) for the given datapath fragment (Figure 2.6a). In this example and further in this clause we use a notation where the prime symbol "'" after diagram's variable denotes one clock cycle delay, i.e. next state of the variable (e.g reg3' vs. reg3).

Figure 2.7. Datapath representing HLDD partitioning types

Usually, a datapath is represented by a system of HLDDs. Here, different partitioning strategies are possible. The most commonly used partitioning is the one, where for each primary output, fanout signal and register a HLDD

corresponds. In addition, multiplexers that are connected to inputs of a functional unit are represented by a separate HLDD. Figure 2.7b shows this type of HLDD system partitioning for the datapath given in Figure 2.7a. However, it is possible to use alternative partitioning. For example, Figure 2.7c shows an approach, where for each register of the datapath exactly one decision diagram corresponds. This type of partitioning is sometimes referred as *register-oriented HLDD*. Other types of HLDD partitioning can be used depending on the target model application.

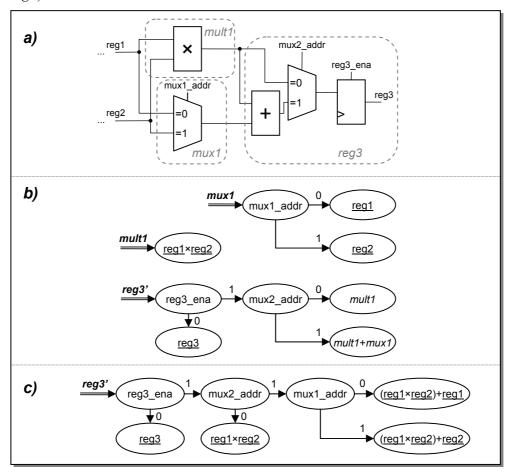

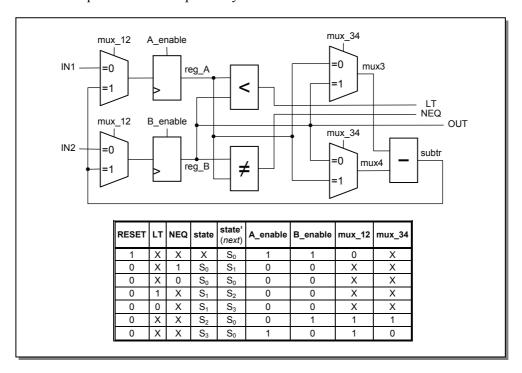

Figure 2.8. Converting FSM state table into HLDD

A simple RTL design *control part* is usually represented by a single HLDD, however in case of complex or multiple FSMs different partitioning are possible here as well.

The control part HLDD calculates the values for a vector consisting of the state variable and control signals. In the HLDD, the non-terminal nodes correspond to current state (labelled by variable  $x_S$ ) and conditional signals originating from the datapath (variables  $x_N$ ). Terminal nodes hold vectors with the values of next state and control signals  $x_C$ .

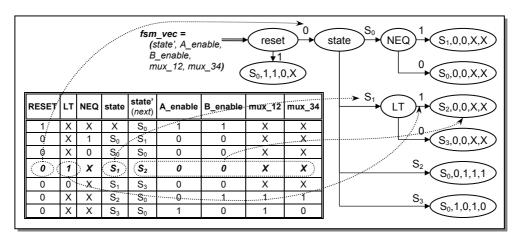

Figure 2.8 shows an FSM state table and its corresponding HLDD representation. In the HLDD, *state'* denotes the next state and *state* denotes the current state value. Variables  $A\_enable$ ,  $B\_enable$ ,  $mux\_12$  and  $mux\_34$  are FSM outputs and belong to the control signals  $x_C$ . Variables RESET, LT and NEQ are FSM inputs and belong to  $x_N$ . The dashed circles and arrows in Figure 2.10 depict setting up the edges and the terminal node corresponding to the fourth row of the state table.

#### 2.1.2.4 Behavioural RTL designs representation by HLDDs

Behavioural RTL HDL description style represents the design as an FSM structure nested with data assignments. It includes clocking information and is

therefore cycle-accurate. The control state is mapped to a *case* statement and conditions to *if* or *case* statements respectively. Each branch of the control state *case* statement corresponds to a certain control state and describes the datapath operations at the corresponding state and also the next state transitions.

This style is also synthesizable as well as pure RTL, but it is less target architecture specific. The behavioural RTL style is more commonly used in practical design HDL-based implementation than pure RTL style, where the design is strictly partitioned to datapath and control part. For example, ITC'99 benchmark circuits [76],[102] that are widely used in research community and partially represent real industrial designs, are described in behavioural RTL style.

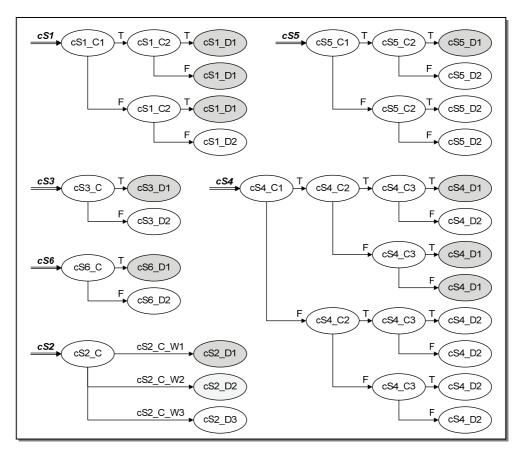

A separate HLDD diagram is generated for each internal signal and output port of the behavioural RTL description. For each such signal v we generate a diagram by parsing the behavioural RTL code as follows:

- 1. From the nested *if/case* structure generate a diagram where nodes correspond to conditions in respective *if/case* statements and edges correspond to decisions and are marked by the activation values of the respective decisions.

- 2. The terminal nodes are labelled by the right-hand side of assignments to a signal v. If there is no assignment to the signal v in the corresponding decision branch then the respective terminal node will be labelled by v.

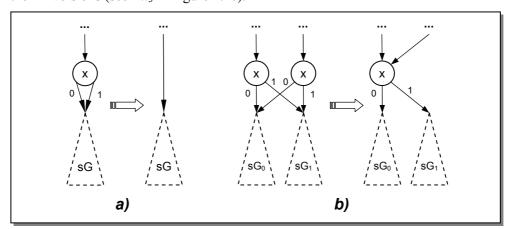

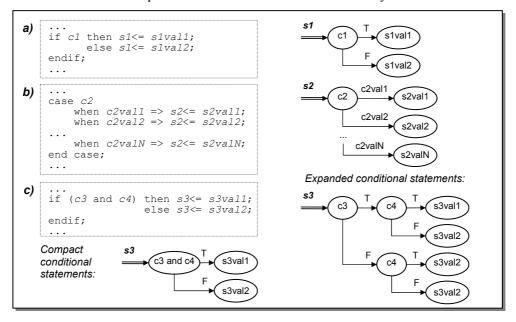

Figure 2.9. HLDD representation for the common constructs of the behavioural RTL VHDL

Figure 2.9 shows HLDD generation for the common behavioural RTL HDL (we consider VHDL) constructs. Figures 2.9a and 2.9b show simple *if* and *case*

conditional statements. Figure 2.9c shows a complex *if* construct, which consists of two conditions *c3* and *c4* joint by the logical *and* operator. For a complex conditional statement consisting of a set of conditions 2 HLDD variants are possible. Normally, the conditional statement evaluated as a whole and therefore can be represented by a HLDD with *compact conditional statements* (the bottom-left part of Figure 2.9c). However, in case if we are interested in several particular simulation coverage metrics (e.g. *condition coverage*) measurement, we may be interested in a HLDD representation with *expanded conditional statements* (the right-hand-side part of Figure 2.9c). This topic is discussed in detail in Chapter 4 (Section 4.3). Please note, that depending on the application we may be interested in a non-reduced HLDD. For example, *c4* is analyzed even after the *false-edge* of *c3* node in Figure 2.9c, however here the *reduction rule 1* from the Subsection 2.1.1 (Figure 2.2a) would be applicable.

Note, that since we do not support asynchronous latches in our approach the synthesizable RTL style must always include *else* and *default* branches of the *if* and *case* statements, respectively. Alternatively, default value assignments of signal v must be given.

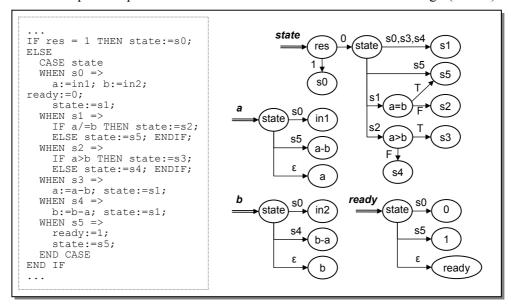

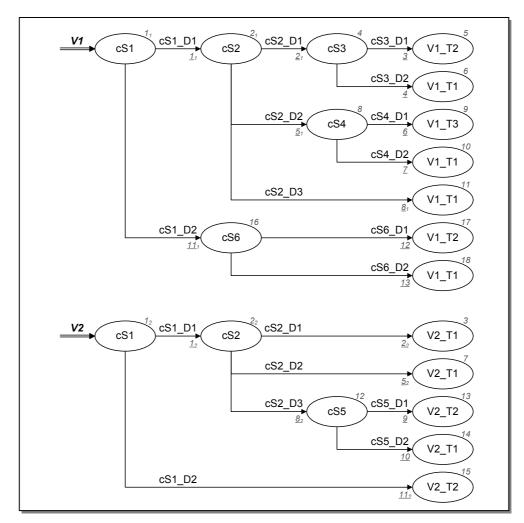

Figure 2.10 shows an implementation GCD1 of a greatest common devisor design, which is actually a benchmark *gcd* from the HLSynth'92 benchmarks family [103]) in behavioural RTL VHDL and its corresponding HLDD. The comparison benchmark from the next clause (Figure 2.11) is an alternative pure RTL description implementation of the Greatest Common Devisor design (GCD2).

Figure 2.10. Behavioural RTL VHDL and HLDD representations for a design GCD1

## 2.1.2.5 HLDD vs. ADD representations comparison

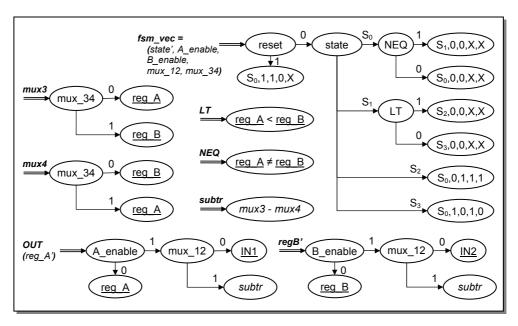

This clause provides an example (proposed in [43]) of HLDD model comparison with a commonly used *Assignment Decision Diagram* (ADD) approach.

Figure 2.11 presents the schematic RTL description of a Greatest Common Divisor benchmark GCD2. Figures 2.12 and 2.13 show its corresponding HLDD and ADD representations respectively.

Figure 2.11. A RTL design GCD2

Apart from the fact that HLDD description contains less nodes, there are the following fundamental differences:

- ADDs structure closely matches the RTL design. Edges of ADD correspond to

connecting nets in datapath. ADD for FSM is equivalent to its gate-level

implementation. In contrast, HLDDs do not strictly follow the circuit

structure. Here, a synthesis to extract data and control relationships from the

circuit functionality has been carried out.

- ADD model includes four types of nodes (read, write, operator, assignment decision). In HLDD the nodes are treated uniformly and can be divided into nonterminal nodes (control) and terminal nodes (data).

While ADDs do not support decision-making implicitly in the model, in HLDDs, the selection of a node activates a path through the diagram, which derives the needed value assignments for variables. Note, that the edges in ADD model have no labels. This is the most significant difference between the two models.

Figure 2.12. HLDD representation for the GCD2 design

Figure 2.13. ADD representation for the GCD2 design

## 2.1.2.6 HLDD model advantages for debug in verification

High-level decision diagrams model has a set of advantages compared to HDL and other DD based design representation models. A comparison with ADD has been provided in the previous clause. This clause describes by example some advantages of HLDD model for debug process in verification.

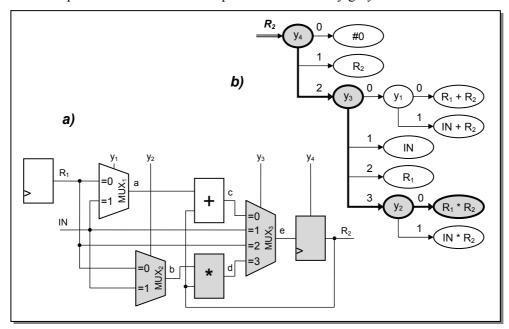

As an example, consider a datapath of a design depicted in Figure 2.14a and its corresponding HLDD representation shown in Figure 2.14b. Here,  $R_1$  and  $R_2$  are registers ( $R_2$  is also output),  $MUX_1$ ,  $MUX_2$  and  $MUX_3$  are multiplexers, + and \* denote adder and multiplier, IN is and input bus,  $y_1$ ,  $y_2$ ,  $y_3$  and  $y_4$  serve as input control variables, and a, b, c, d and e denote internal buses, respectively. In the HLDD, the control variables  $y_1$ ,  $y_2$ ,  $y_3$  and  $y_4$  are labelling internal decision nodes of the HLDD with their values shown at edges. The terminal nodes are labelled by a constant #0 (reset of  $R_2$ ), by word variables  $R_1$  and  $R_2$  (data transfers to  $R_2$ ), and by expressions related to data manipulation operations of the network. By bold lines and grey nodes, a full activated path in the HLDD is shown from  $Z(m_0) = y_4$  to  $Z(m^T \in M^T) = R_1 * R_2$ , which corresponds to the pattern  $y_4 = 2$ ,  $y_3 = 3$ , and  $y_2 = 0$ . The activated part of the network at this pattern is denoted by grey boxes.

Figure 2.14. HLDD model advantages for debug

The main advantage and motivation of using HLDD model, compared to other design representation models relying on netlists of primitive functions, is the increased efficiency of simulation and diagnostic modelling. The efficiency is caused by direct and compact representation of cause-effect relationships. For

example, instead of simulating the control word  $y_1$ ,  $y_2$ ,  $y_3$ ,  $y_4 = 0032$  by computing the functions  $a = R_1$ ,  $b = R_1$ ,  $c = a + R_2$ ,  $d = b * R_2$ , e = d, and  $R_2 = e$ , we only need to trace the nodes  $y_4$ ,  $y_3$  and  $y_2$  on the HLDD and compute a single operation  $R_2 = R_1 * R_2$ . In case of detecting an error in  $R_2$  the possible causes can be defined immediately along the simulated path through  $y_4$ ,  $y_3$  and  $y_2$  without any diagnostic analysis inside the corresponding RTL netlist. As a result of such a quick reasoning the debugging of a system can be considerably simplified. A detailed analysis inside the RTL netlist is needed only if all the values of  $y_4$ ,  $y_3$  and  $y_2$  are correct. In such a way, a very efficient hierarchical debugging procedure can be carried out with HLDDs: first, by a quick trace of faulty nodes in HLDDs, and then after locating the erroneous RTL region, by exactly locating the cause of error in this region.

The advantages for debug and proven [44],[45] faster design HLDD-based simulation are a strong motivation for HLDD application for simulation-based functional verification.

The first section of this background chapter has presented discussed the advantages of the design representation model called high level decision diagrams. This model is used for the approaches proposed in Chapters 3 and 4.

# 2.2 Property specification language

This section provides introductory information about a language for assertions expression *Property Specification Language* (PSL). Within this work PSL is not just a choice among available assertions expression languages like *System Verilog Assertions*, *Open Vera Assertions*, *e*, *Open Verification Library*, *SystemC Assertions*, etc. Based on the number of factors, discussed further, PSL serves in frames of this work as a reference for the supported set of properties and their classification.

Assertion-based verification popularity has encouraged a common property specification language development by the Functional Verification Technical Committee of Accellera. After a process in which donations from a number of companies were evaluated, the *Sugar* language [99] from IBM was chosen as the basis for PSL. The latest Language Reference Manual (LRM) for PSL version 1.1 was released in 2004 [91]. The language became an IEEE 1850 Standard in 2005 [92] and later IEC 62531 Standard [61] in 2007. The both above mentioned standards are based upon Accellera's LRM [91] with minor modifications (e.g. SystemC flavor introduction). This LRM together with the web resources listed on the PSL/Sugar Consortium webpage [94] can be considered for comprehensive PSL definition and explanation source. The information about PLS provided in this Chapter focuses on the parts of the language required for implementation and understanding of the approaches described in Chapter 3.

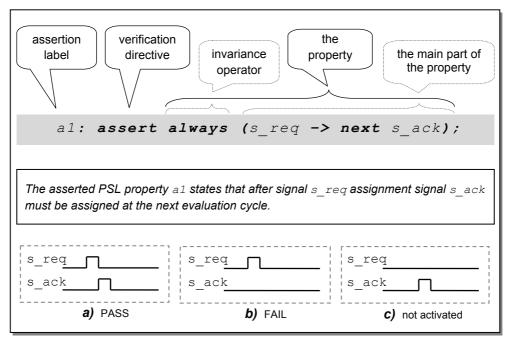

Figure 2.15. An example of PSL assertion with its structure explained and possible DUV's behavior timing diagrams

An example of a PSL assertion is shown in Figure 2.15. The assertion in the example consists of an optional label, the verification directive and the property to be checked. The last one is composed of the signals of interest and PSL operators. The timing diagrams in the bottom demonstrate 3 of many possible variants of the DUV's behaviour. In case of behaviour (a) the assertion is satisfied. However, the assertion will be violated in case of (b) and not activated (or vacuously passed) in case of behaviour (c).

#### 2.2.1 PSL organization

As it was mentioned, PSL is primarily based on IBM's Sugar language. The latter one was, in turn, originally based on *Computation Tree Logic* (CTL) (first introduced in 1977 [62]), initially just providing "sugaring" to the CTL's complicated syntax for IBM tools users' convenience in early '90-ies (as it is stated in [4] and [2]). The main application of Sugar was Formal Verification. Later, before PSL standardization, Sugar has employed *Linear-Time (temporal) Logic* (LTL) (first introduced in 1981 [63]) capabilities. At present, PSL consists of 2 parts:

- Foundation Language (FL), that is based on LTL and applied for both simulation-based and formal verification

- Optional Branching Extension (OBE), that is based on CTL and finds its application in formal verification

The main emphasis of this thesis is put on simulation-based verification, therefore from now on we will consider mostly FL part of PSL.

#### 2.2.1.1 Flavors

For convenience of the language users, PSL supports 5 flavors<sup>1</sup>, each of them corresponding to one HDL. The main difference between the flavors is seen for Boolean expressions. At present the flavors are:

- SystemVerilog (IEEE Std 1800)

- Verilog (IEEE Std 1364)

- VHDL (IEEE Std 1076)

- SystemC (IEEE Std 1666)

- GDL (General Description Language [98]), which is known also as a placeholder for the future HDL from IBM

```

VHDL flavor:

-- psl property p1 is

-- always (sig1 ->

-- ((sig2(0 to 4) = "1010")) or

-- (sig2(0 to 4) = "0101")))

-- @(clk'event and clk='1');

-- psl assert p1;

Verilog flavor:

// psl property p1 =

// always (sig1 ->

// ((sig2[0:4] == 4b'1010)) |

// (sig2[0:4] == 4b'0101)))

// @(posedge clk);

// psl assert p1;

```

Figure 2.16. The same PSL property expression in Verilog and VHDL flavors

An example of the same PSL property expression in Verilog and VHDL flavor is given in Figure 2.16. It is not allowed to mix flavors within one property (otherwise it could not be parsed).

## 2.2.1.2 Modes

In practice PSL properties related to a design under verification (DUV) may be expressed in one of the two modes [2].

- The *stand-alone mode* means that all properties related to a DUV are grouped into a separate file or files, and also usually organised within the files into *verification units*. This approach is preferred by verification engineers, because of the convenience for complex verification plan organization.

- The second mode is the *embedded mode*. In this mode, usually preferred by designers, the DUV's properties are written directly into its HDL files.

<sup>&</sup>lt;sup>1</sup> In the frames of PSL specification this term is normally used in the US transcription

Normally, special directives for HDL compilators with PSL support hidden into comments are used in this mode (e.g. like "-- psl" for VHDL flavor in Figure 2.16).

The embedded mode properties should be of the same PSL flavor as DUV's HDL. On the contrary, stand-alone properties can be of flavor *B* different from DUV's HDL *A*. However, it is necessary to check if the applied verification tool (e.g. simulator) with PSL support has the support for HDL *B* (e.g. SystemC).

The approaches proposed in the Chapter 3 of this work generally assume the VHDL flavor and the stand-alone mode for PSL properties expression.

## 2.2.1.3 Layers

PSL is a multi-layered language. The layers are:

- Boolean layer the lowest one, it consists of Boolean expressions in HDL (e.g. a and (b or c)). These expressions are used as building blocks in the upper layer to compose complex properties. Boolean expression is an expression that is evaluated in a single (clock) cycle and has the value true or false. Boolean expressions may contain non-Boolean expressions.

- Temporal layer it is the main part of the language. It builds temporal properties of Boolean expressions which describe DUV's (or its environment) behaviour over time (e.g. a and (next[3]b or next\_e[5 to 7]c)). The main tools here are temporal operators that are introduced further. This layer also adds the support for Sequential Extended Regular Expressions (SERE) (e.g. {a; {[\*3];b} or {[\*5 to 7]; c}}).

- Verification layer it provides directives that tell a verification tool what to do

with specified properties. For example the directive assert specifies that the

property is asserted (i.e. DUV's behaviour described by the property should

hold) and makes an assertion out of it. The other directives are: assume

(widely used to model DUV's environment), cover, restrict and others. It also

includes declaration of verification units vunit-s used for properties

organization, as it was mentioned in the previous subsection. Verification

units can inherit from other ones.

- Modelling layer additional helper code to model auxiliary combinational signals, state machines etc. that are not part of the DUV but are required to express the property. Usually (except SystemC and GDL flavor) the modelling layer instances are synthesizable.

The approaches provided in the Chapter 3 focus on the first two layers of PSL.

## 2.2.1.4 Styles

There are two styles in use for PSL properties expression.

- *LTL style* is the approach when a PSL property is composed of Boolean expressions as operands for PSL *Boolean* and *temporal operators*, as well as pure HDL operators.

- SERE<sup>2</sup> style makes use of sequences of Boolean variables or simple Boolean expressions. The sequences are enclosed curly braces and their atoms are usually separated by semi-colons (e.g. {a; (b && c);d} ). As opposed to Regular Expressions (REs) from pattern matching, SEREs are allowed to have not only variables but also expressions as atoms for their sequences. A SERE may be an operand for some PSL temporal operators, a part of another SERE and can contain special SERE repetition operators. For example, the following sequence {a;b[\*5];{c;d}[=3]} means that fist a is assigned, followed by 5 consecutive assignments of b and, finally, followed by sub-sequence c followed by a assignment for 3 non-consecutive times. Practically, in SERE style, a property is expressed as SEREs connected by suffix implication operators ("|->" and "|=>").

The most of the properties can be expressed in both LTL and SERE styles, however with different levels of convenience. Usually it is more reasonable to express a property or a part of a complex property in one of the styles and therefore styles are normally mixed. According to [4], while every LTL style property can be translated to SERE style, there are some SERE style properties (with a particular form of counting, like "p holds on every even cycle") that cannot be expressed by LTL (nor is it expressible by pure CTL).

The approaches from Chapter 3 include currently support for LTL style, however they do not have any principal constraint for SERE style usage. The support for SERE style PSL properties can be relatively easily added (as it will be explained further) and is scheduled for the future work. The most of the simple SERE style properties are known to have their formal equivalences in LTL style. Figure 2.19 from the next subsection presents a table with such equivalences [4].

## 2.2.2 PSL properties

It is important to distinguish between the two notions often used interchangeably: a property and an assertion. A *property* is some specified part of behaviour (of the DUV, its environment or the whole system). The property itself

<sup>&</sup>lt;sup>2</sup> An interesting fact is that in Sugar before PSL standardization, SERE was acronym for *Sugar* Extended Regular Expressions (as opposed to the present *Sequential* Extended Regular Expression) [99]

does not state if it is expected to fail or hold, whether the DUV should be checked for it during simulation or it should be avoided during some actions. A property with the verification directive (see 2.2.1.3) *assert* (added directly or separately in the corresponding *vunit*) makes an *assertion* of the property. Assertions are the most often usage of the properties in verification, however a property can serve as an *assumption*, a *restriction* or other depending of it application. Figure 2.15 shows clear separation of the property part in the assertion *a1*.

The properties are composed of combinations of operators with operands that are variables, internal signals or primary inputs/outputs of interest. A property can state single signal assignment without an explicit operator (e.g. p1: signal\_a; or a1: assert signal a; ).

## **2.2.2.1** *Operators*

This subsection discusses some commonly used PSL FL operators and their attributes. The complete list of PSL operators [92] sorted by their precedence is provided in Figure 2.17. The formal definitions for the operators are available in [92]. More details on PSL operators are also available in Appendix A of this work, which presents the *Primitive Properties Graphs* (PPG) library. *PPG library* is one of the contributions of this thesis and proposes decision diagrams based representation for a set of PSL operators.

| Operator |          |      |             | Operator class          | Associativity  |

|----------|----------|------|-------------|-------------------------|----------------|

| and or   |          | not  | etc.        | HDL operators           | same as in HDL |

| union    |          |      |             | Union operator          | left           |

| @        |          |      |             | Clocking operator       | left           |

| [*]      | [+]      | [=]  | [->]        | SERE repetition         | left           |

|          | within   |      |             | SERE sequence within    | left           |

|          | &        | 2.3  |             | SERE sequence AND       | left           |

|          | 1        |      |             | SERE sequence OR        | left           |

|          |          | :    |             | SERE sequence fusion    | left           |

|          |          | ;    |             | SERE seq. concatenation | left           |

| abort    | async_ab | ort  | sync_abort  | FL termination          | left           |

| next*    | next_eve | nt*  | eventually! | FL occurrence           | right          |

|          | until*   | befo | ore*        | FL bounding             | right          |

|          | ->       | =>   |             | SERE seq. implication   | right          |

|          | ->       | <->  |             | Boolean implication     | right          |

|          | always   | ne   | er/         | FL invariance operators | right          |

Figure 2.17. PSL FL operators (sorted by precedence from the highest on top)

In Figure 2.17 the asterisk at the end of a name (i.e. *name\**) denotes the whole *family of operators*, which is a group of operators that are related. Operators of one family usually share a common family name (prefix) that is followed by suffix (can be empty). For example, *next*, *next\_a*, *next\_e*, *next!*, *next\_a!*, *next\_e!* are operators from *next\** family.

Only particular operators can have their dedicated suffixes or particular a combination of them. Normally the suffixes have the following meaning:

- "\_a" the property should hold within <u>all</u> the time range of the operator (e.g. p1: next\_a[3 to 5] (signal\_1);)

- "\_e" there should exist a time moment when the property holds within the time range of the operator (e.g. p1: next e[3 to 5] (signal 1);)

- "\_" it means the *overlapping* version of the operator (e.g. p1: (x) until\_ (y); )

- "!" it means the *strong* version of the operator (e.g. p1: (x) until!\_ (y);)

Along with the set of operators, PSL has a number of built-it functions. Some of the functions are:

- prev() returns the previous value of the expression in the argument

- next() returns the value at the signal in the argument at the next smallest evaluation cycle

- rose() returns 'true' if the signal in the argument has changed to '1' from '0' in the previous evaluation cycle, otherwise 'false'

- fell() returns 'true' if the signal in the argument has changed to '0' from '1' in the previous evaluation cycle, otherwise 'false'

- stable() returns 'true' if the signal in the argument has not been changed since the previous evaluation cycle, otherwise 'false'

There are 7 more less frequently used PSL built-in functions. The formal definitions of the functions are available in [92].

It is important to notice that PSL clearly defines when each of the properties should be evaluated by adding @ clocking operator at the end of each property (e.g.  $@(clk'event\ and\ clk='l')$ ; like in Figure 2.16 for VHDL flavor). The other option if the same evaluation cycle is valid for all the properties to declare in vunit one default clock (e.g. default clock is  $clk'event\ and\ clk='l'$ ;). The examples given in this work and the approaches from Chapter 3 assume the latter case and the properties evaluation clock to be the same with DUV's one, if it is not stated otherwise.

## 2.2.2.2 Strong vs. weak operators

In the PSL the notion of strength is applicable to the properties as such and to PSL temporal operators. A property holds strongly if it holds on a finite path (simulation-based verification) and will hold on any extension of the path (e.g. p1: eventually! (not a and b); ).

As it is mentioned above the strong version of an operator is distinguished by "!" at the end of it. Temporal operators may come in both strong and weak forms or only in one of them. For example, <code>always</code> has only weak version, <code>eventually!</code> is available only in the strong one, while <code>until</code> can have the both.

The *strong* operators require that the terminating condition eventually occurs, while the *weak* ones do not. Let's consider two properties (busy until done;) and (busy until! done;). The first one will be satisfied even if done is never asserted and busy stayed asserted forever, while the second one requires done to finally occur.

## 2.2.2.3 Vacuous pass

The notion of vacuity is not PSL specific, however it is important for understanding the concept of assertion satisfaction and violation.

*Vacuous pass* occurs if a passing property contains Boolean expression that, in frames of the given simulation trace, has no effect on the property evaluation.

Let's consider a simple property (p1: always (req -> next ack);). p1 will pass on the simulation trace where signal req is never asserted without consideration when and if at all signal ack was asserted. It will be a vacuous pass because the property has passed not because of meeting all the specified behaviour but only because of non-fullfilment of logical implication activation conditions.

It is verification (simulation) tool dependant decision whether to treat vacuous passes as actual satisfactions of properties. The approaches presented in Chapter 3 separate vacuous passes from normal passes of a property.

## 2.2.2.4 PSL flexibility and common equivalences

Besides the convenience of 5 different flavors and different modes and styles, PSL gives the flexibility to express the same property in several possible ways. The most common equivalences for some simple properties expressed by means of different FL operators are provided in Figure 2.18. A set of commonly used equivalences between SERE and LTL style is provided in Figure 2.19. The other required equivalences can be written out as well or just used on-the-fly.

| Property            | An equivalent property                    |

|---------------------|-------------------------------------------|

| p <b>or</b> q       | not((not p) and (not q))                  |

| p <b>and</b> q      | <pre>not((not p) or (not q))</pre>        |

| p <b>-&gt;</b> q    | (not p) or q                              |

| always p            | <pre>not(eventually! (not p))</pre>       |

| always p            | never(not p)                              |

| eventually! p       | not(always (not p))                       |

| eventually! p       | "true" until! p                           |

| next p              | <pre>not(next! (not p))</pre>             |

| next! p             | <pre>not(next(not p))</pre>               |

| p <b>until</b> q    | (p until! q) or (always p)                |

| p <b>until</b> q    | not((not q) until! ((not p) and (not q))) |

| p until! q          | not((not q) until ((not p) and (not q)))  |

| p until_ q          | p until (p and q)                         |

| p until!_ q         | p until! (p and q)                        |

| p <b>before</b> q   | (not q) until (p and (not q))             |

| p <b>before!</b> q  | (not q) until! (p and (not q))            |

| p <b>before_</b> q  | (not q) until p                           |

| p <b>before!_</b> q | <pre>(not q) until! p</pre>               |

| next_event(b)(q)    | (not b) until (b and q)                   |

| next_event!(b)(q)   | (not b) until! (b and q)                  |

Figure 2.18. Some common equivalences between PSL FL operators

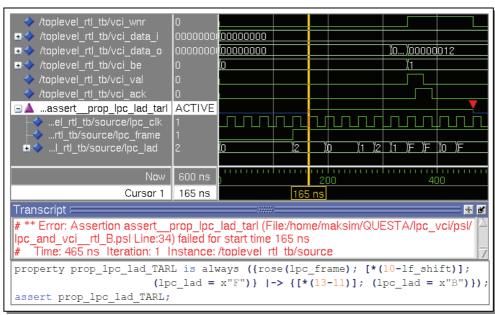

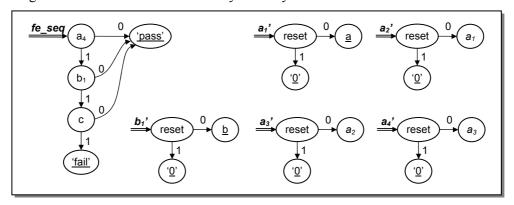

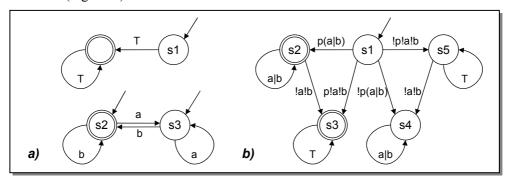

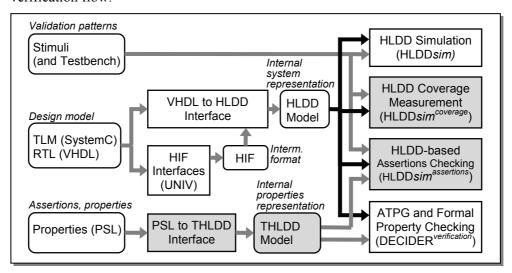

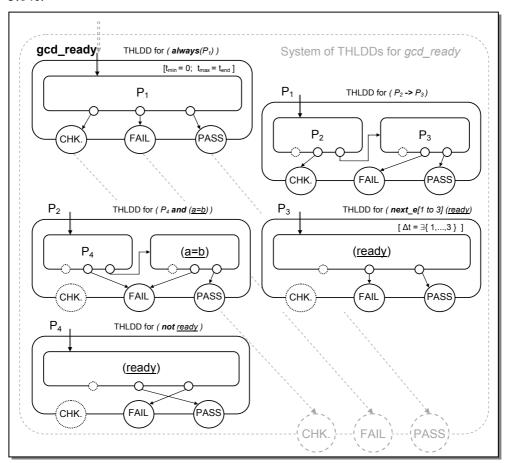

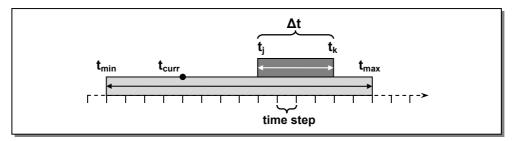

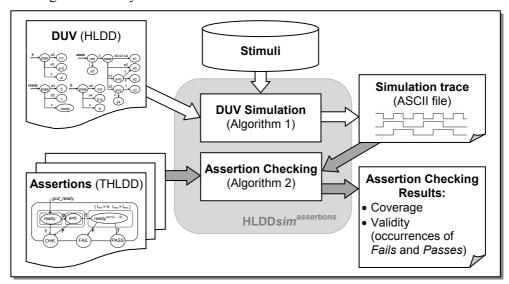

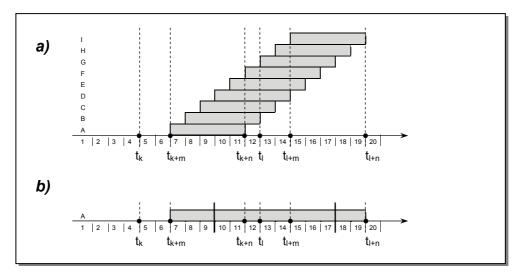

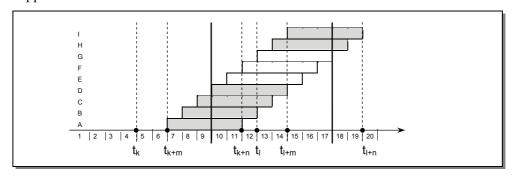

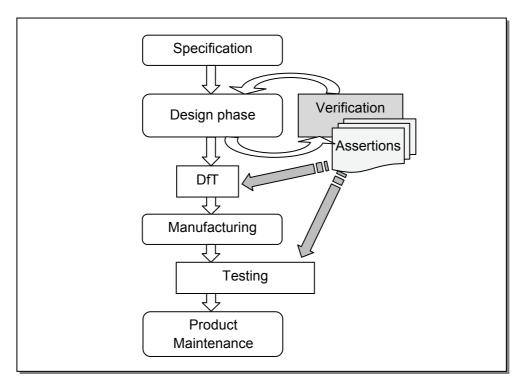

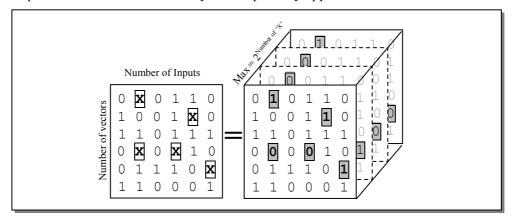

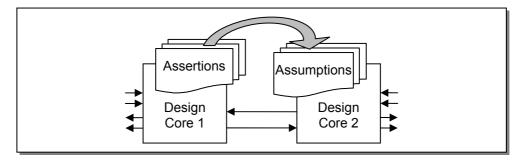

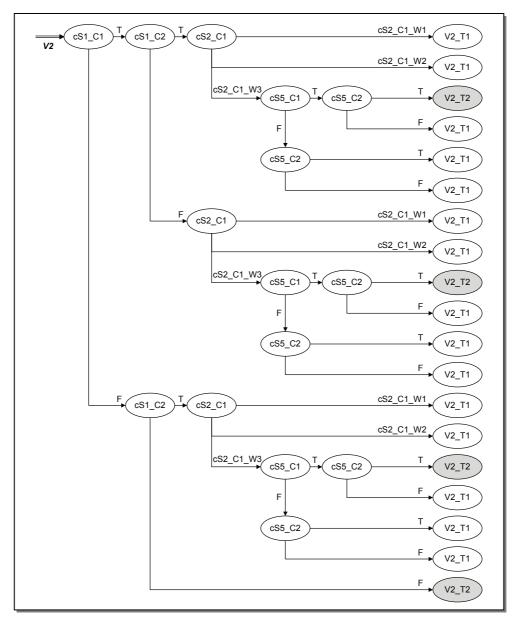

This flexibility allows avoiding particular parts of the language (e.g. undesired operators or their special order, or even the whole style). The reason for this may be requirement to follow some specific rules dictated by software tools or method. In some cases, however, satisfaction of the rules forbids usage of some expressible by PSL properties in any form.