# **DOCTORAL THESIS**

# Methods to Optimize Functional Safety Assessment for Automotive Integrated Circuits

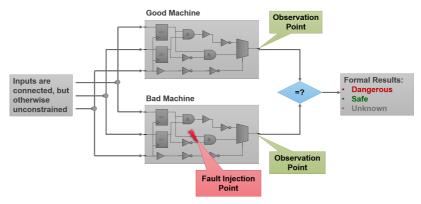

Ahmet Çağrı Bağbaba

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2022 TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 9/2022

# Methods to Optimize Functional Safety Assessment for Automotive Integrated Circuits

AHMET ÇAĞRI BAĞBABA

TALLINN UNIVERSITY OF TECHNOLOGY School of Information Technologies Department of Computer Systems

# The dissertation was accepted for the defence of the degree of Doctor of Philosophy in Computer and Systems Engineering on 4 March 2022

| Supervisor:    | Prof. Maksim Jenihhin<br>Department of Computer Systems<br>Tallinn University of Technology<br>Tallinn, Estonia |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| Co-supervisor: | Dr. Christian Sauer<br>Cadence Design Systems<br>Munich, Germany                                                |

| Opponents:     | Prof. Alberto Bosio<br>École Centrale de Lyon<br>Lyon, France                                                   |

|                | Dr. Juergen Alt<br>Infineon Technologies AG<br>Munich, Germany                                                  |

Defence of the thesis: 20 April 2022, Tallinn

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for any academic degree elsewhere.

Ahmet Çağrı Bağbaba

signature

Copyright: Ahmet Çağrı Bağbaba, 2022 ISSN 2585-6898 (publication) ISBN 978-9949-83-802-8 (publication) ISSN 2585-6901 (PDF) ISBN 978-9949-83-803-5 (PDF) Printed by Koopia Niini & Rauam TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 9/2022

# Meetodid autotööstuse kiipide funktsionaalse ohutuse hindamise optimeerimiseks

AHMET ÇAĞRI BAĞBABA

# Contents

| Lis | t of Pı                                        | ublications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                                          |

|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Au  | thor's                                         | s Contributions to the Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                                                                          |

| Ab  | brevia                                         | ations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                         |

| 1   | Intro<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5       | oduction<br>Motivation<br>Problem Formulation<br>Research Objectives<br>Contributions .<br>Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                             | 11<br>11<br>12<br>13<br>13<br>14                                                                           |

| 2   | Back<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5        | aground on Functional Safety and ISO 26262Functional Safety: A General Overview2.1.1Application Areas and Related StandardsAutomotive Functional Safety: ISO 26262Failure Types2.3.1Fault ModelsSafety MechanismsFunctional Safety Analysis2.5.1Quantitative Assessment of Hardware Architectures2.5.1.1Failure Modes Classification                                                                                                                                                                       | 16<br>16<br>16<br>18<br>20<br>20<br>21<br>22<br>23                                                         |

|     | 2.6                                            | <ul> <li>2.5.1.2 Hardware Architectural Metrics</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23<br>25<br>25<br>25<br>25<br>25<br>26                                                                     |

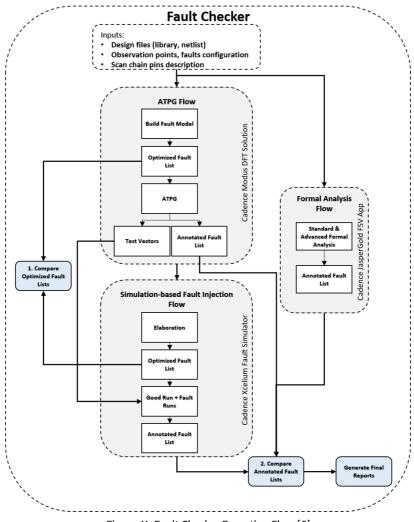

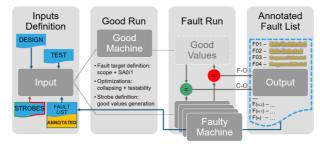

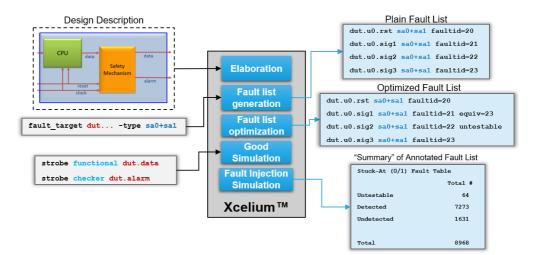

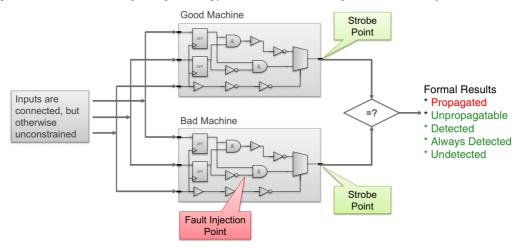

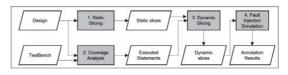

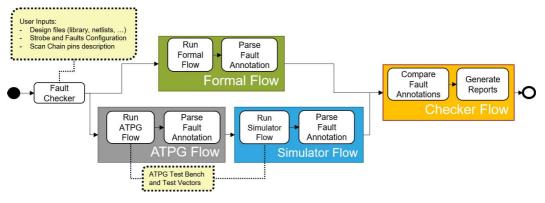

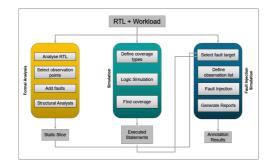

| 3   | Func<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | <ul> <li>ctional Safety Verification and Validation Using Fault Analysis Technologies</li> <li>Introduction</li> <li>Related Works</li> <li>Functional Safety Analysis Technologies</li> <li>3.3.1 Simulation-based Fault Injection</li> <li>3.3.2 Formal Analysis</li> <li>3.3.3 Automatic Test Pattern Generator</li> <li>The Proposed Methodology</li> <li>Experimental Setup and Results</li> <li>3.5.1 Experimental Setup</li> <li>3.5.2 Experimental Results</li> <li>Chapter Conclusions</li> </ul> | 31<br>33                                                                                                   |

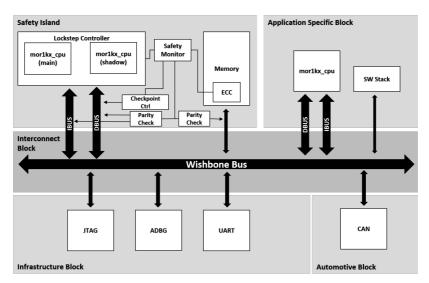

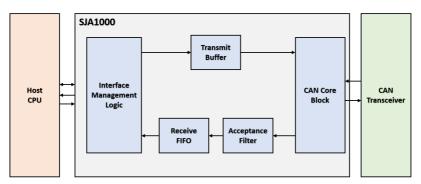

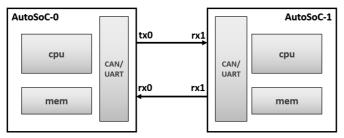

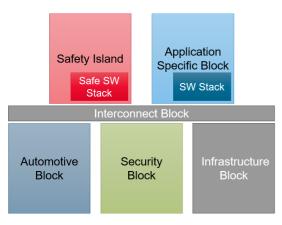

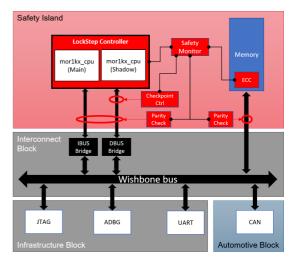

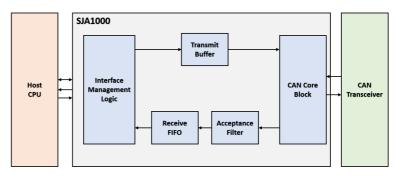

| 4   |                                                | AutoSoC Benchmark Suite<br>Introduction<br>Related Works<br>General Architecture of the AutoSoC<br>4.3.1 Hardware Components<br>4.3.1.1 Controller Area Network                                                                                                                                                                                                                                                                                                                                            | <ul> <li>30</li> <li>40</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>42</li> </ul> |

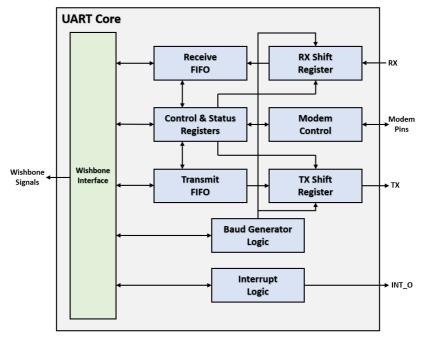

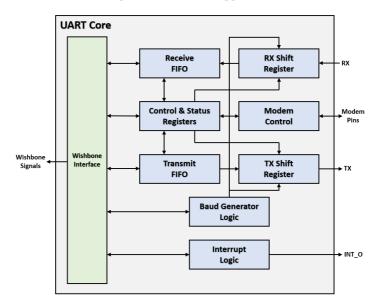

|      |                                                                                    | 4.3.1.2 Universal Asynchronous Receiver-Transmitter                                                                                                                                                               | 44                                         |

|------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|      | 4.3.2                                                                              | Safety Components                                                                                                                                                                                                 | 45                                         |

|      | 4.3.3                                                                              | Software Resources                                                                                                                                                                                                | 46                                         |

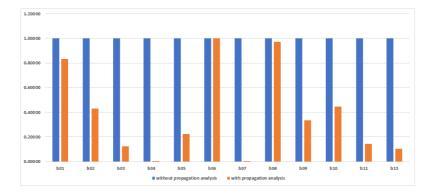

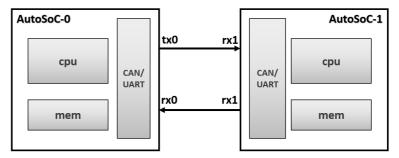

| 4.4  | Experi                                                                             | mental Results                                                                                                                                                                                                    | 46                                         |

| 4.5  | Chapte                                                                             | er Conclusions                                                                                                                                                                                                    | 47                                         |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

| Acce | lerating                                                                           | g Simulation-based Fault Injection Campaigns with Fault List Pruning                                                                                                                                              | 48                                         |

| 5.1  | Introdu                                                                            | uction                                                                                                                                                                                                            | 48                                         |

| 5.2  | Relate                                                                             | d Works                                                                                                                                                                                                           | 49                                         |

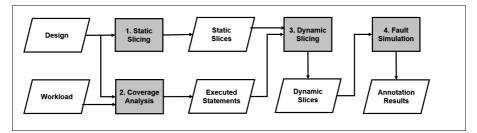

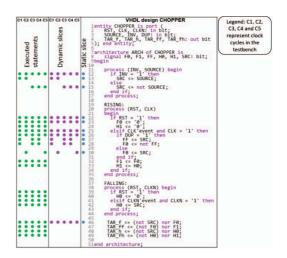

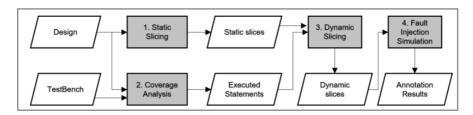

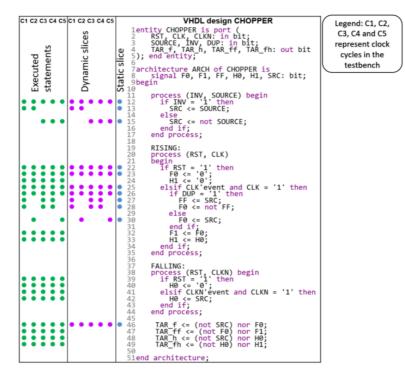

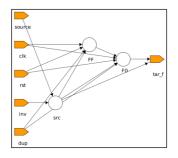

| 5.3  | Dynam                                                                              | nic Slicing based Fault List Pruning                                                                                                                                                                              | 51                                         |

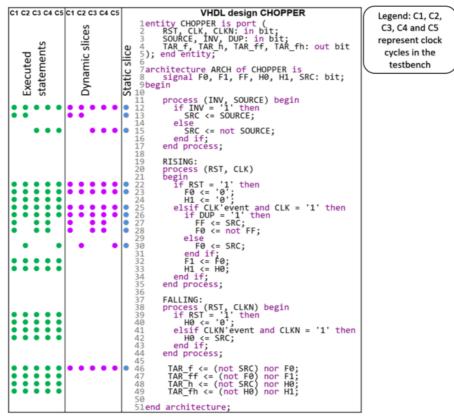

|      | 5.3.1                                                                              | Static Slicing                                                                                                                                                                                                    | 52                                         |

|      | 5.3.2                                                                              | Coverage Analysis                                                                                                                                                                                                 | 52                                         |

|      | 5.3.3                                                                              |                                                                                                                                                                                                                   | 53                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 54                                         |

|      | 5.3.4                                                                              |                                                                                                                                                                                                                   | 54                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 55                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 55                                         |

|      | 5.0.0                                                                              | •                                                                                                                                                                                                                 | 56                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 56                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 57                                         |

|      | 537                                                                                |                                                                                                                                                                                                                   | 58                                         |

| 51   | 0.017                                                                              |                                                                                                                                                                                                                   | 58                                         |

| J.4  |                                                                                    |                                                                                                                                                                                                                   | 59                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 59                                         |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

|      | 5.4.4                                                                              |                                                                                                                                                                                                                   | 60                                         |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

|      |                                                                                    |                                                                                                                                                                                                                   | 61                                         |

|      |                                                                                    | •                                                                                                                                                                                                                 |                                            |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

|      |                                                                                    |                                                                                                                                                                                                                   | 65                                         |

| 5.5  | Chapte                                                                             | er Conclusions                                                                                                                                                                                                    | 66                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | <i>.</i> –                                 |

|      | -                                                                                  | - · ·                                                                                                                                                                                                             | 67                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 67                                         |

| •    |                                                                                    |                                                                                                                                                                                                                   | 69                                         |

| 6.3  | -                                                                                  |                                                                                                                                                                                                                   | 70                                         |

|      | 6.3.1                                                                              |                                                                                                                                                                                                                   | 70                                         |

|      | 6.3.2                                                                              |                                                                                                                                                                                                                   | 71                                         |

|      | 6.3.3                                                                              |                                                                                                                                                                                                                   | 71                                         |

|      |                                                                                    | 6.3.3.1 Structural Analysis Check Types                                                                                                                                                                           | 72                                         |

|      |                                                                                    | 6.3.3.2 Formal Analysis Check Types                                                                                                                                                                               | 72                                         |

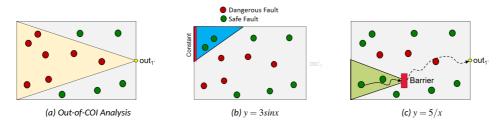

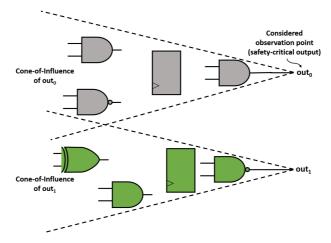

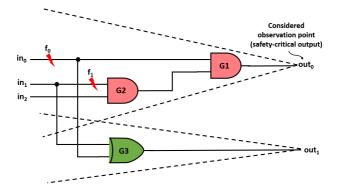

| 6.4  | Propos                                                                             | sed Application-Dependent Safe Fault Identification Method                                                                                                                                                        | 74                                         |

|      | 6.4.1                                                                              | Application-dependent Safe Faults                                                                                                                                                                                 | 74                                         |

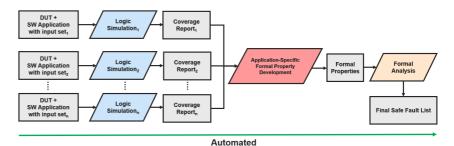

|      | 6.4.2                                                                              | The Proposed Flow                                                                                                                                                                                                 | 74                                         |

|      |                                                                                    | •                                                                                                                                                                                                                 | 75                                         |

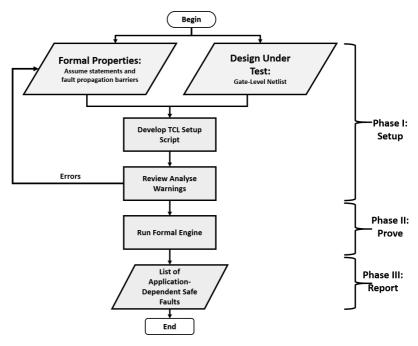

|      |                                                                                    |                                                                                                                                                                                                                   | 76                                         |

|      |                                                                                    |                                                                                                                                                                                                                   | 77                                         |

| 6.5  | Experi                                                                             |                                                                                                                                                                                                                   | 78                                         |

|      |                                                                                    |                                                                                                                                                                                                                   |                                            |

|      | 4.5<br>Acce<br>5.1<br>5.2<br>5.3<br>5.4<br>5.4<br>5.5<br>Enha<br>6.1<br>6.2<br>6.3 | 4.3.34.4Experi4.5ChapteAccelerating5.1Introd5.2Relate5.3Dynan5.3.1 $5.3.2$ 5.3.3 $5.3.4$ 5.3.5 $5.3.6$ 5.45.4.15.4.2 $5.4.3$ 5.4.4 $5.4.5$ 5.5ChapteEnhancing H6.1Introd6.2Relate6.3Backgu6.4Proposition6.5Experi | <ul> <li>4.3.2 Safety Components</li></ul> |

|     |         | 6.5.2<br>6.5.3 | Safe Faults in UART<br>Safe Faults in CAN                         | 81<br>82 |

|-----|---------|----------------|-------------------------------------------------------------------|----------|

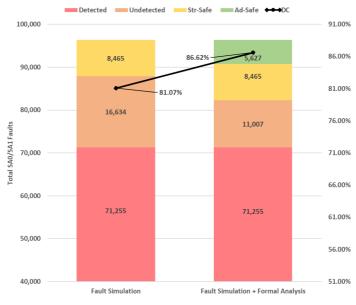

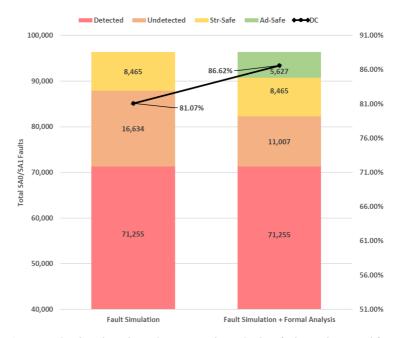

|     |         | 6.5.4          | Combined Results: Simulation-based Fault Injection + Formal Anal- | 00       |

|     | 6.6     | Chapte         | ysis<br>r Conclusions                                             | 83<br>85 |

| 7   | Cond    | lusions        |                                                                   | 87       |

| Lis | t of Fi | gures          |                                                                   | 89       |

| Lis | t of Ta | bles           |                                                                   | 90       |

| Re  | ferend  | ces            |                                                                   | 91       |

| Ac  | knowl   | edgeme         | ents                                                              | 101      |

| Ab  | stract  | •••••          |                                                                   | 103      |

| Ко  | kkuvõ   | te             |                                                                   | 105      |

| Ap  | pendi   | x 1            |                                                                   | 107      |

| Ap  | pendi   | x 2            |                                                                   | 115      |

| Ap  | pendi   | x 3            |                                                                   | 123      |

| Ap  | pendi   | x 4            |                                                                   | 127      |

| Ap  | pendi   | x 5            |                                                                   | 131      |

| Ap  | pendi   | x 6            |                                                                   | 139      |

| Ap  | pendi   | x 7            |                                                                   | 149      |

| Ap  | pendi   | x 8            |                                                                   | 161      |

| Ap  | pendi   | x 9            |                                                                   | 169      |

| Ap  | pendi   | x 10           |                                                                   | 177      |

| Cu  | rriculı | um Vitae       | e                                                                 | 205      |

| Elu | ılookiı | rjeldus.       |                                                                   | 207      |

# **List of Publications**

The present Ph.D. thesis is based on the following publications that are referred to in the text by Roman numbers.

- I A. C. Bagbaba, F. Augusto da Silva, and C. Sauer. Improving the confidence level in functional safety simulation tools for iso 26262. In 2018 Design and Verification Conference (DVCON), 2018

- II F. Augusto da Silva, A. C. Bagbaba, S. Hamdioui, and C. Sauer. Use of formal methods for verification and optimization of fault lists in the scope of iso26262. In 2018 Design and Verification Conference (DVCON), 2018

- III Felipe Augusto da Silva, Ahmet Cagri Bagbaba, Said Hamdioui, and Christian Sauer. Efficient methodology for iso26262 functional safety verification. In 2019 IEEE 25th International Symposium on On-Line Testing and Robust System Design (IOLTS), pages 255–256, 2019

- IV Ahmet Cagri Bagbaba, Maksim Jenihhin, Jaan Raik, and Christian Sauer. Efficient fault injection based on dynamic hdl slicing technique. In 2019 IEEE 25th International Symposium on On-Line Testing and Robust System Design (IOLTS), pages 52–53, 2019

- V Felipe Augusto da Silva, Ahmet Cagri Bagbaba, Said Hamdioui, and Christian Sauer. Combining fault analysis technologies for iso26262 functional safety verification. In 2019 IEEE 28th Asian Test Symposium (ATS), pages 129–1295, 2019

- VI Ahmet Cagri Bagbaba, Maksim Jenihhin, Jaan Raik, and Christian Sauer. Accelerating transient fault injection campaigns by using dynamic hdl slicing. In 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), pages 1–7, 2019

- VII Felipe Augusto da Silva, Ahmet Cagri Bagbaba, Annachiara Ruospo, Riccardo Mariani, Ghani Kanawati, Ernesto Sanchez, Matteo Sonza Reorda, Maksim Jenihhin, Said Hamdioui, and Christian Sauer. Special session: Autosoc - a suite of open-source automotive soc benchmarks. In 2020 IEEE 38th VLSI Test Symposium (VTS), pages 1–9, 2020

- VIII Felipe Augusto da Silva, Ahmet Cagri Bagbaba, Sandro Sartoni, Riccardo Cantoro, Matteo Sonza Reorda, Said Hamdioui, and Christian Sauer. Determined-safe faults identification: A step towards iso26262 hardware compliant designs. In 2020 IEEE European Test Symposium (ETS), pages 1–6, 2020

- IX Ahmet Cagri Bagbaba, Maksim Jenihhin, Raimund Ubar, and Christian Sauer. Representing gate-level set faults by multiple seu faults at rtl. In 2020 IEEE 26th International Symposium on On-Line Testing and Robust System Design (IOLTS), pages 1–6, 2020

- X Ahmet Cagri Bagbaba, Felipe Augusto da Silva, Matteo Sonza Reorda, Said Hamdioui, Maksim Jenihhin, and Christian Sauer. Automated identification of application-dependent safe faults in automotive systems-on-a-chips. *Electronics*, 11(3), 2022

# Author's Contributions to the Publications

- I In I, the author wrote the scripts for simulation-based fault injection and ATPG flows. The author also developed the idea and the application that uses ATPG test benches and test vectors in fault injection campaigns. Additionally, the author carried out all the simulations and collected the results.

- II In II, the author contributed during the development of the presented idea. The author assisted to writing.

- III In III, the author supported the combination of ATPG and fault injection flows with the scripts he developed. The author also synthesized and tested the designs that were used to carry out experiments.

- IV In IV, the author carried out the research on dynamic slicing. The author wrote all the scripts, implemented the idea using the required tools, prepared the target designs, conducted experiments, wrote the manuscript, and presented it at the conference.

- V In V, which is the extension of III, the author advanced the use of ATPG and fault injection to obtain better safety results. Similar to the previous one, the author also synthesized and tested the designs. The author also helped to elaborate the manuscript.

- VI In VI, the author extended and improved the method presented in the previous paper on dynamic slicing. The author also integrated the new algorithm into the tools, handled the experiments, wrote the manuscript, and presented it at the conference.

- VII In VII, the author was involved in developing the idea, designed the gate-level representation of the presented benchmark suite, ran simulations and fault injection campaigns using special test programs.

- VIII In VIII, the author contributed to the gate-level implementation of the target design, ran the tests, and carried out fault injection campaigns.

- IX In IX, the author developed the concept that maps faults from gate-level to RTL abstraction level. The author wrote all the scripts, ran the simulations, collected the experimental results, wrote the paper, and presented in the conference.

- X In X, the author established the idea of application-specific safe faults on an automotive system-on-chip. The author developed the automotive representative software application, wrote the scripts to characterize it, automatically generate formal properties, and ran a formal analysis to increase the safety level of the target design. The author also wrote the manuscript.

# Abbreviations

| ACC   | Adaptive Cruise Controller                              |

|-------|---------------------------------------------------------|

| ADAS  | Advanced Driver Assistance System                       |

| ALU   | Arithmetic Logic Unit                                   |

| ASIC  | Application Specific Integrated Circuit                 |

| ASIL  | Automotive Safety Integrity Level                       |

| ATPG  | Automatic Test Pattern Generation                       |

| BIST  | Built-in-Self-Test                                      |

| CAN   | Controller Area Network                                 |

| CCA   | Cruise-Control-Application                              |

| CRC   | Cyclic Redundancy Check                                 |

| CPU   | Central Processing Unit                                 |

| DC    | Diagnostic Coverage                                     |

| DCLS  | Dual-Core Lockstep                                      |

| DELS  | Dependent-Failure Analysis                              |

| DMR   | Dual Modular Redundancy                                 |

| DfT   | Design-for-Test                                         |

| EBS   | Emergency Braking System                                |

| FCC   | Error Correction Code                                   |

| ECU   | Electronic Control Unit                                 |

| EDA   | Electronic Design Automation                            |

| FIFO  | First-in-First-out                                      |

| FPGA  | Field-Programmable Gate Array                           |

| FTA   | Fault-tree Analysis                                     |

| FMEDA | Failure Modes, Effects, and Diagnostics Analysis        |

| GPDK  | Generic Process Design Kit                              |

| GPU   | Graphics Processing Unit                                |

| HDL   | Hardware Description Language                           |

|       | Integrated Circuit                                      |

| IP    | Intellectual Property                                   |

| ISO   | International Organization for Standardization          |

| JTAG  | Joint Test Action Group                                 |

| RAM   | Random-Access Memory                                    |

| RTL   | Register Transfer Level                                 |

| SBST  | Software-based Self Test                                |

| SA    | Stuck-at                                                |

| SER   | Soft Error Reliability                                  |

| SET   | Single Event Transient                                  |

| SEU   | Single Event Upset                                      |

| SoC   | System-on-Chip                                          |

| STL   | Software Test Library                                   |

| TCL   | Tool Confidence Level                                   |

| TMR   | Triple Modular Redundancy                               |

| UART  | Universal Asynchronous Receiver-Transmitter             |

| VHDL  | Very High Speed Integrated Circuit Hardware Description |

| THE   | Language                                                |

| VLSI  | Very Large-Scale Integration                            |

|       |                                                         |

# **1** Introduction

This PhD thesis addresses functional safety assessment methods targeting automotive Integrated Circuits (IC), emphasizing optimization techniques.

This introductory chapter presents the motivation behind this thesis, formulates the area's problems, lists a summary of the main contributions, and sketches the thesis structure.

#### 1.1 Motivation

In recent years, the use of Systems-on-Chip (SoCs) in automotive has been increasing rapidly. The reason for this is the Advanced Driver-Assistance Systems (ADAS) used in cars or the addition of autonomous-driving features, which is the most popular topic in automotive domain today. [11] reports that today's cars consist of more than 100 electronic control units (ECUs) to handle different applications. ADAS systems such as Adaptive Cruise Controller (ACC) or Emergency Braking Systems (EBS), which can be life-threatening in case of any malfunction, are present in every car today. For this reason, it is crucial that SoCs used in areas where safety is of vital importance, such as automotive or space, operate without failing. Otherwise, it may cause injury or even loss of human lives. Consequently, International Organization for Standardization (ISO) has developed ISO 26262 [12] functional safety standard in 2011 and revised in 2018 targeting design, verification, and validation of safety-critical automotive SoCs against systematic and random faults.

Several reasons can cause a failure in an SoC. First, it is the decreasing trend in the transistor size, which is described by "Moore's Law" [13]. When the advanced technology nodes take place in the design of an SoC, random hardware faults become more effective as shrinking nodes increase the sensitivity of SoCs to aging effects [14] [15] or cosmic radiation [16]. Therefore, as safety-critical SoCs are designed using advanced node technologies, the need for more safe SoCs is increasing accordingly. Second, it is the increasing trend in the density of complex electronic devices inside automotive SoCs. Modern cars have several advanced features to become more autonomous that require the processing of real-life data during driving, monitoring the environment, and analyzing traffic signs. All these tasks increase the SoC density in the cars. Additionally, [17] states that ninety percent of the car novelties are based on electronics that manage the above-mentioned advanced car features, SoCs in automobiles are becoming more susceptible to random hardware faults that can cause data loss and harm human health. As a result, there is a need to design robust and safe SoCs to avoid life-critical failures.

The way of preventing failures in SoCs is to implement fault prevention mechanisms (safety mechanisms) that detect faults or control failures to maintain or achieve a safe state [12] [18]. Safety mechanisms are introduced during the design and verification of the hardware/software system. Examples of safety mechanisms include Built-in-Self-Test (BIST), Error Correction Codes (ECC), or hardware redundancy. However, safety mechanisms increase the design and verification complexity as well as the cost of safety-critical SoCs. For example, one of the widely used hardware redundancy schemes is Dual-Core Lock Step (DCLS) increases the SoC's area and power consumption, whereas some other safety mechanisms have an adverse impact on the SoC performance [19] [20]. Moreover, ISO 26262, the functional safety standard, requires using safety analysis techniques to measure the effectiveness and evaluate the benefits of the implemented safety mechanisms. This necessity also escalates the verification complexity of a safety-critical SoC development flow and makes it difficult to comply with the time-to-market criteria. There-

fore, methods to overcome the complexity are crucial.

In this PhD thesis, we address functional safety analysis of Electrical/Electronic (E/E) systems, particularly SoCs used in automobiles. Its particular significance in industrial applications, including automotive, is the fundamental motivation of this thesis. Additionally, existing techniques adopted by the industry and academia still have considerable drawbacks that leave functional safety assessment a challenging and expensive task. Therefore, this thesis proposes solutions to optimize these techniques such as fault injection, formal analysis, or Automatic Test Pattern Generation (ATPG). In addition to the fact that these mentioned methods are handled separately in the following chapters, how their combination can contribute to functional safety assessment has motivated this thesis.

#### **1.2 Problem Formulation**

Considering all the constraints introduced above, it is mandatory to improve the efficiency of safety analysis techniques to meet the demanding requirements of the automotive industry. ISO 26262 guides functional safety for the SoCs used in automobiles and recommends using some safety analysis techniques. The purpose is to provide evidence that the SoCs can handle faults through their safety mechanisms, and the functionality of the SoC cannot be changed. Even though helpful safety analysis techniques exist in the literature, there is still room for more efficient and optimized methodologies to deal with different functional safety challenges. To be more exact, these safety analysis techniques need optimization, automation, and being more accurate. Therefore, this PhD thesis proposes techniques to make functional safety analysis of automotive SoCs more effective. The following paragraphs formulate the problems in the area.

Functional safety analysis is a complex procedure that requires challenging skills as follows. First, it necessitates prior knowledge about the application scenarios and the target design. Second, it demands to identify possible safety threats, predict their impacts on the results, add safety mechanisms to prevent failures, and evaluate the severity of the faults. In general, these activities happen before the actual design and implementation are made available. Also, this analysis is performed manually based on expert judgment. However, this is error-prone, time-consuming, thus expensive considering the size and complexity of automotive SoCs. Therefore, the manual analysis is tedious, inefficient, and might have an adverse impact on the SoC development cycle. More specifically, when we take fault injection or formal analysis campaigns into account, or when they are used together, it is impossible to have a complete run considering the complexity of designs and applications. These kinds of functional safety campaigns leave a considerable amount of undetected faults, whose effects are unknown but must be identified by experts manually. Consequently, the lack of automated safety approaches to reduce possible human errors and meet the demanding safety requirements of today's cars is a significant problem.

Moreover, along with the design development, the initially defined requirements must be repeatedly observed while a detailed analysis is performed to provide evidence that these safety requirements are achieved. Nevertheless, the size and complexity of SoCs pose a severe problem in this step, and all functional safety analysis techniques such as fault injection or formal analysis suffer from this issue. In other words, modern automotive SoCs consist of large amounts of faults up to millions; hence, the execution of safety analysis methods on these SoCs requires a long time to obtain significant statistical results. As a result, the industry adopted the "divide and conquer" approach, which is mapping the requirements to the corresponding design components to enable a safety analysis on only safety-related design parts [21]. However, even with this solution, functional safety analysis campaigns are more costly and even unfeasible considering complex ECUs that perform various application scenarios that automate the car [22]. This also shows that not only hardware complexity but also real-world applications that SoCs execute need to be carefully considered for efficient functional safety analysis. On the other hand, characterization of these applications (workloads) is a challenge and needs to be carefully performed to develop optimized methods and techniques that speed up functional safety analysis and reduce the cost of the SoC design and verification cycle.

Also, the development of test environments that runs functional safety analysis is another problem. The test environment is necessary to obtain a confident assessment of results generated by the tools in the context of ISO 26262. This implies that compelling methodologies that reduce the efforts of test environment development are necessary. Furthermore, the attempts to unify functional safety analysis tools/technologies and their strengths create a competent campaign, making all kinds of analysis and their results more confident. Hence, it is required to have this environment supporting ISO 26262 compliant automotive SoC development.

Additionally, there is a lack of open-source resources in the functional safety research community. The high need to evaluate the quality of results on automotive representative SoCs makes any research on the area more challenging. Moreover, both hardware and software resources must be available to demonstrate various use cases. Also, providing a representative automotive SoC that has several safety mechanisms capable of detecting random faults is essential. Nevertheless, it is a problem to access this kind of comprehensive automotive SoC with a modular structure, enabling more detailed research.

### **1.3 Research Objectives**

Considering the above problems, the main goal of this PhD thesis is based on addressing them in the following ways:

- Proposing a novel methodology that combines different fault analysis tools. The idea is to increase tool confidence level as guided by ISO 26262.

- Providing an open-sourced benchmark to support functional safety research, enabling comprehensive and automotive representative SoC with all required hardware and software resources.

- Optimizing fault injection campaigns by the analysis of workloads that run on the target designs. The main idea is to select critical faults to be injected and so prune the large fault lists.

- Enhancing hardware fault classification, which is normally done manually based on expert judgment. Analysis of the software application (workload) automatically and translation of this behavior to the formal properties accurately are aimed.

## **1.4 Contributions**

The main objective of this PhD thesis is to propose methodologies to leverage the most advanced functional safety analysis techniques. Contributions of this PhD thesis in tackling the challenges explained in Chapter 1.2 consist;

• Mitigation of the drawbacks caused by the different classification characteristics of fault analysis tools is addressed in this PhD thesis. Also, the applicability and feasibility of these tools are investigated.

Taking the advantage of the strength of one specific fault analysis tool as a starting point, fault injection campaigns are optimized, providing better coverage.

Unified application of three tools, processing and report generation, are the main features.

More details about this approach is clarified in Chapter 3.

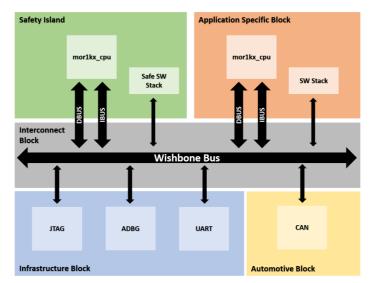

• Filling the gap in the research community by proposing representative automotive SoC is studied in the context of this thesis. The requirements of an automotive SoC are examined by inspecting several commercial alternatives.

The approach shall be oriented towards seamless hardware and software resources, modular SoC structure enabling adding peripherals, different safety configurations in compliance with ISO 26262.

The ultimate goal of this work is to build a representative automotive SoC, supporting functional safety researches, which needs an open-source platform to assess the quality of the results.

Chapter 4 provides the details of the proposed approach.

• Accelerating fault injection campaigns targeting transient faults is investigated in the context of this thesis. Starting with a state-of-the-art study of the main fault injection acceleration techniques applied in the industry and academia, efficient methodologies are developed to prune the fault lists of transient fault injection campaigns.

The main objective of this approach is to initiate a general and well-structured description of fault injection campaigns, in particular simulation-based fault injection, which supports industrial-grade automotive SoCs and applications.

A key milestone in the proposed approach is the workload characterization and identification of critical and non-critical time steps, mapping faults between abstraction levels, and pruning the transient fault list accordingly.

More detailed explanations are given in Chapter 5.

• Enhancing hardware fault classification using formal analysis is investigated in this thesis. Starting with an analysis of software application and development of formal properties, safe fault identification is intensified.

The main aim of this research is to an analysis of a complete automotive SoC when it runs an automotive representative application software. Furthermore, characterization of the faults on peripherals is also targeted when the application software uses them.

Automated formal property generation, processing, and combination of formal analysis and fault injection to achieve safety metrics driven by ISO 26262 are considered.

The results and details for enhancing the hardware fault classification approach are elicited in Chapter 6.

## 1.5 Thesis Organization

This thesis consists of seven main chapters. The rest of it is organized as follows.

• Chapter 2 provides a background information about functional safety and ISO 26262 standard to familiarize the reader with the basics.

- Chapter 3 points out combination of fault analysis technologies to increase tool's confidence level, and have a better detection rate using the strength of the ATPG.

- Chapter 4 defines a open-source and comprehensive automotive SoC, the AutoSoC, to support research targeting functional safety.

- Chapter 5 starts with the discussion about the challenges of fault injection campaigns and then provides a solution to prune the fault lists.

- Chapter 6 explains enhancing hardware fault classification in an automotive SoC using formal methods.

- Chapter 7 draws conclusions for the presented PhD thesis and discusses possible future directions in the functional safety scope.

Also, at the end of the thesis, the research papers mentioned in the context of this PhD are attached as appendixes.

# 2 Background on Functional Safety and ISO 26262

This chapter initially overviews the functional safety and its usage areas. Then, automotive functional safety is detailed further to give the reader more information about the main scope of the presented research.

## 2.1 Functional Safety: A General Overview

In general, functional safety refers to the concept that a system (typically an SoC, or an IP) will remain dependable and function as intended even in an unexpected occurrence, which is termed a failure. Failures can be due to random hardware faults (e.g., short circuits) or systematic design errors (e.g., defects in software). Furthermore, the possible risk posed by these failures must be reduced by either minimizing the probability of a failure occurring or restricting the aftereffects of unavoidable failures. Concerning safety-critical areas such as automotive, planes, or medical devices, embedded electronics have increased significantly, and therefore, there is an increased emphasis on functional safety in the designs used in these areas.

The use of advanced node technologies that are adopted increasingly for performance and reduced area/power escalates susceptibility of SoCs to radiation sources and aging effects. However, these two impacts cause the device to malfunction temporarily or permanently. Moreover, malfunctioning of an SoC used in safety-critical areas might pose a significant risk even for a short period. Consequently, several standards have been developed to make the system safe.

The following sub-chapter explains application areas and relates standards developed for safety-critical areas.

#### 2.1.1 Application Areas and Related Standards

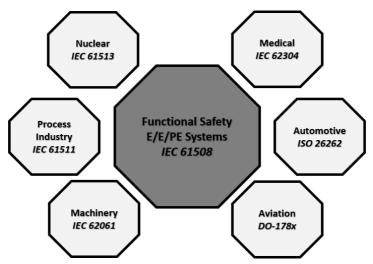

IEC 61508 [23] is the international standard that provides generic guidelines for the specification, design, and operation of Electric/Electronic and Programmable Electronic (E/E/PE) systems used in safety-critical areas. It is a generic safety standard and serves as the basis for drafting the functional safety guidelines tailored to the respective industry sectors. Fig. 1 gives an overview of functional safety standards. This illustration explains that IEC 61508 supported the development of safety standards applied to process industry, nuclear, medical, machinery, aviation, automotive, and many others that are not included in Fig. 1.

Among these standards, ISO 26262 [12] "Road Vehicles - Functional Safety" has been published in 2011, targeting the automotive industry. This standard addresses series production passenger cars up to 3500 kilograms. Moreover, ISO 26262 [12] targets the highvolume mass-market automotive industry, whereas IEC 61508 deals with the systems produced in low volumes. In this thesis, the focus is on the ISO 26262 functional safety standard. Hence, the following sub-chapters give a detailed study of the standard.

# 2.2 Automotive Functional Safety: ISO 26262

Being the adaptation of IEC 61508, ISO 26262 is a functional safety standard titled "Road Vehicles - Functional Safety". It was first published in 2011 as a functional safety standard for the automotive industry. Then, its revised second edition was released in 2018. This second edition has broader scope by removing the vehicle mass limitation mentioned in Chapter 2.1.1 and also includes two additional chapters for guidelines on the application of ISO 26262 to semiconductors and the adaptation for motorcycles.

According to the ISO 26262, functional safety is described as the "absence of unrea-

Figure 1: Overview of Functional Safety Standards in Different Industry Sectors

sonable risk due to hazards caused by malfunctioning behavior of electrical/electronic systems". This definition shows that functional safety in automobiles is actually a chain of implications [18] as presented in Fig. 2. It starts with the malfunction definition and targets risk reduction as a final goal.

Figure 2: ISO 26262 Chain of Implications [18]

In general, ISO 26262 performs the following tasks:

- It guides to avoid risk in creating a safety-critical system.

- It regulates critical testing processes.

- It introduces Automotive Safety Integrity Levels (ASILs) to specify the item's necessary safety requirements to achieve an acceptable residual risk.

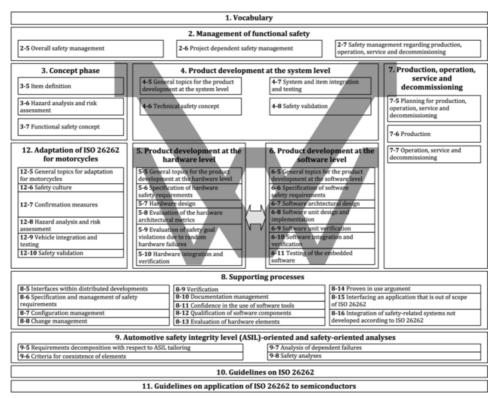

ISO 26262 is based on a V-model, shown in Fig. 3, as a reference process for the different phases of product development. ISO 26262 contains twelve parts covering all required activities to ensure the functional safety of E/E components used in automobiles. These are summarized as follows:

• In Part 1: *Vocabulary*, necessary terms are introduced such as ASIL, item, system, element, and many others.

- In Part 2: *Management of Functional Safety*, the process for management of functional safety for automotive applications is outlined, and the automotive safety lifecycle is introduced.

- In Part 3: *Concept Phase*, activities to be performed are specified. These activities are Item Definition, Hazard and Risk Analysis (HARA), Safety Goals Definition, ASIL Determination, and definition of Functional Safety Requirements. This part is applied during the early phase of product development.

- In Part 4: *Product Development at the System Level*, Technical Safety Requirements are derived for each Functional Safety Requirement defined in the previous chapter with respect to hardware and software components.

- In Part 5: *Product Development at the Hardware Level*, requirements for product development on the hardware level are defined. This part covers hardware design and evaluation of architectural hardware metrics. Also, an assessment of safety goal violation because of random failures is performed.

- In Part 6: *Product Development at the Software Level*, specifications for software safety are defined in this part. Additionally, qualitative analyses, like Failure Tree Analysis (FTA) and Failure Mode and Effect Analysis (FMEA), are used in the context of this part.

- In Part 7: *Production and Operation*, requirements for system production, operation, installation, servicing, decommissioning are specified.

- In Part 8: *Supporting Processes*, requirements for processes that support the development effort, including documentation standards, tool qualification, verification, and validation, are mentioned.

- In Part 9: Automotive Safety Integrity Level-Oriented and Safety-Oriented Analyses, all aspects regarding the ASIL-oriented requirements are explained. Analysis of dependent failures is also covered.

- In Part 10: *Guideline on ISO 26262*, an overview of the standard is summarized to improve the understanding of other parts.

- In Part 11: Guideline on Application of ISO 26262 to semiconductors, information to support semiconductor manufacturers and silicon intellectual property is provided to address how suppliers and integrators work together.

- In Part 12: Adaptation of ISO 26262 for Motorcycles, standard is specified for motorcycles.

# 2.3 Failure Types

ISO 26262 classifies malfunction of E/E component into *Systematic Failures*, *Random Hardware Failures*, and *Dependent Failures*. This section discusses these three types of failures in detail.

• **Systematic Failures**: According to Part 1 of the standard [12], these are the failures in an item or function that are caused in a deterministic way during development, manufacturing, or maintenance. Systematic failures can only be eliminated by changing the design or the manufacturing process, operational procedures, or other relevant factors.

Figure 3: General Overview of ISO 26262 [12]

- **Random Hardware Failures**: These failures occur unpredictably during the lifetime of a hardware element, and that follows a probability distribution. To prevent Random Hardware Failures, it is necessary to deploy safety mechanisms to make the architecture able to detect and correct malfunctions.

- **Dependent Failures**: These failures are defined as the failure of more than one element stemming from a single root. The main reason for these failures is environmental conditions, aging, or failures of mutual external sources such as power supply. They can be curtailed by supervision of clock, power, temperature, and independent failure signaling [11].

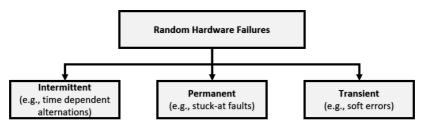

Concerning Random Hardware Failures, Fig. 4 shows that they can be caused by three types of faults based on their duration. These are Intermittent, Permanent, and Transient faults that are explained below:

- Intermittent Faults: These are faults in a hardware element that appear, disappear, and then reappear after some time. In other words, an intermittent fault occurs at intervals, usually irregular, in a target system that functions normally at other times. They are caused by poor solder joints, corrosion on connector contacts. Time-dependent alternations in hardware are an example of this type of fault. Thus, these are temporary faults.

- **Transient Faults**: A Transient fault is a malfunction of a device or system that remains active for a short period of time with respect to the device or system mission

time. A well-known example of a transient fault is a soft error that hits a device's memory elements and flips the bit from 0 to 1 or 1 to 0. If this happens, the state of a few bits is changed; however, there is no lasting damage to the device.

• **Permanent Faults**: Permanent faults occur and stay until corrective action is taken. Burn-out hardware or disk head crashes are an example of permanent faults.

Figure 4: Random Hardware Failure Causes

#### 2.3.1 Fault Models

In order to analyze the effect of hardware faults listed above, fault models must be used on the target design. Even if fault models are not perfect representations of what is happening on a real design, they help design test cases or procedures to mimic and simulate faulty conditions and develop safety mechanisms. In this way, safety-critical designs can be tested whether safety requirements are met even if some hardware components fail or not.

There are two fault models adopted by the industry as listed and explained below:

• **Stuck-at Fault Model**: The stuck-at (SA) model is widely used to address the test of ICs. It is a particular fault model used by ATPG tools to mimic a manufacturing defect within an IC.

The model assumes that a signal is forced to either O (SAO) or 1 (SA1). Thus, it can be applied to any signal, such as nets or registers.

• Single-Event-Upset (SEU) and Single-Event-Transient (SET) Fault Models: A SEU is a change of state caused by ionizing particles such as electrons or photons that strike a sensitive node in a device. The model inverts the value of a sequential element's output and holds the modified value until it is assigned a new value. It is applied only on the outputs of sequential components such as flip-flops, latches, or memories.

The SET fault model inverts the value of a signal and holds the value for a specified period of time. It can be employed to any kind of signal, such as nets or registers, as opposed to SEU.

## 2.4 Safety Mechanisms

Safety mechanisms should be introduced to address random hardware failures. According to the ISO 26262: Part 1 [12], a safety mechanism is a technical solution implemented by E/E functions or elements, or by other technologies, to detect faults or control failures to achieve or maintain a safe state.

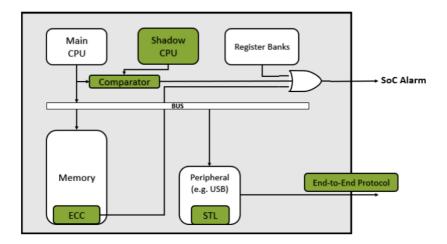

In other words, safety mechanisms are protection mechanisms. They can be implemented using hardware or software techniques. Fig. 5 illustrates an example SoC that

Figure 5: Example Safety Mechanisms in an SoC

has several safety mechanisms. In this example, some major hardware components are protected as follows:

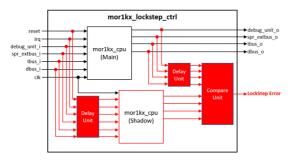

- **CPU**: A shadow CPU, which is the copy of the main, and a comparator are used as a hardware safety mechanism to protect the CPU. This is a typical implementation of DCLS.

- Memory: The memory in the example has ECC as a hardware safety mechanism.

- USB: Software Test Library (STL) is shown as a software safety mechanism that protects USB. Also, End-to-End Protocol can be used for the transferred data.

- **SoC Alarm**: This safety mechanism works when one of the safety mechanisms mentioned above sets the alarm. In this case, the system is switched to a safe state.

The safety mechanisms shown in Fig. 5 are selected as they are relevant to this PhD thesis. Besides the listed mechanisms above, there are other well-known safety mechanism implementations such as watchdog (program sequence monitor), hardware logic BIST, or ECC mechanisms on instruction cache, data cache, buses, and others. In addition, ISO 26262: Part 5 proposes several categories of safety mechanisms targeting processing units and volatile memory with typical achievable Diagnostic Coverage (DC).

Moreover, safety mechanism selection must be carried out carefully, considering the trade-offs between effectiveness and cost. This selection must evaluate power consumption, area, safety metrics, and timing performance all together for a specific building block [24]. For example, DCLS and Triple Modular Redundancy (TMR) have high area overhead and low-performance impact. On the other hand, a simple parity safety mechanism has lower area overhead and performance impact than DCLS and TMR.

## 2.5 Functional Safety Analysis

Functional safety analysis is utilized to assess the target product's safety level, which is typically an IP or an SoC. In general, these analysis techniques are grouped into quantitative evaluations and qualitative assessments. Quantitative evaluations are Failure Mode

Effect and Diagnostic Analysis (FMEDA) or timing analysis. On the other hand, Dependent Failure Analysis (DFA) is a well-known example of qualitative assessment.

The following sub-chapter exemplifies the quantitative assessment following the structure of FMEDA.

#### 2.5.1 Quantitative Assessment of Hardware Architectures

The incorporation of several protection mechanisms in a safety-critical design requires the evaluation of their safety level. ISO 26262 addresses this issue through quantitative assessments to determine a hardware architecture's Automotive Safety Integrity Level (ASIL). Four ASILs are defined in ISO 26262, where ASIL-A represents the least stringent level, and ASIL-D is the most stringent level [12]. In order to decide the ASIL of a target design, hardware architectural metrics are designated in ISO 26262. Hardware architectural metrics measure the effectiveness of safety mechanisms to detect random hardware failures. In other words, these metrics assess the overall likelihood of risk.

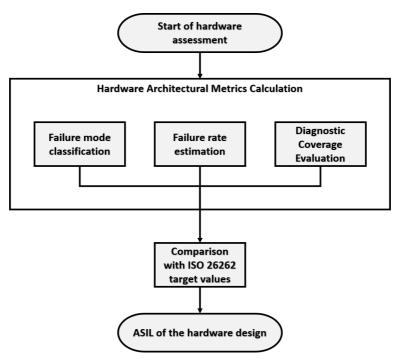

The hardware architecture assessment flow is demonstrated in Fig. 6. In order to obtain ASIL of the hardware design, it is necessary to calculate hardware architectural metrics, which their definitions and equations are provided in the subsequent sub-chapters. In general, this calculation is performed by failure mode classification, estimation of hardware elements' failure rates, and deployed safety mechanisms' DC evaluation. Finally, using the obtained results, the ASIL of the target design can be determined using predefined values in ISO 26262.

In this sub-chapter, initially, failure modes classification is explained in detail. Then, hardware architectural metrics are introduced together with failure rate estimation of hardware components and diagnostic coverage evaluation of safety mechanisms.

Figure 6: Hardware Architecture Assessment Flow in the context of ISO 26262 (adapted from [25])

#### 2.5.1.1 Failure Modes Classification

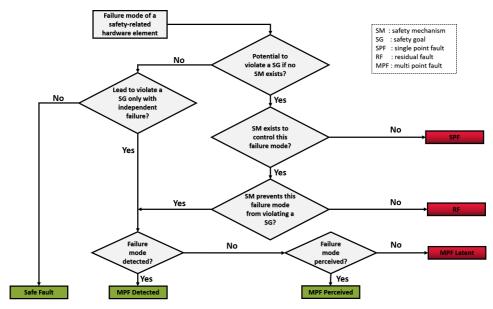

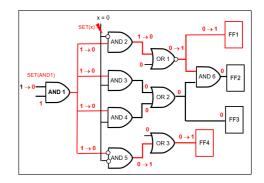

ISO 26262: Part 5 classifies the failure modes of a hardware element in order to calculate hardware architectural metrics, which will be explained later. Fig. 7 demonstrates the flow diagram of failure mode classification. A failure mode could be classified into the following types, where  $\lambda$  stands for the failure rate [12], which is defined as the frequency in which a component fails:

- Safe Fault  $(\lambda_{\text{S}}) {:}$  A safe fault does not violate a safety goal.

- Multiple Point Fault  $(\lambda_{MPF})$ : A MPF may lead to a violation of a safety goal in conjunction with another independent faults. There are three types of an MPF;

- A Perceived MPF ( $\lambda_{\text{MPF,P}}$ ) cannot directly violate a safety goal, but their presence can be perceived by the driver due to performance decline or any other similar negative implication. However, they are not identified by safety mechanisms.

- A Detected MPF  $(\lambda_{MPF,D})$  is identified by safety mechanism as opposed to a perceived MPF. They are detected within a specified time.

- A Latent MPF( $\lambda_{MPF,L}$ ) is neither identified by a safety mechanism nor a driver.

- Single Point Fault  $(\lambda_{\text{SPF}})$ : It is a non tolerated fault that directly violates a safety goal.

- **Residual Fault**  $(\lambda_{RF})$ : A RF is not detected by any safety mechanism and lead to a violation of a safety goal.

Consequently, the failure rate of each safety-related hardware element is stated using (1). Also, we here note that Chapter 2.5.1.3 explains how  $\lambda$  is obtained in the context of ISO 26262.

$$\lambda = \lambda_{S} + \lambda_{SPF} + \lambda_{RF} + \lambda_{MPF}$$

(1)

#### 2.5.1.2 Hardware Architectural Metrics

The effectiveness of safety mechanisms that detect the failure mode needs to be measured by the three metrics listed and detailed below to control faults. In other words, these metrics assess functional safety for hardware components in the context of ISO 26262. Additionally, they support design evaluation and determination of whether or not the deployed safety mechanisms have the sufficient capability to control faults.

These metrics are reported in ISO 26262:Part-5 [12] with their description and formulas. They are defined as follows;

• Single-Point Fault Metric (SPFM): This metric reflects the effectiveness of the safetyrelated design to protect from a single point and residual faults. Effective safety mechanisms in the design result in few residual faults and higher SPFM. On the contrary, unprotected design parts bring about many single point faults and lower SPFM. Last, many safe faults cause higher SPFM.

SPFM is calculated using (2), where SR stands for safety-related,  $\lambda_{SPF}$  is the failure rate associated with single point faults,  $\lambda_{RF,est}$  is the estimated failure rates associated with with respect to residual faults, and  $\lambda$  denotes the failure rate corresponding to all hardware faults as calculated in (1). Additionally, (3) shows the calculation of  $\lambda_{RF,est}$ , where *c* is the DC with respect to residual faults.

Figure 7: Failure Mode Classification Flow Diagram [25]

$$SPFM = 1 - \frac{\sum_{SR,HW} (\lambda_{SPF} + \lambda_{RF,est})}{\sum_{SR,HW} \lambda}$$

(2)

$$\lambda_{\text{RF,est}} = \lambda \times (1 - \frac{c_{\text{DC,RF}}}{100})$$

(3)

• Latent Fault Metric (LFM): This metric reflects the effectiveness of the safety architecture to protect from latent faults, which are a subset of multiple point faults. Many single point faults or residual faults imply higher LFM. Many detected multiple point faults result in higher LFM. Also, many safe faults cause higher LFM.

LFM is determined by (4), where  $\lambda_{MPF,L,est}$  denotes the estimated failure rate with respect to latent multiple point faults. Also, (5) provides the calculation of  $\lambda_{MPF,L,est}$ .

$$LFM = 1 - \frac{\sum_{SR,HW} \lambda_{MPF,L,est}}{\sum_{SR,HW} (\lambda - \lambda_{SPF} - \lambda_{RF})}$$

(4)

$$\lambda_{\text{MPF,L,est}} = \lambda \times (1 - \frac{c_{\text{DC,MPF,L}}}{100})$$

(5)

• **Probabilistic Metric of Hardware Failures (PMHF)**: This metric explains that the residual risk of a safety goal violation is sufficiently low [18] [25]. The calculation of PMHF is not provided in ISO 26262, even if it is proposed as one of the alternatives of the probabilistic metrics.

#### 2.5.1.3 Failure Rate Estimation

As shown in Fig. 6, after failures are classified according to the ISO 26262, and as explained in Chapter 2.5.1.1, failure rate estimation can be performed to be used in the metrics introduced above. In another saying, hardware architectural metrics (SPFM and LFM) can be designated by the estimation of failure rates.

For this step, ISO 26262 describes several methods as follows:

- Using recognized industry reliability data books such as IEC 61709, IEC TR 62380, MIL-HDBK-217F.

- Making use of statistical data collected based on tests or field returns.

- Exploiting an expert judgment.

Using one of these methods, the failure rate of a hardware component (e.g., register file, arithmetic logic unit, or instruction memory) is estimated in units of Failure In Time (FIT), which is the number of failures per billion hours. For example, 1 FIT means that the device has a mean time to failure (MTTF) of 1 billion hours [12].

#### 2.5.1.4 Diagnostic Coverage Evaluation

As a next step, DC is assessed. DC shows the effectiveness of the safety mechanism at detecting faults [18], and it is evaluated in this step to calculate the estimated failure rates used in (2) and (4).

DC can be calculated analytically if the target design deploys some standard safety mechanisms such as an ECC. However, even if there is a standard safety mechanism, this computation must be performed considering the specific parts of the logic separately. For example, the DC may be accurate on the data cell of the memory but not for the decoder in front of the memory [18]. In this kind of situation, it might be too challenging to achieve higher safety levels such as ASIL-D. Therefore, it may require to perform more accurate safety analysis techniques such as fault injection. On the other hand, if the target design deploys custom safety analysis techniques, such as STLs, DC cannot be calculated analytically; hence, functional safety analysis techniques, such as fault injection, must be employed in this case for a more accurate calculation. However, these analysis techniques need optimization to be more efficient and less costly, which is the main scope of this PhD thesis.

#### 2.5.1.5 Comparison with ISO 26262 Target Values

After DC is estimated and evaluated using functional safety analysis techniques, all the prerequisites for the calculation of hardware architectural metrics are ready. Using the formulas given in (2) and (4), metrics are calculated and compared with ISO 26262 target values.

For hardware components, the ASIL requirements regulate the values to achieve for the metrics as shown in Table 1. The calculated SPFM and LFM values are compared to use the values given in this table and finally ASIL of the hardware is determined.

#### 2.5.2 Qualitative Assessment of Hardware Architectures

As opposed to quantitative techniques, qualitative assessment comes into prominence when the target system has shared sources. Therefore, the analysis of dependent failures [26], which is described in Chapter 2.3, is required to investigate the possible common cause and cascading failures between design elements. In other words, it determines that

| ASIL | Failure Rate | SPFM         | LFM          |

|------|--------------|--------------|--------------|

| Α    | <1000 FIT    | not relevant | not relevant |

| В    | <100 FIT     | $\geq 90\%$  | $\geq 60\%$  |

| С    | <100 FIT     | $\geq 97\%$  | $\geq 80\%$  |

| D    | <10 FIT      | $\geq$ 99%   | $\geq 90\%$  |

Table 1: Metrics for Each ASIL

safety requirements to reduce the dependencies between the elements are in alignment with safety requirements and have been met.

An example can be given using ADAS in the car. For example, an ASIL-B compliant communication module measures the distance from the front car and sends this data to a cruise controller module that adopts the course of an action in terms of accelerating or braking. However, any glitch or fault on the communication module can create a fatal situation. Therefore, it would be necessary to assess ASIL of this communication module again, which causes additional expenses. In this case, DFA can be used to avoid such a situation.

Additionally, ISO 26262 provides some dependent failure examples such as clock elements, power supply elements, or reset logic, as shared resources exist. Also, typical countermeasures are listed by ISO 26262 as clock monitoring for shared clock resources, physical separation, or isolation for fault avoidance.

### 2.6 Fault Injection

In Chapter 2.5.1.4, it was stated that fault injection is required in order to have more accurate DC calculation, especially in case the target design deploys custom safety mechanisms. Even if its details are investigated in the subsequent sub-chapters in the context of the research which uses fault injection, in this part, we give the fault injection types and how they differ from each other.

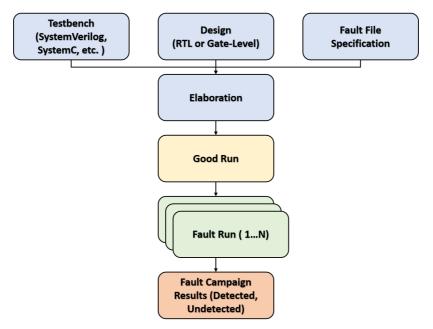

In general, fault injection is the simulation of fault effects on the target design. The purpose is to determine the behavior of faults. Several fault injection techniques have been introduced in academia and the industry. The techniques are classified into the following categories [27] [28] [29]:

• Hardware-based Fault Injection: This type of fault injection is performed at the physical level through extra components such as contacts.

However, using extra hardware components affects the target hardware as it may disturb the power supply by producing voltage and current changes, it may distract the hardware with environmental parameters such as heavy-ion radiation, and it may modify the value of circuit pins.