# THESIS ON POWER ENGINEERING, ELECTRICAL ENGINEERING, MINING ENGINEERING D60

# Research and Development of the New Topologies for the Isolation Stage of the Power Electronic Transformer

VIKTOR BELDJAJEV

# TALLINN UNIVERSITY OF TECHNOLOGY

Faculty of Power Engineering Department of Electrical Engineering

Dissertation was accepted for the defence of the degree of Doctor of Philosophy in Engineering on May 20, 2013

**Supervisors:** Dr. Dipl. Ing. Indrek Roasto, Department of Electrical Engineering, Tallinn University of Technology.

Prof. Tõnu Lehtla, Department of Electrical Engineering, Tallinn University of Technology.

Prof. Dr.-Ing. Marius Klytta, Department of Electrical Engineering and Automation, Technical University of Applied Sciences Mittelhessen, Germany.

**Opponents:** Prof. D. Sc. (Tech.) Pertti Silventoinen, Laboratory of Applied Electronics, Lappeenranta University of Technology, Finland.

Ph. D. Marek Jasinski, Institute of Control and Industrial Electronics, Warsaw University of Technology, Poland.

Defence of the thesis: June 20, 2013

### **Declaration:**

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for any academic degree.

Viktor Beldjajev.....

Copyright: Viktor Beldjajev, 2013 ISSN 1406-474X ISBN 978-9949-23-481-3 (publication) ISBN 978-9949-23-482-0 (PDF)

# Jõuelektroonilise trafo isolatsioonilüli uudsete topoloogiate uurimine ja arendamine

VIKTOR BELDJAJEV

# **Contents**

| Abbrevi   | ations                                                              | 6    |

|-----------|---------------------------------------------------------------------|------|

| Symbols   | 5                                                                   | 7    |

| List of A | Author's Publications                                               | 9    |

| 1 INTE    | RODUCTION                                                           | 11   |

| 1.1       | Background                                                          | 11   |

| 1.2       | Main Hypotheses and Objectives of the Thesis                        |      |

| 1.3       | Contribution of the Thesis and Dissemination                        |      |

| 2 TEC     | HNOLOGICAL OVERVIEW                                                 |      |

| 2.1       | Topologies of the PET                                               | 17   |

| 2.2       | Topologies for the Isolation Stage                                  |      |

| 2.3       | Summary                                                             |      |

| 3 NEW     | POWER ELECTRONIC BUILDING BLOCKS FOR THE                            |      |

| ISOLAT    | TION STAGE                                                          | 25   |

| 3.1       | Improved Modulation Method                                          | 26   |

| 3.2       | Current Doubler Rectifier with Bi-directional Power Flow Capability |      |

| PEBE      | }                                                                   | 27   |

| 3.3       | Quasi-Z Source Inverter PEBB                                        | 32   |

| 3.4       | Current-Fed DC/DC Converter with an Active Clamp PEBB               | 35   |

| 3.5       | Voltage Regulation Range                                            | 36   |

| 3.6       | Laboratory Test Bench                                               | 37   |

| 3.7       | Summary                                                             | 38   |

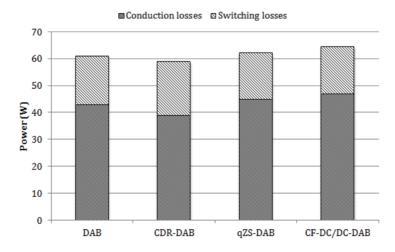

| 4 COM     | IPARISON AND ANALYSIS                                               | 40   |

| 4.1       | Conduction and Switching Losses                                     | 40   |

| 4.2       | Current and Voltage Stress                                          | 43   |

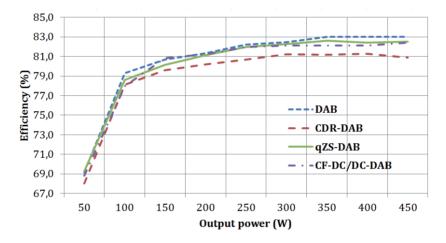

| 4.3       | Efficiency                                                          | 44   |

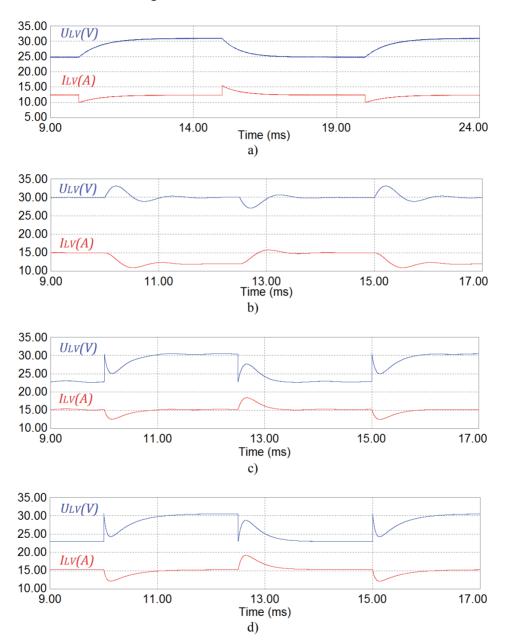

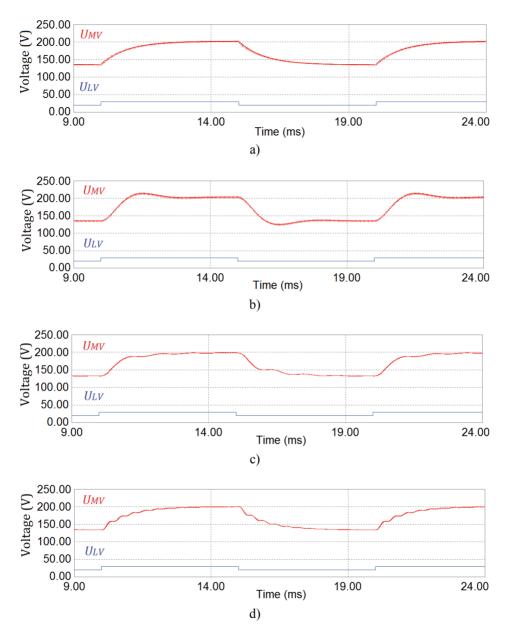

| 4.4       | Dynamic Analysis                                                    | 46   |

| 4.5       | Summary                                                             | 51   |

| 5 FUT     | URE WORK                                                            | . 53 |

| Referen   | ces                                                                 | 55   |

| Acknow    | ledgement                                                           | 59   |

| Abstract  |                                                                     | 60   |

|           | õte                                                                 |      |

|           | rjeldus                                                             |      |

|           | um Vitae                                                            |      |

| Appendi   |                                                                     | 69   |

# **Abbreviations**

ADN active distribution network

CCM continuous conduction mode

CDR current doubler rectifier

CF-DC/DC current-fed DC/DC

DAB dual active bridge

DCM discontinuous conduction mode

DG distributed generation

DHB dual half bridge

FB full bridge

HB half bridge

HF high frequency

HP high power

HV high voltage, 100 kV...230 kV (according to ANSI C84.1)

IGBT Insulated Gate Bipolar Transistor IMM improved modulation method

LC circuit consisting of inductance L and capacitance C

LFT line frequency transformer

LLC resonant circuit consisting of two inductors and one capacitor

LLC-HB HB with and LLC network

LV low voltage, below 1 kV (according to ANSI C84.1)

MF medium frequency

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MV medium voltage, 1 kV...100 kV (according to ANSI C84.1)

PEBB power electronic building block

PET power electronic transformer

PFC power factor correction

PSM phase shift modulation

PV photovoltaic

PWM pulse width modulation qZSI quasi-Z source inverter

RCD resistor-capacitor-diode snubber

TR transformer

VSI voltage source inverter ZCS zero current switching

ZV zero voltage

ZVS zero voltage switching

# **Symbols**

$A_e$  transformer's core area

b boost factor

$B_{MAX}$  maximal flux density of the transformer

C capacitanceD duty cycle

$D_4$  relative duration of the active state

$D_{A,MAX}$  maximal relative duration of the active state relative duration of the shoot-through state

$D_{S,MAX}$  maximal relative duration of the shoot-through state

$D_Z$  relative duration of the zero state  $D_{\varphi}$  relative duration of the phase shift

$f_s$  switching frequency i(t) instantaneous current

$I_{aux,AV}$  average current through the auxiliary transformer

$I_{AV}$  average transformer current during the half switching period

$I_{C,AV}$  average collector current of the IGBT  $I_{C,RMS}$  RMS value of the IGBT's collector current

$I_{DAV}$  average value of the diode current

$I_{IN}$  input current  $I_{OUT}$  output current

$I_{T6,MAX}$  peak current through transistors  $T_6$  (and  $T_8$ ) of the CDR PEBB

$I_{Taux}$  average auxiliary switch  $T_{aux}$  current of the CDR PEBB

$I_{TR}$  transformer RMS current

$I_{Tx}$  switch current

$I_{X,VSI}$  current through the corresponding element in the VSI (in p.u.)

$k_I$  current ripple factor  $\Delta I/I_{AV}$  $k_U$  voltage ripple factor  $\Delta U/U_{DC}$

L inductance

$L_{aux}$  leakage inductance of the  $TR_{aux1}$  and  $TR_{aux2}$  of the CDR PEBB

$L_{TR}$  equivalent leakage inductance of the transformer

$N_{aux}$  turn's ratio of the auxiliary transformers  $N_{aux,MIN}$  minimum auxiliary transformers turn's ratio

$N_{TR}$  turns ratio of the transformer  $N_{LV}$  number of turns on the LV side  $N_{MV}$  number of turns on the MV side

P active power

$P_D$  diode conduction losses  $P_{IGBT}$  IGBT conduction losses  $P_{LV}$  power on the LV port

$P_{LV,MAX}$  maximal transferred power in the reverse operating mode

$P_{MV}$  power on the MV port switching losses

R resistance

$r_{aux}$  active resistance of the auxiliary transformer windings

$r_C$  on-state resistance of the IGBT

$r_D$  on-state resistance of the freewheeling diode  $r_L$  active resistance of the filter inductance

u(t) instantaneous voltage

$U_{CE}$  collector to emitter voltage drop of the IGBT

$U_D$  voltage drop on the freewheeling diode of the IGBT  $U_{D,REV,MAX}$  steady state voltage stress on the diodes  $D_{aux1}$  and  $D_{aux2}$  voltage on the LV side terminals of the MF transformer

$U_{LV}$  low side voltage

$U_{LV,DC}$  low side DC-link voltage  $U_{MV}$  medium side voltage

$U_{MV,DC}$  medium side DC-link voltage

$U_{SLMAX}$  blocking voltage over the switch  $S_I$  of the qZSI-PEBB

$U_{Tx}$  steady state voltage on the switch

$U_{T6,MAX}$  steady state voltage stress on the transistor  $T_6$  and  $T_8$  of the CDR  $U_{Taux,MAX}$  maximum voltage stress on the auxiliary switch  $T_{aux}$  of the CDR

$U_{TR,P}$  voltage on the transformer primary  $U_{TR,S}$  voltage on the transformer secondary

$U_{X,VSI}$  voltage across the corresponding element of VSI (in p.u.)

t time

$t_A$  duration of the active state  $t_{off}$  turn OFF time of the switch turn ON time of the switch

$T_{\rm S}$  PWM period

$t_S$  duration of the shoot-through state

$t_Z$  duration of the zero state  $t_{\varphi}$  duration of the phase-shift

$TR_{aux1}$  auxiliary transformer 1 of the bi-directional current doubler  $TR_{aux2}$  auxiliary transformer 2 of the bi-directional current doubler

$\eta$  efficiency

$\varphi$  phase shift angle

$\Delta i$  peak-to-peak current ripple inductor current ripple

$\Delta i_{TR}$  peak-to-peak transformer current ripple

$\Delta u$  peak-to-peak voltage ripple

# **List of Author's Publications**

The present doctoral thesis is based on the following publications that are referred to in the text by Roman numbers.

- [PAPER-I] **Beldjajev, V**., Roasto, I. State of the Art Trends and Design Challenges of Power Electronic Transformer for Future Distribution Grids. Технічна електродинаміка, Alushta, Ukraine, 17-22 September 2012, pp. 55 62.

- [PAPER-II] **Beldjajev, V.**, Roasto, I., Lehtla, T. Intelligent Transformer: Possibilities and Challenges. Scientific Journal of Riga Technical University: Power and Electrical Engineering, Vol. 4, No. 29, 2011, Latvia, pp. 95 100.

- [PAPER-III] **Beldjajev, V.**, Roasto, I., Vinnikov, D. Analysis of Current Doubler Rectifier Based High Frequency Isolation Stage for Intelligent Transformer. 7<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2011), Tallinn, Estonia, June 01-03, 2011, pp. 336 341.

- [PAPER-IV] **Beldjajev, V**., Roasto, I. Impact of Component Losses on the Efficiency of the Bi-Directional Current Doubler Rectifier Based Isolation-Stage. The 38th Annual Conference of the IEEE Industrial Electronics Society (IECON2012), Montreal, Canada, 25-28 October 2012, pp. 5209 5214.

- [PAPER-V] **Beldjajev, V**., Roasto, I. Efficiency and Voltage Characteristics of the Bi-Directional Current Doubler Rectifier. Przeglad Elektrotechniczny, Vol. 88, No. 8, 2012, Poland, pp. 124 129.

- [PAPER-VI] **Beldjajev, V**., Roasto, I., Zakis, J. Impact of Component Losses on the Efficiency of a New Quasi-Z-Source Based Dual Active Bridge. Doctoral school of Computing, Electrical and Industrial Systems DoCEIS 2013, IFIP AICT 394, Portugal, pp 485 492.

- [PAPER-VII] **Beldjajev, V**., Rang, T., Zakis, J. Steady State Analysis of the Commutating LC Filter Based Dual Active Bridge for the Isolation Stage of Power Electronic Transformer. 8<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2013), Ljubljana, Slovenia, June 05-07, 2013, pp. 138 143.

- [PAPER-VIII] **Beldjajev, V.**, Lehtla, T., Zakis, J. Impact of Component Losses on the Efficiency of the Commutating LC-Filter Based Dual Active Bridge for the Isolation Stage of the Power Electronic Transformer. 8<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2013), Ljubljana, Slovenia, June 05-07, 2013, pp. 132-137.

The copies of the publications are included in Appendix 1.

### Author's own contribution

This section describes the author's contribution to the papers included in the thesis.

- [PAPER-I] Viktor Beldjajev is the main author of the paper, responsible for the literature review and data collection. He had a major role in writing. He presented the paper at International Conference "Silovaja Elektronika i Energo-effektivnostj 2012 CEE'2012", Alushta, Ukraine.

- [PAPER-II] Viktor Beldjajev is the main author of the paper, responsible for the literature review and data collection. He had a major role in writing. He presented the paper at Riga Technical University 52nd International Conference, Riga, Latvia.

- [PAPER-III] Viktor Beldjajev is the main author of the paper, responsible for the literature review, data collection, performed calculations and modeling. He had a major role in writing. He presented the paper at 7<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2011), Tallinn, Estonia.

- [PAPER-IV] Viktor Beldjajev is the main author of the paper, responsible for the literature overview, data collection, calculations and modeling. He had a major role in writing.

- [PAPER-V] Viktor Beldjajev is the main author of the paper, responsible for the literature review, data collection, calculations and experimental measurements.

- [PAPER-VI] Viktor Beldjajev is the main author of the paper, responsible for the literature review, data collection, calculations and experimental measurements. He had a major role in writing. He presented the paper at the Doctoral School of Computing, Electrical and Industrial Systems DoCEIS 2013, Portugal.

- [PAPER-VII] Viktor Beldjajev is the main author of the paper, responsible for the literature review, data collection, calculations and modeling. He had a major role in writing. He presented the paper at 8<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2013), Ljubljana, Slovenia.

- [PAPER-VIII] Viktor Beldjajev is the main author of the paper, responsible for the literature review, data collection, calculations and modeling. He had a major role in writing. He presented the paper at 8<sup>th</sup> International Conference-Workshop Compatibility and Power Electronics (CPE2013), Ljubljana, Slovenia.

# 1 INTRODUCTION

# 1.1 Background

Modern trends in electrical energy technology are characterized by steadily growing need for renewable energy sources, energy storage, and smart grid technologies. Most widely utilized sources of renewable energy are photovoltaic energy, wind energy, tidal energy and hydrogen based fuel cell energy [1]. Continuous penetration of renewable energy sources into the distribution grid superimposes new challenges to the existing electric power transmission systems. This is due to the unpredictable nature of renewable energy resources in comparison with the conventional energy system, where the energy production and consumption can be predicted and scheduled with tolerable deviations. Conventional power system consists of large centralized generators, passive transformers, transmission lines, substations and consumers, whereas electrical energy flows uni-directionally from the generator's side to the consumers. Today's line frequency (50 Hz and 60 Hz) AC transmission systems use the magnetically coupled transformer concept for voltage elevation, transmission over long distances and voltage reduction for residential use. The traditional line frequency transformer (LFT) has simple construction, high efficiency and reliability and galvanic isolation. In addition, the LFT technology has proven itself during the era of industry. During the last decade, the basic construction of the LFT has remained the same, but the improved material technology allowed higher saturation densities and lower hysteresis losses to be achieved, resulting in very efficient transformers.

However, the growing number of renewable energy sources has resulted in a rising number of distributed power plants that are in principle subject to energy fluctuations. Therefore, it is essential to build energy storages (e.g. batteries, ultra capacitor banks, hydrogen buffer) to the distributed power plants to compensate the power demand during the low production periods (e.g. during the night for PV systems, silent wind periods for wind turbines). In addition, the consumers can supply energy to the grid by means of a local (e.g. roof mounted) power plant, regenerative braking of electrical drives and vehicle-to-grid systems. Thus, future power generation and distribution is likely to involve a substantial amount of the distributed renewable energy sources and micro grids. Many distributed generation (DG) sources cannot be connected directly to the AC systems, hence they require power electronic interface. To easily connect these new energy sources to the grid and improve the power quality by harmonic filtering, voltage sag correction, dynamic control of the power flow, a new power electronic transformer (PET) is required.

# Concept of the Power Electronic Transformer

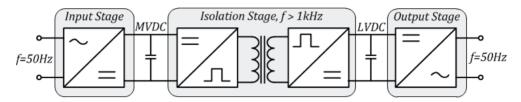

PET, also known as a solid state transformer or intelligent transformer, is a new type of transformer based on the power electronic converter that aims to better voltage regulation, power transmission, isolation and power quality

improvement of the grid. The basic idea behind the PET is to use medium frequency (f > 1 kHz) instead of low frequency in order to achieve considerably higher power density of the magnetic core and reduce its size. Moreover, the PET employs "active" control of the electrical energy by continuous monitoring and maintaining the desired network conditions. In comparison with the LFT, the PET has the following advantages:

- **Bi-directional power flow control:** The bi-directional power flow between the sources and the loads can be realized by utilizing the active front end topologies and the proper control of the active switches. In the electrical energy distribution system that incorporates renewable energy sources, storage devices and loads, the bi-directional power flow capability is one of the most important requirements for the PET.

- **Reduced mass and volumes**: As the power throughput density of the transformer is inversely proportional to the frequency, increasing the frequency allows better utilization of the steel magnetic core and reduction in transformer size allowing the high power densities to be achieved in the smaller cores. In comparison with the conventional LFT the size reduction up to three times is possible [2].

- Power quality: The control of the reactive power and power factor correction (PFC) has been stated to be one of the most important objectives of the PET. PFC circuits can be implemented on the MV and on the LV terminals that in turn make the additional capacitor banks for compensating reactive power unnecessary [3]. Moreover, the input and output ports of the PET are independent of each other, thus the quality of the output voltage is immune against the harmonics on the input side. The filtering is done by using the energy stored in the DC-link capacitors and active control [4].

- Protection against distortions: In order to achieve seamless operation of the network the adaptive control systems that can react on different fault conditions in the network are required. In the PET such voltage distortions like voltage sag, surge on the MV side are not reflected on the low voltage side of the transformer and vice versa. Such ride-through capability is achieved by the active control of the switches and presence of the storage elements (capacitors) in the DC-link of the PET.

- Environmental safety: The cooling mineral oil of the LFT poses a risk to the environment due to its toxic contents. The tendency is to avoid the oil in the cooling of the PET, instead the air-cooling can be successfully utilized. Thus the danger of oil pollution will be eliminated and the need for special oil-baths under the substations will be excluded.

- Smart grid ready: The PET is mainly aimed to operate first of all in the active distribution networks, where the "passive" control of the energy flow will be improved by adding innovative devices with sophisticated control features to the grid. The PET can be equipped with an advanced communication interface that includes smart metering, diagnostics, fault tracing, protection and distance control features. Advanced measurements are necessary for data acquisition to achieve a higher degree of the network

automation and more deterministic system control [5]. Such features would for example make the PET react on the LV side short circuit by turning off one phase or the whole device and also continue normal operation on the LV side in case of blackout on the MV side.

The PET can replace the LFT in the future active distribution networks (ADNs), such as smart-grid and microgrid, where the bi-directional power flow and flexible control functions are required. The list of the most important requirements that the PET has to correspond to is presented in [PAPER-I]. The ADN-s operate at the MV level, hence the PET must be adaptable to the existing voltage levels that can range from 0.4 kV to 35 kV worldwide. In addition, the efficiency of the PET must be comparable with the efficiency of the LFT. The US Department of Energy has released the standard for liquid and dry type distribution transformers, effective since 2010 [6]. The standard defines the minimum efficiency of the LFT to be higher than 97 % irrespective of the power rating, however, the standard value approaches 99.5 % for most liquid-immersed power transformers. According to the literature the target efficiency for the PET is 96...98 % depending on the power rating [7].

#### PET in Future Active Distribution Networks

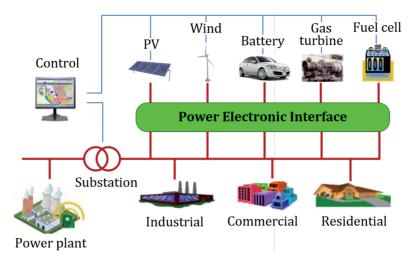

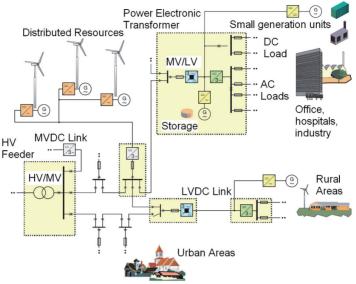

The aim of the ADN-s is to provide a flexible infrastructure allowing novel distribution and transmission networks to withstand demands that will be placed on them by penetration of the novel generation types, increasing energy demand, harnessing the renewable energy potential and supporting the low-carbon energy systems in an environmentally acceptable manner [5]. A schematic of a semi-autonomous ADN that can separate itself from the main grid and operate in islanding mode is shown in Figure 1.1. In comparison with the traditional passive networks that have limited control of the parameters, low penetration of the renewables and poor monitoring, the ADN-s are aimed to have sophisticated control of power quality and power flow direction between the power plants, loads and DG-s attached to the distribution level, with continuous network condition monitoring. The ADN-s consist of the national grid, distributed power generating units and different loads that are interconnected into one system.

The role of the PET in such systems is to act as an interface between the power grid and loads. It can be regarded as an energy router [8], [9] that can supply the energy during the power down of the main grid (islanding mode) or compensate the power during the higher demand periods. An additional storage that is attached to the PET reduces the influence of the unpredictable power generation on the grid. In such a way, the consumers are protected against the disturbances in the power grid and at the same time the reactive power generated by the loads would not penetrate into the power grid [1]. As a result the operation of the distribution system would be more stable and efficient.

Figure 1.1. A schematic of a semi-autonomous ADN.

### Challenges of the Isolation Stage

The topologies of the PET can be classified according to the number of power conversion stages (see chapter 2.1). The three-stage topology, where the isolation stage represents a high frequency isolated DC/DC converter, is the most advantageous among others. The isolation stage provides the voltage conversion and galvanic isolation between the MV and LV ports. The isolation stage can be divided into two logical entities on the MV and on the LV ports of the transformer, which can be seen as power electronic building blocks (PEBB). The PEBB is a standardized module that allows rapid configuration of power converters to meet specific customer needs, including: AC-DC conversion, DC-AC conversion, frequency changers and/or DC-DC voltage changers [10].

Due to the presence of the transformer, the isolation stage has great impact on the weight and the volumes of the PET and eventually on the whole distribution system. In order to achieve high power density (and significant mass reduction compared with the LFT), semiconductors must have the ability to be switched under high switching frequency while maintaining reliable operation under high voltage and high current conditions. The efficiency of the isolation stage depends on the losses in the components. Most crucial of the losses are the conduction, switching and core losses. Research in [1], [11] focused on the analysis of the conduction, the switching and the core losses in the different parts of the PET. According to the research in [11], the losses in the two-level rectifier based isolation stage can comprise 68 % of the total losses

It can be concluded that the isolation stage will determine the volumes and efficiency of the PET and will play a key role in the power conversion. Thus, investigation of the isolation stage and improvement of the power conversion characteristics are very important and challenging tasks. By investigating the new topologies, such features like the losses, current and voltage stress, the

dynamic behavior and flexibility of the isolation stage can improve the bottlenecks of the existing DC/DC converters. The investigation and development of the DC/DC converter topologies for the performance optimization is the major task of the thesis.

# 1.2 Main Hypotheses and Objectives of the Thesis

The PET presents a new type of transformer that is based on power electronics. It provides a flexible alternative for the traditional LFT in the future ADN-s, where it acts as an energy router. However, the technology faces numerous challenges that need to be solved before the PET can be integrated into the future ADN. The main purpose of the research is to locate the challenges of the commonly used DC/DC converters and synthesize new medium-frequency isolated DC/DC converter topologies for the isolation stage of the PET. The topologies are to be analyzed mathematically and validated with simulations and experiments.

# The Main Hypothesis of the Research

A three-stage topology is considered to be one of the most advantageous topologies for the power electronic transformer. The isolation stage of the three-stage topology is the most critical part of the power electronic transformer considering the wide voltage and power regulation capabilities and the efficiency. By adding new power electronic building blocks to the isolation stage, the power and voltage regulation ranges can be extended. Moreover, the voltage and current stress on the components can be reduced.

# The Main Objectives of the Thesis

- to analyze and classify the current state-of-the-art technologies and development trends of the power electronic transformer concept;

- to analyze the current state-of-the-art technologies and development trends of the isolated bi-directional high frequency DC/DC converters;

- to identify weaknesses of conventional topologies of the isolation stage and propose new power electronic building blocks for the LV side of the isolation stage;

- to perform the comparative analysis between the traditional approach and the proposed power electronic building blocks;

- to define directions for the future research based on the challenges obtained from the comparative analysis.

#### 1.3 Contribution of the Thesis and Dissemination

The doctoral thesis is based on the 8 published articles and conference papers composed by the author of the thesis. The study was carried out during the years 2009 – 2013 at Tallinn University of Technology in Tallinn, Estonia. The study was a part of the following projects: Optimal energy conversion and control in smart and microgrids, Intelligent Transformer – Analysis of Operating Modes

(ETF8687), New Converter Topologies and Control Methods for Electronic Power Distribution Networks (SF0140016s11). The originality of the thesis lies in the scientific and practical novelties described further.

# Scientific Novelty

Scientific novelty of the doctoral thesis includes:

- classification and analysis of the current state-of-the-art technologies and development trends of the power electronic transformer and bi-directional isolated high frequency DC/DC converters;

- proposal of new power electronic building blocks, such as a current doubler rectifier with bi-directional power flow capability, a quasi-Z source inverter and a current-fed DC/DC converter with an active clamp, for the isolation stage of the power electronic transformer;

- derivation of the mathematical models and assessment of the component losses on the efficiency of the proposed power electronic building blocks.

#### **Practical Novelty**

The practical novelty of the doctoral thesis includes:

- improved modulation method for the qZSI and current-fed DC/DC converter with an active clamp to increase the voltage and power regulation range;

- experimental investigation of the proposed power electronic building blocks regarding their impact on the component voltage and current stresses;

- design guidelines for the proposed PEBB-s.

# Dissemination of the Results

The results of the doctoral thesis have been presented by the author at 11 international conferences. The author has published 10 international scientific papers directly associated with the thesis. Three of them are available in the *IEEE* database and two have been published in the international peer-reviewed journals.

# 2 TECHNOLOGICAL OVERVIEW

# 2.1 Topologies of the PET

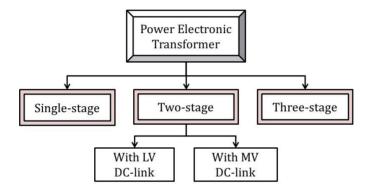

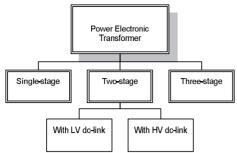

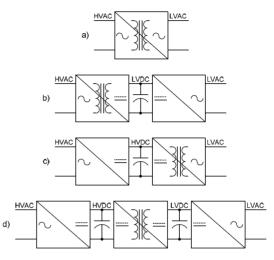

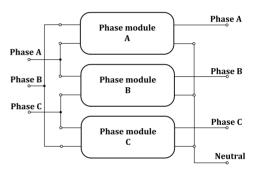

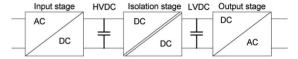

A technological overview of the topologies for the PET and their classification is presented in [PAPER-I] and [PAPER-II]. Numerous topologies for the PET have been proposed by different authors. However, many of the proposed topologies do not support the bi-directional power flow that is a major requirement for the PET in the ADN. Other important requirements comprise galvanic isolation and capability of interconnecting renewable energy sources and energy storage devices. The PET topologies can be classified according to the number of power conversion stages [12], [13] as depicted in Figure 2.1.

Figure 2.1. Classification of the PET topologies based on the number of stages.

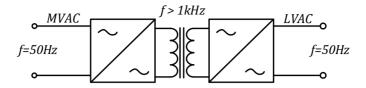

Single-stage PET structure comprises direct AC-AC conversion from low voltage (LV) AC to medium voltage (MV) AC and vice versa [14]. The block diagram of a single stage topology of the PET is shown in Figure 2.2. Typically, such topologies are based on different matrix converter [15]-[17] and cycloconverter [18] topologies. Although this is the most straightforward approach to AC-AC power conversion, including such benefits as low weight and low cost, it is problematic, since each switch must be able to block full primary voltage and also be capable of conducting full secondary current [19]. Lack of the DC-link in the single stage topologies is a major drawback because integration of the storage elements and power factor correction circuit require additional devices that will result in increased complexity, size and cost of the system. In addition, this single-stage topology is sensitive to the distortions, since disturbances on one side of the converter may also reflect to the other side [2].

Figure 2.2. Single-stage topology of the PET.

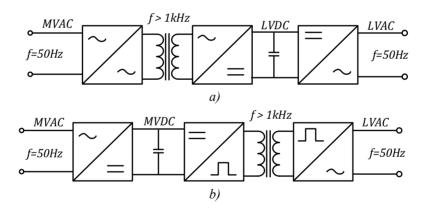

The two-stage topologies can be subdivided into topologies with LV DC-link [20] - [23] and MV DC-link [24], [25] as shown in Figure 2.3. Here the low frequency AC is directly converted to the high frequency AC and rectified back to DC on the transformer secondary. Then it is converted to 50 Hz output voltage using a PWM inverter. The switches on the AC-AC side must be four-quadrant to withstand bi-polar voltages and currents. This topology has some notable disadvantages. First, the reactive power compensation feature in the two-stage topology with LV DC-link is complicated on the MV side and requires additional circuitry that results in a higher cost. Moreover, the energy sources cannot be connected directly to the PET due to lack of the MV DC-link. Second, the two-stage topology with MV DC-link lacks the possibility of interconnecting the storage elements directly to the PET.

Figure 2.3. Two stage topologies of PET: a) with LV DC-link; b) with MV DC-link.

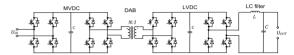

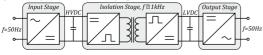

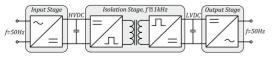

The three-stage topology is the most preferred and investigated PET topology today, since various converter topologies can be chosen for the different power conversion stages that give a wide playground for the performance optimization of the PET [1], [12], [19], [26] - [35]. The three-stage topology of the PET is shown in Figure 2.4. It consists of three power conversion stages: the input stage, the isolation stage and the output stage. The input stage is an active front end rectifier that rectifies the MV AC to the MV DC voltage. In the isolation stage the DC-DC conversion takes place by converting MV DC voltage into high frequency square-wave AC voltage and is transferred to the MF

transformer, where the voltage level is reduced and rectified again on the LV DC side, forming this way a LV DC-link. Finally, the LV DC is converted back to 50 Hz AC voltage by means of the inverter in the output stage. The three-stage PET topology has a bi-directional power flow capability, thus the power can be transferred from the LV port towards the MV port.

Figure 2.4. Three-stage topology of the PET.

Presence of two different voltage level DC-links allows interconnecting the energy storage devices and the renewable energy sources into one system. Integration of power-factor-correction, sag compensation and isolated DC-DC converters can decrease the losses and consequently improve the efficiency. For these reasons, the three-stage topology seems to be the most advantageous among the other topologies. Though, a high switch count is the major drawback of this topology due to increased conduction and switching losses. However, the losses can be reduced by use of the new-generation *SiC* or *GaN* based switches and different control techniques that enable the zero voltage switching (ZVS) and/or zero current switching (ZCS) to be achieved.

# 2.2 Topologies for the Isolation Stage

In order to meet the demands of medium voltage and high power capability for the distribution network, two different trends can be seen in the industry and power electronics communities. One way is development of the new semiconductors with higher nominal voltage and current ratings and their integration into existing two-level converter topologies using the series/parallel connections. Second is the development of the new multi-level converter topologies by using the conventional semiconductors [36] - [38].

Series connection of the power switches with high voltage and current ratings can inherit the benefits of well-known control methods. However, these devices are more expensive and they still do not meet the voltage rating requirements set by the future distribution systems. The research in [38] showed that series connection of the MOSFETs and IGBTs may result in unsymmetrical voltage sharing between the switches due to unequal parameters of the switches (leakage current, switching delays, collector-to-emitter capacitance). Therefore additional methods for voltage-balancing are needed to prevent the failures caused by the transients and static phases. The failure in one element will cause a failure of the entire converter that will result in low reliability [39].

# Multi-level MV DC/DC topologies

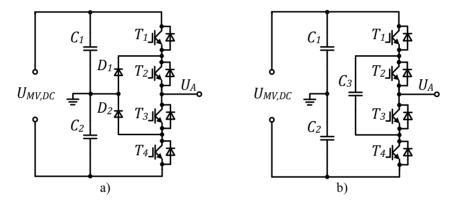

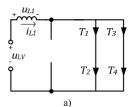

The MV multi-level DC/DC converters use conventional power switches but have a complex structure and control in comparison with the two level converters. They consist of arrays of power switches, diodes and capacitive voltage sources. Correct combination allows the multi-level voltage waveforms to be generated, while maintaining the equal voltage sharing between the switches [39]. Thus a multi-level converter topology is suitable for the MV side to clamp the voltage across each switch that in turn reduces the required switch blocking voltage. Among several multi-level configurations the cascaded, diode clamped and flying capacitors are best known [39] - [44]. The proposed three-level topologies are shown in Figure 2.5. The key components of the diode clamped three-level converter are the diodes  $D_1$  and  $D_2$  that are used to clamp the voltage across each switch to only half the DC bus voltage. The flying capacitor converter works in a similar way as the diode clamped converter, however the voltage across the switches is clamped by clamping capacitor  $C_3$ .

Figure 2.5. Multi-level topologies for the MV side of the isolation stage: a) diode clamped converter; b) capacitor clamped converter.

The multi-level topology combines some serious disadvantages like increased number of components, decreased long-term reliability, increased complexity of control and protection circuits, increased dimensions and weight of the converter [45]. As the reliability is one of the most critical requirements for the PET, the cascaded two-level converter design seems to be a more optimal solution for the PET in comparison with the multi-level converter topologies.

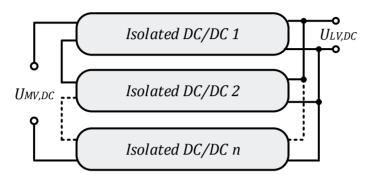

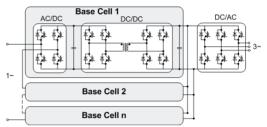

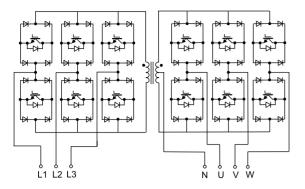

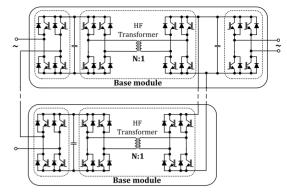

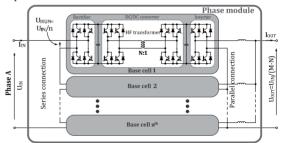

## Modular structure based DC/DC converters

The modular structure based DC/DC converters are composed of well-known topologies and available semiconductors. They usually consist of the series connection of the converter cells on the MV side and parallel connection on the LV side as shown in Figure 2.6. The series connection on the MV side allows the voltage to be shared between the switches. Parallel connection on the LV side allows high current to be shared between the switches. As can be seen, each cell handles only part of the total input power. That in turn allows to select the

power switches with lower voltage ratings and thus lower conduction losses and also increase the switching frequency [39], [46]. Lower losses improve the overall efficiency of the converter while increased switching frequency allows the volumes of the MF transformer core to be reduced. Due to higher efficiency, reduced volumes, mass and eventually cost, such type of converters are the optimal for the PET.

Figure 2.6. Block diagram of the modular series-input-parallel-output design.

# Topologies for the Modular Design Based DC/DC Converters

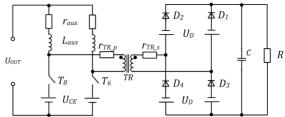

Numerous isolated DC/DC converter topologies have been proposed by different authors [47] - [54], however many of them lack the bi-directional power flow and ZVS capabilities. Among them the phase-shifted dual active half bridge (DHB) and dual active bridge (DAB) meet most of the requirements of the PET concerning the bi-directional power flow and ZVS capabilities, thus making them interesting research objects. Compared to the traditional hard-switched PWM converters, the phase-shift-controlled converters usually have higher circulating current and higher conduction losses. However, as the switching frequency increases, the loss reduction caused by soft-switching overweighs the conduction losses and thus the overall efficiency improves.

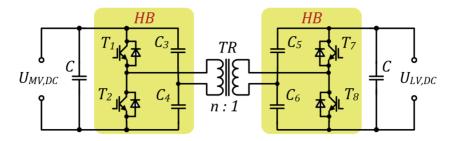

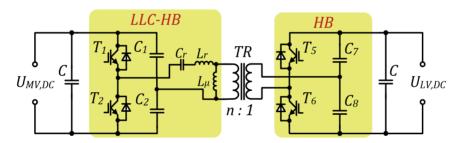

A DHB is a widely used converter in the high power applications. For the isolation stage of the PET it was proposed in [39], [55]. The circuit of the DHB shown in Figure 2.7 consists of the two half-bridges (HB) that are connected by means of the HF transformer. Besides small number of the switching devices, simple power stage design and simple control system, a small core loss of the transformer can be achieved. In addition, the DHB results in a more economical implementation than the FB based DC/DC converters. However, the splitting capacitors have to carry all transformer currents and capacitors with higher VA rating are required. Moreover, the total switch conduction losses in the DHB can be twice as high as in the DAB for the same power level due to the higher magnitudes of current (almost double) through the switches [39].

Figure 2.7. Schematic of the dual half bridge circuit.

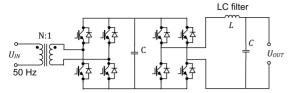

In [57] the 1.2 MW PET for the traction applications with single phase 15 kV input and 1.5 kV DC output voltages is presented. The isolation stage of the given PET consists of the half bridge LLC isolated resonant circuit topology and a MF transformer as shown in Figure 2.8. By involvement of the magnetizing inductance and the leakage inductance of the MF transformer, the LLC circuit allows the zero voltage turn-on and effective turn-off (with significantly smaller current) of the 6.5kV IGBTs to be achieved.

Figure 2.8. Schematic of a half-bridge LLC DC/DC converter topology used in the PET of the traction system.

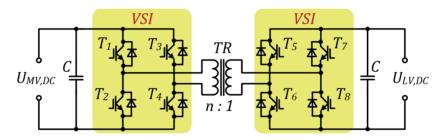

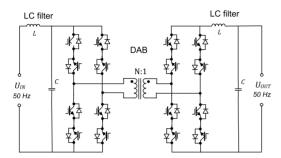

The most widely proposed topology for the future MV DC-DC converters is the DAB [59] - [64]. A DAB based PET prototypes have already been built for 7.2/0.24 kV and 20 kVA power ratings [65], [66]. Some advantages of the DAB converter are: voltage stress across each switch is limited by the DC bus voltage level, ZVS can be achieved without additional circuitry, simple structure of the transformer, fast dynamic behavior due to lack of passive components, and various possible control algorithms [39]. For these reasons the DAB is selected as a reference topology for the further investigations.

### **Dual Active Bridge**

The circuit of the DAB is shown in the Figure 2.9. It consists of two simultaneously controlled voltage source inverters (VSI) and a HF transformer between them. For proper output power control, the DAB requires a relatively large series inductor  $L_{TR}$ , in order to create voltage difference between the voltages on the LV and MV sides of the transformer. As the PET is aimed to be

used in HP and MV applications, the natural stray inductance of the HP transformers is typically sufficient [68].

Research in [68] has analyzed three different modulation methods for the DAB: i) rectangular modulation mode, with duty cycles D=0.5 ii) triangular current mode, iii) trapezoidal current mode. Triangular modulation allows the lowest switching losses to be achieved. Trapezoidal modulation allows higher power to be transferred in comparison with the triangular modulation [68], [69]. With rectangular modulation the highest power transfer can be achieved, thus the rectangular modulation method was selected as a control method of the DAB for the further investigations.

With rectangular modulation method, the magnitude and the direction of power can be controlled by means of the phase shift angle  $\varphi$  between the gate signals of both VSI-s. The value of the phase angle determines the magnitude of the transferred power, whereas the sign of the phase angle determines the power flow direction. In addition, the phase shift technique allows ZVS to be effectively achieved over a wide load range, reducing this way the switching losses. However, using the large phase shift values can result in a high reactive power content that in turn reduces the efficiency of the converter. In [68] the dependency between the phase angle, the active and reactive power is shown. The suggested control range of the phase angle varies between 45°...60° [70]. The gate signals, typical waveforms and operation description of the DAB are presented in [PAPER-VI] and [PAPER-VII].

Figure 2.9. Schematic of the DAB.

The power delivered from one port to the other can be determined by knowing the transformer turn's ratio  $N_{TR}$ , the voltages on MV and LV side,  $U_{MV}$  and  $U_{LV}$  respectively, switching frequency  $f_S$  and the leakage inductance of the transformer  $L_{TR}$ , in the following way:

$$P = \frac{N_{TR}U_{MV}U_{LV}D_{\varphi}(1 - |D_{\varphi}|)}{2f_{S}L_{TR}}, -1 \le D_{\varphi} \le 1,$$

(2.1)

where  $D_{\varphi}$  is the duration of the phase shift  $t_{\varphi}$  between the gate signals of the corresponding legs of the DAB. The best performance of the DAB is achieved when the voltage on the transformer LV side and the reflected MV side voltages are equal.

$$U_{LV} = N_{TR} \cdot U_{MV}. \tag{2.2}$$

In such case the current stress on the devices is minimal and soft switching can be effectively achieved that results in higher efficiency and reduced component ratings. However, the DAB lacks the voltage boost properties and under realistic conditions the voltages variations on MV and especially on LV cannot be compensated. That in turn results in increased transformer  $I_{TR}$  and the capacitor  $I_{CI}$ ,  $I_{C2}$  RMS currents and lower efficiency [60]. These factors have been a serious drawback of the DAB that could be solved by introducing new PEBB-s for the LV side of the DAB.

# 2.3 Summary

The three-stage topology of the PET is the most advantageous among the single and the two-stage topologies. That is due to the presence of two DC-links with different voltage levels that allow the energy sources and storage devices to be interconnected into one system and power factor correction circuits to be integrated on the MV and LV side. In order for switches to operate on the MV side, the voltage stress on the switches must be reduced by employing the multilevel converter topologies, connecting the switches in series or using the modular design of the converter cells, where total input power is shared between different cells. The DHB and DAB are widely used two port topologies that can be connected into a modular structure to reduce the component ratings. The advantages of the DAB for HP applications overweight the DHB. The phase shift modulation allows to control the power range of the DAB in a wide range in both directions. However, the DAB lacks the voltage regulation capabilities that results in increased component stress values under varying LV side voltage level. These problems can be solved by introducing the new PEBBs for the isolation stage of the PET.

# 3 NEW POWER ELECTRONIC BUILDING BLOCKS FOR THE ISOLATION STAGE

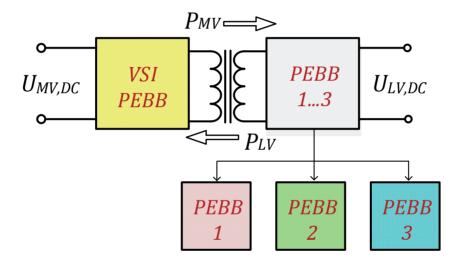

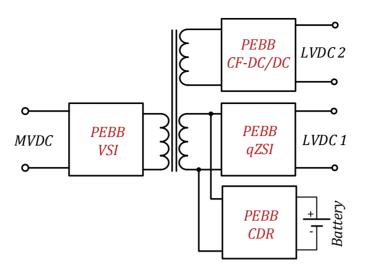

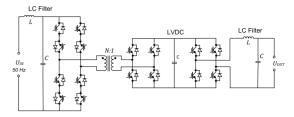

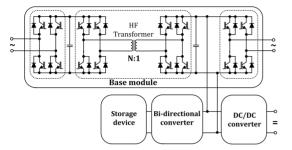

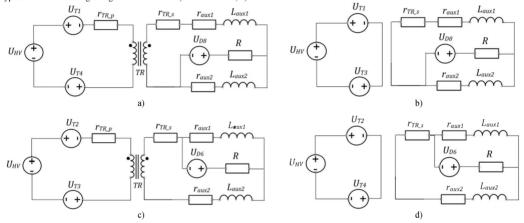

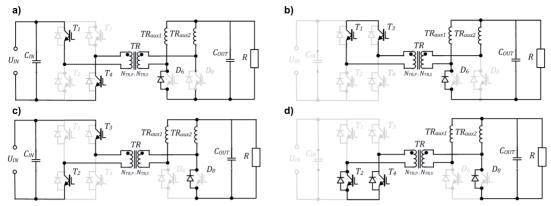

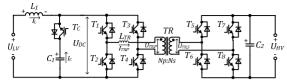

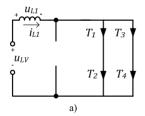

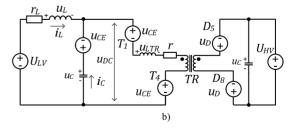

Previous chapter reviewed technologies suitable for DC/DC converters for the isolation stage of the three-stage PET. It turned out, that a major drawback of the DAB is lack of voltage compensation capabilities. This chapter focuses on the elimination of this problem. The isolation stage of the PET can be represented by the PEBB-s, as shown in Figure 3.1. The MV side converter consists of the traditional voltage source inverter (VSI) PEBB. Three new PEBB-s for the LV side of the isolation stage are proposed in this section.

Figure 3.1. Representation of the isolation stage by using the PEBB-s.

The most important requirements for the isolation stage are the bi-directional power flow control and galvanic isolation by means of the MF transformer. The new PEBB-s should have improved shoot-through immunity, reduced current and voltage stress on the components and fairly good efficiency in comparison with the conventional VSI. Following new PEBB-s are proposed for the LV side of the isolation stage:

- CDR PEBB: current doubler rectifier (CDR) with bi-directional power flow capability;

- qZSI PEBB: quasi-Z-source inverter (qZSI);

- CF-DC/DC PEBB: current-fed DC/DC converter with an active clamp.

The isolation stage with the proposed PEBB-s allows the power to be transferred in two directions, in the forward and in the reverse operating mode. In the forward operating mode, the energy is transferred from the MV port

towards the LV port. In the reverse operating mode, the energy is transferred from the LV port towards the MV port.

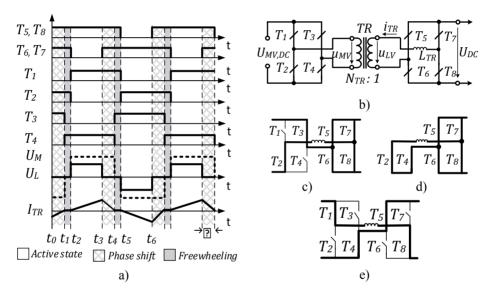

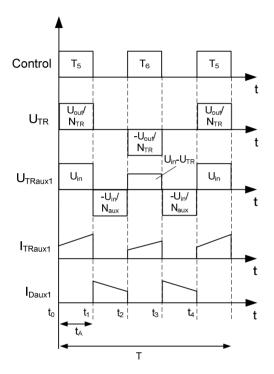

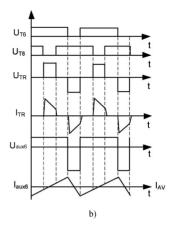

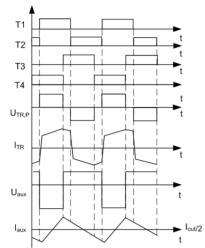

# 3.1 Improved Modulation Method

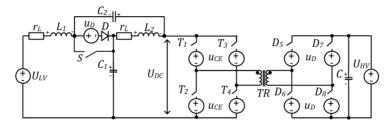

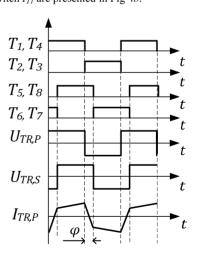

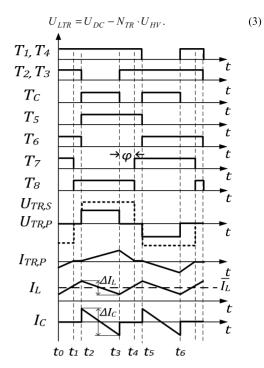

In order to perform comprehensive comparison between the DAB and the proposed PEBB-s the modulation method must provide simultaneous control of the switches on both sides of the transformer. The conventional rectangular modulation can be used in the forward operating mode, however in the reverse operating mode, if voltage regulation is necessary, the improved modulation method (IMM) is used to control the voltage and power level simultaneously [60]. The typical waveforms of the IMM are shown in Figure 3.2a, and the equivalent circuit in Figure 3.2b.

Figure 3.2. Improved modulation method. a) typical waveforms; b) schematic of the circuit; c) phase shift state; d) freewheeling state; e) active state.

The IMM consists of three switching states: active state, phase shift state and the freewheeling state. During the time interval  $t_0...t_1$  the current in the MF transformer is reversed and adjusted to the new level. The equivalent circuit of this switching state is shown in Figure 3.2c. The rising slope of the transformer current  $I_{TR}$  can be expressed as follows:

$$\Delta i_{TR} = i_{TR,0} + \frac{u_{MV} N_{TR}}{L_{TR}} \cdot \Delta t, t_0 \le t \le t_1,$$

(3.1)

where  $i_{TR,0}$  is the initial transformer current value at time instance  $t_0$  and  $L_{TR}$  designates the leakage inductance of the MF transformer. During the freewheeling time interval  $t_1...t_2$  current slope of the  $i_{TR}$  remains constant. The equivalent circuit of the freewheeling state is shown in Figure 3.2d. During the

active state  $t_2...t_3$  the energy is transferred from the LV port towards the MV port of the MF transformer. The equivalent circuit of the active state is shown in Figure 3.2e and the slope of the current can be determined as follows:

$$\Delta i_{TR} = \frac{U_{LV} - U_{MV} N_{TR}}{L_{TP}} \cdot \Delta t, t_2 \le t \le t_3.$$

(3.2)

The next half switching cycle is symmetrical to the first one. According to a detailed analysis, presented in [PAPER-VII], knowing the switching frequency  $f_S$ , the voltages on the MV and the LV ports and considering the leakage inductance of the transformer  $L_{TR}$ , the transferred power from the LV port to the MV port can be expressed in the following way:

$$P = U_{LV} \cdot \frac{(2N_{TR}U_{MV} - U_{LV})D_{\varphi}(1 - D_S)}{4f_S L_{TR}}, 0 \le D_{\varphi} \le D_S,$$

(3.3)

where  $D_{\varphi}$  is the relative duration of the phase-shift and  $D_S$  designates the relative duration of the shoot-through state. As can be seen, the transferred power is a function of  $D_S$  and  $D_{\varphi}$ , that extends the voltage and power regulation possibilities comparison with conventional rectangular modulation of the DAB. However, the IMM has limited phase angle control range that should be limited to  $D_S$ . Increasing  $D_{\varphi}$  over  $D_S$  results in increased component stress and reduced voltage step-up capability.

The following chapters present the proposed PEBB-s, describe their operating principle, their advantages and disadvantages, and recommendations for design.

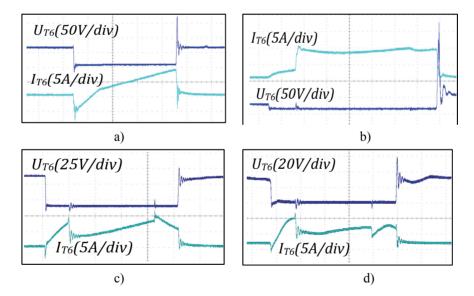

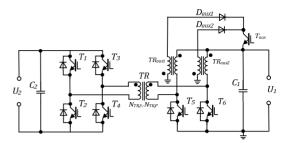

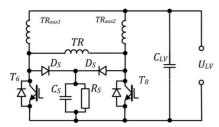

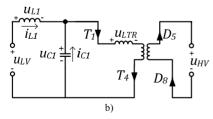

# 3.2 Current Doubler Rectifier with Bi-directional Power Flow Capability PEBB

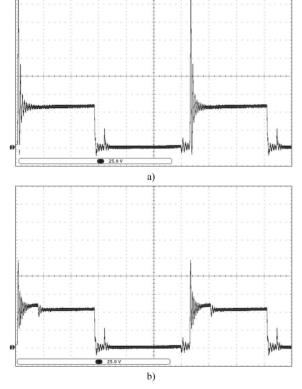

The proposed current doubler rectifier (CDR) PEBB is introduced in [PAPER-III]. The paper describes the operating principle of the converter and presents its typical waveforms. In addition, the paper provides a steady state analysis with the boost factor estimation and the simulation results. The experimental results for the CDR PEBB are presented in [PAPER-V].

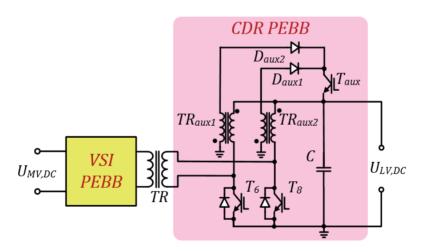

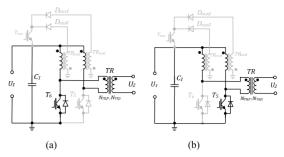

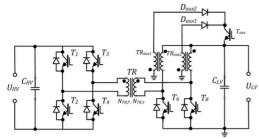

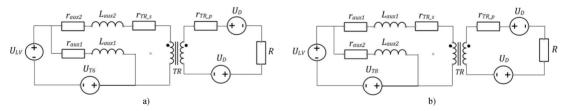

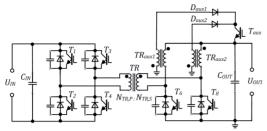

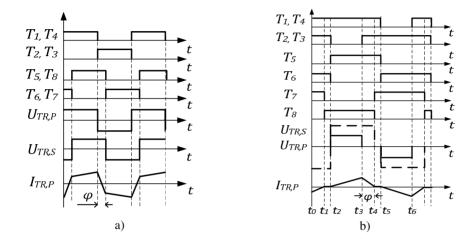

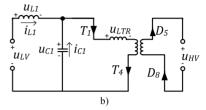

A combination of a CDR PEBB and a VSI PEBB results in a topology called CDR-based DAB. A schematic of such combination is shown in Figure 3.3. It consists of the conventional CDR circuit, where the diodes are replaced with controllable switches  $T_6$  and  $T_8$ , and inductors are replaced with the transformers  $TR_{aux1}$  and  $TR_{aux2}$ . An auxiliary circuit is attached to the CDR in order to provide freewheeling path for the energy stored in the auxiliary transformers  $TR_{aux1}$  and  $TR_{aux2}$ , and mitigate the occurrence of the overvoltage peaks on the switches when operating with the duty cycle  $D_A \le 0.5$ .

The operating principle of the converter in the forward and the reverse operating modes is described in [PAPER-IV]. When the converter operates in the forward operating mode, the MV side VSI PEBB generates rectangular voltage over the MV side winding of the transformer and the current flows

through the antiparallel diodes of  $T_6$  and  $T_8$  on the LV side. In the reverse operating mode the switches  $T_6$  and  $T_8$  on the LV side are controlled alternately to provide the necessary voltage step-up and power flow to the MV port. In the normal operating mode the switches  $T_6$  and  $T_8$  are controlled with the duty cycle D > 0.5 and the boost factor b equals to:

$$b = \frac{u_{MV}}{u_{LV}} = \frac{1}{1 - D_A} \cdot N_{TR} \,, \tag{3.4}$$

where  $D_A$  is the duty cycle of the gate signals for  $T_6$  and  $T_8$ , and  $N_{TR}$  is the turn's ratio of the MF transformer. The switches on the MV side VSI are controlled according to IMM. If the duty cycle of the switches  $T_6$  and  $T_8$  becomes  $D_A \leq 0.5$  the path of the transformer's leakage energy gets interrupted. That results in dangerous overvoltage spikes over the switches. Therefore, this energy is redirected back to the LV port by means of the freewheeling path, provided by the auxiliary circuit. A boost factor in that operating mode can be determined as follows:

$$b = \frac{u_{MV}}{u_{LV}} = \frac{N_{TR}}{N_{aux}} \left( 2N_{aux} - \frac{1 - 2D_A}{D_A} \right), \tag{3.5}$$

where  $N_{aux}$  is the turn's ratio of the auxiliary transformers  $TR_{aux1}$  and  $TR_{aux2}$ .

Figure 3.3. Schematic of the CDR PEBB.

The advantages of the CDR PEBB are: i) reduced current ripple, ii) voltage step-up in the reverse operating mode, iii) ZV turn-on can be achieved, iv) improved hoot-through immunity on the LV side, v) simple gate driver design, vi) reduced number of active switches. The major drawbacks of CDR PEBB are: i) increased mass and volumes due to the presence of three transformers, ii) increased voltage stress on the LV side switches, iii) different boost factors in the forward and in the reverse operating modes.

# Design considerations for the $D_A > 0.5$

Next, some design guidelines for the CDR PEBB in the reverse operating mode are presented. First of all, the necessary inductance of the auxiliary transformer's should be obtained since it determines the slope and the peak value of the current. Due to the current sharing effect of the CDR PEBB each auxiliary transformer carries half of the input current, thus the average current can be obtained as follows:

$$I_{aux,AV} = \frac{P_{LV}}{2 \cdot U_{LV}}. (3.6)$$

Inductance of the auxiliary transformer depends on the allowed current ripple  $\Delta I_L$  value. The current through the auxiliary transformer reaches its maximal value at the end of the duty cycle  $D_A$ . Thus, considering the maximum duty cycle  $D_{A,MAX}$  and the switching frequency  $f_S$ , the inductance can be determined according to 3.7

$$L_{aux} = \frac{2 \cdot U_{LV}^2 \cdot D_{A,MAX}}{P_{LV} \cdot f_S \cdot k_L},$$

(3.7)

where  $k_I$  represents the ratio of the current ripple and the average current  $\Delta I/I_{aux,AV}$ . When designing the converter for the bi-directional operating mode, it should be kept in mind that in the forward mode, too low inductance of the auxiliary transformer can bring the converter into the discontinuous conduction mode.

Next, the selection of the filter capacitance is considered. If the CDR-DAB operates in the boost mode, the current ripple is typically very low, thus the LV side capacitor should be dimensioned first of all according to the requirements set in the forward operating mode. If the converter operates in the forward operating mode, the capacitor selection is based on the allowed current on voltage ripples on the LV side and can be selected according to 3.8 as follows:

$$C = \frac{\Delta I}{\Delta U \cdot 2 \cdot f_S},\tag{3.8}$$

where  $\Delta I$  is the current ripple,  $\Delta U$  is the voltage ripple and  $f_S$  is the switching frequency. It is advisable to use not more than 1 % voltage ripple during the design. In order to achieve more efficient current ripple cancellation, a capacitor with as small ESR as possible is advisable to be employed.

#### Transformer turn's ratio

Next, the selection of transformer turns ratio is considered. Different parameters are needed to be considered when designing the MF transformer for the CDR circuit. These are the maximal flux density  $B_{MAX}$  (derived from the saturation flux), core area  $A_e$ , switching frequency and converter features. The number of turns on the LV side can be obtained according to 3.9

$$N_{LV} = \frac{U_{LV}}{(1 - D_A) \cdot B_{MAX} \cdot A_e \cdot f_S} . \tag{3.9}$$

The number of turns on the MV side of the transformer can be obtained according to 3.10 as follows:

$$N_{MV} = \frac{U_{MV} \cdot (1 - D_A) \cdot N_{LV}}{U_{LV}}.$$

(3.10)

It should be noted, that if the current doubler is phase-shift controlled the effect of the leakage inductance should be carefully considered, as it is needed for the power transfer. If necessary, the number of turns can be made higher than the ones obtained by 3.9 and 3.10, in order to achieve necessary value of the leakage inductance.

#### Power switches

In order to dimension the power switches, the voltage and current stress values should be determined. Neglecting the voltage spikes that occur during the switching transients, the steady-state voltage stress on the switches  $T_6$  and  $T_8$  can be estimated according to 3.11 in the following way:

$$U_{T6,MAX} = \frac{U_{LV}}{1 - D_{AMAX}}. (3.11)$$

As can be seen, at high  $D_A$  values the steady state voltage stress on the switches can be enormous, e.g. for  $D_A = 0.8$  a voltage stress 500 % of  $U_{LV}$  is applied on the switches. The experimental investigations have determined that high overvoltage peaks occur over the switches during the turn-off, thus the rating of the switches must be even higher. The peak current through the switch  $T_6$  occurs when  $I_{L8}$  reaches its maximum level, at the end of the duty cycle  $D_{A,MAX}$ . Average current through the switch is half the input current

$$I_{T6,AV} = \frac{1}{2} \cdot I_{LV} \,. \tag{3.12}$$

The peak current through the switch can be obtained according to 3.13

$$I_{T6,MAX} = \frac{U_{LV}}{L_{vir} \cdot f_s} \cdot \left(\frac{1 + D_{A,MAX}}{2}\right).$$

(3.13)

When designing the bi-directional CDR, the voltage and current stress values should be considered for both power flow directions. On the LV side the switches with high current rating are feasible. The IGBT-s have lower conduction losses at high current values in comparison with MOSFETs. However, a disadvantage of the IGBT-s is high turn-off losses. Moreover, with the rise of the switching frequency the switching losses of the IGBT-s significantly overweigh the losses in MOSFET-s.

#### Snubber

The experimental results revealed the problems regarding high overvoltage peaks over the switches in the reverse operating mode of the CDR PEBB. Such feature drastically increases the voltage stress on the switches, increases the turn-off losses and significantly limits the use of this topology in HP applications. However, the overvoltage peaks can be clamped by adding a special diode-capacitor-resistor (RCD) snubber into the circuit, as is shown in section V of [PAPER-IV]. The aim of such snubber is to discharge the energy stored in the leakage inductance of the MF transformer during the turn-off. The design guidelines for calculating the RCD snubber are presented in [77] - [79] and can be used for the RCD snubber design for the CDR PEBB.

# Auxiliary circuit

The aim of the auxiliary circuit is to provide a freewheeling path for the energy that is stored in the auxiliary transformers and direct it back to the LV port of the converter. This is needed to prevent the overvoltage peaks on the switches if the duty cycle is  $D_A \le 0.5$ . The auxiliary circuit consists of the auxiliary transformers  $TR_{aux1}$  and  $TR_{aux2}$ , diodes  $D_{aux1}$  and  $D_{aux2}$ , and one switch  $T_{aux}$ . In order to select the turn's ratio of the auxiliary transformers  $N_{aux}$ , it should be remembered that it has direct impact on the boost factor of the converter, on the average current and blocking voltage of the auxiliary diodes  $D_{aux1}$ ,  $D_{aux2}$ . The maximum blocking voltage of the auxiliary diodes can be obtained as follows

$$U_{D,REVMAX} = U_{LV} \cdot (1 + N_{aux}),$$

(3.14)

where  $N_{aux}$  designates the turn's ratio of the secondary side and the primary side of the auxiliary transformers. As can be seen, increased turn's ratio of the auxiliary transformer, increases the needed blocking voltage of the diodes. Hence, the turn's ratio of the auxiliary transformers should be taken into account when selecting the appropriate diodes. The average current through the auxiliary diode can be approximately estimated in the following way:

$$I_{D,AV} = I_{LV} \cdot N_{aux} (1 - 2D_A)$$

(3.15)

The maximum steady-state voltage on the switch  $T_6$  and  $T_8$  can be evaluated as follows:

$$U_{T6,MAX} = U_{LV} \cdot \frac{(1 + N_{aux})}{N_{aux}}.$$

(3.16)

As can be seen from 3.14 and 3.16, increasing the  $N_{aux}$  decreases the voltage stress on the transistors but on the other hand it increases the voltage stress on the auxiliary diodes. Thus, in order to achieve equal voltage stress on the switches and diodes  $N_{aux}$  should be chosen as 1:1 as shown in 3.17

$$U_{D,REV,MAX} = U_{T6,MAX} \rightarrow N_{aux} = 1. \tag{3.17}$$

In order to keep the voltage stress on the switches equal in the both operating modes, with enabled auxiliary circuit and disabled auxiliary circuit, 3.11 and 3.16 should be equal, thus limiting the  $N_{aux}$  minimum value to

$$N_{aux,MIN} = \frac{1 - D_A}{D_A},\tag{3.18}$$

where  $D_A$  represents the duty cycle for the operation mode with  $D_A \leq 0.5$ . The turn's ratio of the auxiliary transformer also determines the boost factor of the CDR if the duty cycle of the control signals is  $D_A \leq 0.5$  in the continuous conduction mode. From the steady-state analysis presented in [PAPER-III], the  $N_{aux}$  selection can be made according to the required boost factor. The  $N_{aux}$  can be selected according to the required voltage boost b in the following way:

$$N_{aux} = \frac{N_{TR} \cdot (2D_A - 1)}{D_A \cdot (b - 2 \cdot N_{TR})}.$$

(3.19)

It can be seen that there are several criteria for selecting the turn's ratio of the auxiliary transformers that must be considered during the design.

The last component of the auxiliary circuit is the auxiliary switch  $T_{aux}$ . It is needed to detach the auxiliary circuit from the CDR in case the duty cycle  $D_A \le 0.5$ , otherwise the system loses its stability due to positive feedback. The switch carries the current that is double times the current through the auxiliary diodes, thus

$$I_{Taux} = 2 \cdot I_{D,AV}. \tag{3.20}$$

The maximal voltage stress on the switch, however, is applied during the operation mode with  $D_A > 0.5$ , when the auxiliary circuit is disabled. The voltage stress on the switch can be calculated as follows:

$$U_{Taux,MAX} = U_{LV} \cdot \left[ N_{aux} \left( \frac{2D_{A,MAX} - 1}{1 - D_{A,MAX}} \right) \right]. \tag{3.21}$$

Although the auxiliary circuit is disabled in the operating mode with  $D_A > 0.5$ , the voltage stress on the auxiliary switch depends on the turns ratio of the auxiliary transformer.

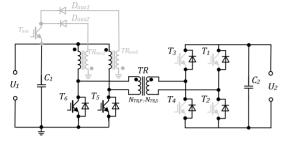

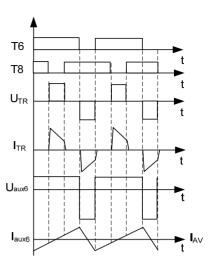

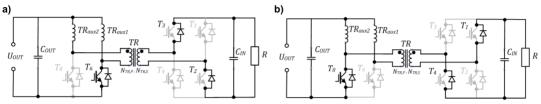

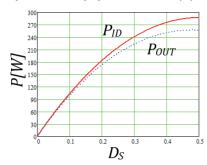

# 3.3 Quasi-Z Source Inverter PEBB

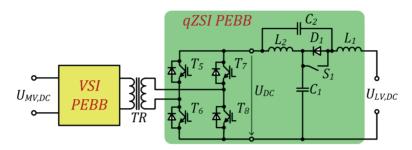

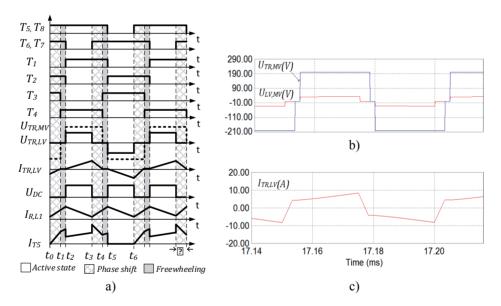

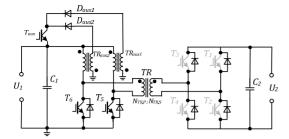

The proposed combination of a qZSI PEBB and a VSI PEBB results in a new topology called qZS-based DAB which has been presented in [PAPER-VI]. The paper describes the operating principle of the qZS-DAB and presents its typical waveforms. In addition, paper provides a steady state analysis with boost factor estimation and power flow control and experimental results.

A schematic of the qZS-DAB is shown in Figure 3.4. It consists of two inductors  $L_I$  and  $L_2$ , two capacitors  $C_I$  and  $C_2$ , a diode  $D_I$ , and a switch  $S_I$ . The aim of the qZS network is to step-up the voltage on the LV DC-link to match

the criterion 2.2. The step-up of the LV in the reverse operating mode is achieved by simultaneous turn-on (also called shoot-through) of the inverter switches  $T_5...T_8$  of the qZSI PEBB. During the shoot-through state the energy is stored in the inductances of the qZS network while the diode  $D_I$  prevents the short circuit of the capacitors  $C_I$  and  $C_2$ . To allow the energy flow in both directions, the diode  $D_I$  is shunted with the switch  $S_I$  in the forward operating mode. In this case, the energy is transferred from the MV side VSI by means of the rectangular modulation of the DAB while qZS network acts as a filter.

Figure 3.4. Schematic of the qZSI PEBB.

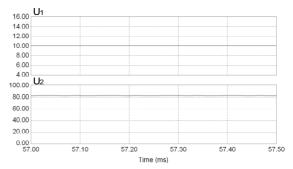

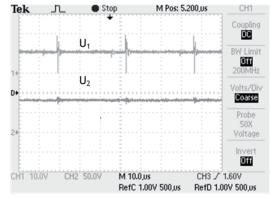

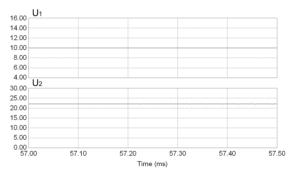

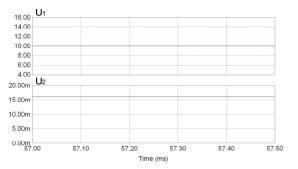

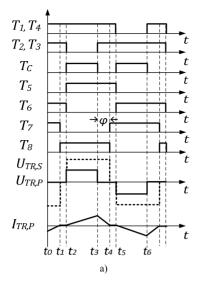

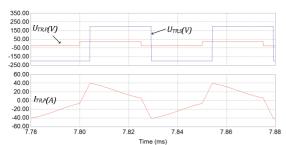

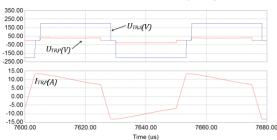

Figure 3.5. Operating principle of the qZS-based DAB: a) typical waveforms; b) simulated transformer voltages; c) simulated transformer current.

The control signals and typical waveforms of the qZS-based DAB in the reverse operating mode are shown in Figure 3.5. It can be seen that during the shoot-through state the current through the switch  $T_5$  rises rapidly during  $t_0...t_1$ , and continues to rise with the same slope as the inductor  $L_1$  and  $L_2$  current during

$t_1...t_2$ . The voltage on the DC-link of the qZSI PEBB can be obtained in the following way:

$$U_{DC} = U_{LV,DC} \cdot \frac{1}{1 - 2D_S}, \tag{3.22}$$

where  $D_S$  designates the relative duration of the shoot-through state. In order to match the criterion 2.2, the qZSI PEBB must achieve a corresponding voltage level on the LV side DC-link, as shown in 3.23

$$U_{MV,DC} = U_{DC} \cdot N_{TR}. \tag{3.23}$$

The qZS-based DAB can be controlled by using the rectangular modulation technique in both operating modes. In addition, in the reverse operating mode the phase angle control can be used simultaneously with voltage step-up by means of the IMM. The advantages of the qZS-based DAB over the conventional DAB are: i) improved shoot-through immunity, ii) reduced current stress on the switches and capacitors, iii) continuous input current, iv) no need for additional filters on the LV side, v) voltage step-up on the LV side. The major drawbacks of this topology are: i) increased number of passive elements, ii) increased risk of oscillations, iii) poor operation under small-loads and relatively low switching frequency [71], iv) limited ZVS range due to unsymmetrical structure.

# Design considerations

When designing the qZS-based DAB for the bi-directional mode, the component values should be dimensioned according to the maximum current and voltage stresses. Some design guidelines of the qZSI are presented in [45]. The maximal stress values on inductances  $L_1$ ,  $L_2$ , capacitors  $C_1$ ,  $C_2$  and diode  $D_1$  apply in the reverse operating mode. The inductances of the qZSI PEBB limit the current ripple in the switch during the shoot-through. The current reaches its peak value at the end of the shoot-through state. From the steady-state analysis the needed inductance of  $L_1$  and  $L_2$  can be estimated as follows:

$$L = \frac{U_{LV}^2}{P_{LV,MAX} \cdot f_S \cdot k_I} \cdot \frac{D_{S,MAX} \left(1 - D_{S,MAX}\right)}{1 - 2 \cdot D_{S,MAX}},$$

(3.24)

where  $P_{LV,MAX}$  is the power at the maximum phase angle and the shoot-through duty cycle  $D_{S,MAX}$  value,  $k_I$  designates the ratio of the current ripple and the average current  $\Delta I_L/I_{LAV}$ .

Next, in order to limit the voltage ripple, the capacitors should be dimensioned accurately. The voltage ripple depends on the maximal shoot-through duration  $D_{S,MAX}$ . During the shoot-through state the capacitors  $C_1$  and  $C_2$  are connected in series and thus the capacitance of each capacitor, assuming that capacitors are equal, can be obtained in the following way:

$$C = \frac{2 \cdot P_{LV,MAX}}{U_{LV}^2 \cdot f_S \cdot k_U} \cdot D_{S,MAX} (1 - 2 \cdot D_{S,MAX}), \tag{3.25}$$

where  $k_U$  is the ratio of the voltage ripple and average voltage on the DC-link  $k_U = \Delta U/U_{DC}$ .

Other elements of the qZSI PEBB are the diode  $D_I$  and the switch  $S_I$ . The maximal reverse voltage stress on the diode  $D_I$  and the switch  $S_I$  (open state) applies during the shoot-through state of the inverter switches  $T_5...T_8$ , and can be estimated in a similar way as 3.23:

$$U_{D1,REV,MAX} = U_{S1,MAX} = U_{LV} \cdot \frac{1}{1 - 2 \cdot D_{S,MAX}}.$$

(3.26)

The average current through the diode can be estimated as follows:

$$I_{D1,AV} = \frac{P_{LV,MAX}}{U_{LV}} \,. \tag{3.27}$$

The current rating of the switch  $S_I$  should be selected according to the full current rating in the forward operating mode when it is in the conducting state. The steady-state voltage stress on the controllable switches  $T_5...T_8$  applies during the non-conducting state of the switches and is equal to the voltage value on the DC-link

$$U_{Tr} = U_{DC}. ag{3.28}$$

The average current through the switches in the reverse operating mode at the maximal power level  $P_{LV,MAX}$  can be found according to 3.29 in a following way:

$$I_{Tx} = \frac{P_{LV,MAX}}{2 \cdot U_{LV}} \,. \tag{3.29}$$

In order to reduce the size and the mass of the inductors, they can be wound on the common core forming this way the coupled inductors, as was done in [72].

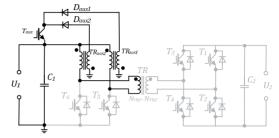

# 3.4 Current-Fed DC/DC Converter with an Active Clamp PEBB

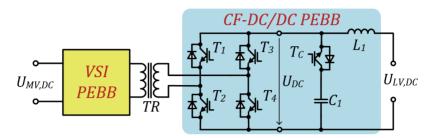

The proposed combination of a CF-DC/DC PEBB and a VSI PEBB results in the new topology, the CF-DC/DC based DAB with an active clamp, which is described in [PAPER-VII]. The paper describes the operating principle of the converter and presents its typical waveforms. In addition, paper provides a steady state analysis with boost factor estimation, power flow control and simulation results. The loss analysis and the experimental results are presented in [PAPER-VIII].

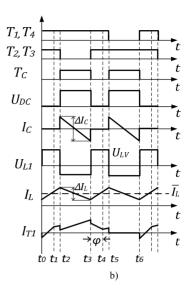

A schematic of such combination is shown in Figure 3.6. The CF-DC/DC PEBB consists of an inductor  $L_I$ , a capacitor  $C_I$ , a controllable switch  $T_C$  with an anti-parallel diode and an inverter. In the forward operating mode, the power is transferred from the MV port to the LV port by means of the rectangular modulation of the DAB while CF-DC/DC PEBB acts as a filter. In the reverse operating mode the voltage step-up on the LV side can be used, to match the criterion 2.2. The voltage step-up takes place by means of the simultaneous shoot-through state of the switches on the LV side inverter. During the shoot-

through the energy is stored in the inductor  $L_I$  and redirected to the MV port during the active state. The switch  $T_C$  is turned off during the shoot-through state in order to prevent the short circuit of the capacitor  $C_I$ .

Figure 3.6. Schematic of the CF-DC/DC PEBB.

The boost factor the CF-DC/DC PEBB can be determined by the following equation:

$$U_{DC} = U_{LV,DC} \cdot \frac{1}{1 - D_S} \,. \tag{3.30}$$

It has the following advantages over the DAB: i) voltage step-up capability, ii) no need for additional filter on the LV side, iii) reduced current and voltage stress on the components. The major drawbacks of this topology are: i) limited ZVS range due to unsymmetrical structure, ii) increased switching and conduction losses due to additional switch  $T_C$ .

# Design considerations

Detailed design guidelines for the CF-DC/DC PEBB converter are presented in [PAPER-VII] and [73].

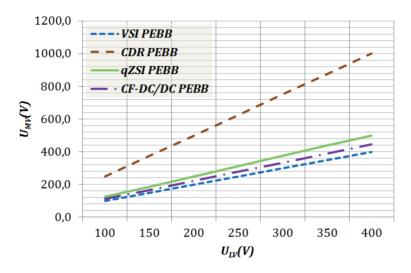

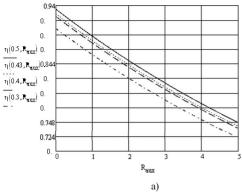

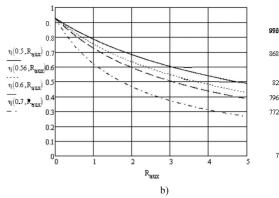

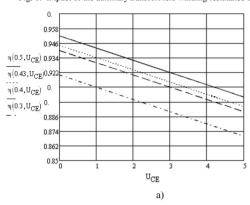

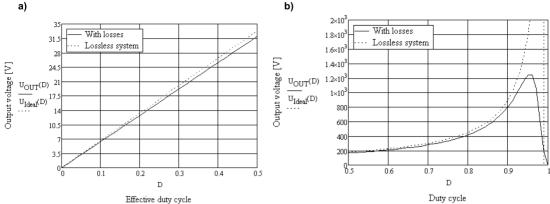

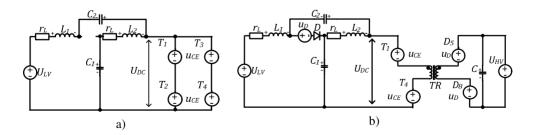

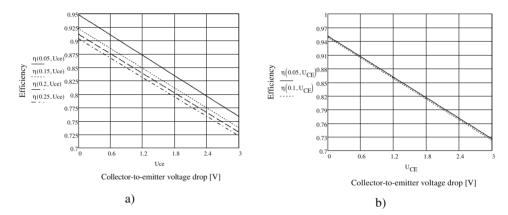

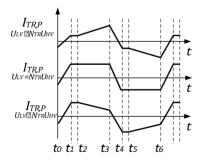

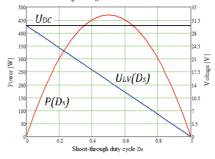

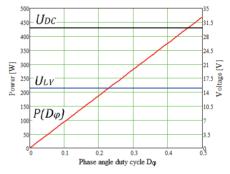

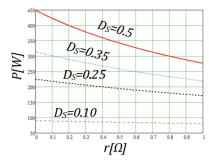

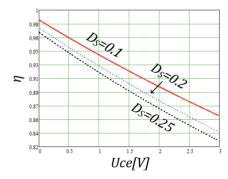

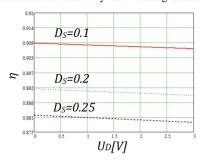

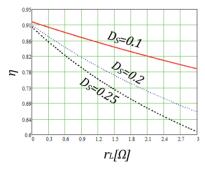

# 3.5 Voltage Regulation Range

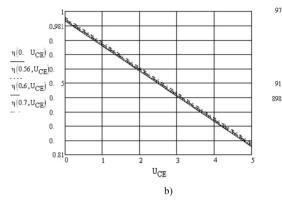

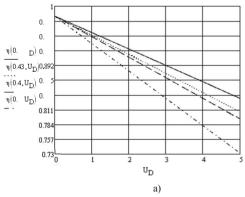

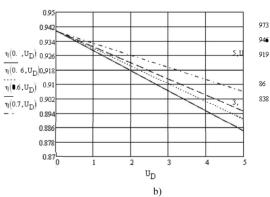

Keeping the voltage on the LV side at the constant level is a task that the isolation stage has to fulfill. If the PET operates in the reverse mode, then too low voltage level on the LV side reduces the power transfer performance and increases the voltage and current stress on the components. Compared to the VSI PEBB, the proposed PEBB-s have the voltage step-up properties. Such feature enables to keep the voltage on a stable level and reduce the stress values on the components. The mathematically derived voltage boost factors of the proposed PEBB-s are depicted in Figure 3.7. Here, the PEBB-s are controlled with the active duty cycle is  $D_A = 0.6$ , shoot-through is  $D_S = 0.1$  and the phase shift value is  $D_{\varphi} = 0.1$ . The transformer turn's ratio is  $N_{TR} = 1$ . The VSI PEBB is controlled with the rectangular modulation method and voltages on MV and LV ports are equal. However, the CDR PEBB can regulate the voltage level in a very wide range and reaches  $U_{MV} = 300 \text{ V}$  at  $U_{LV} = 130 \text{ V}$ . The qZSI PEBB

reaches  $U_{MV}$  = 300 V at  $U_{LV}$  = 250 V voltage level on the LV side. The LC-filter based DAB reaches  $U_{MV}$  = 300 V voltage on the MV side at  $U_{LV}$  = 280 V.

Figure 3.7. Voltage regulation range of the VSI PEBB and proposed PEBB-s.

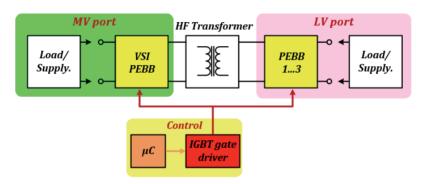

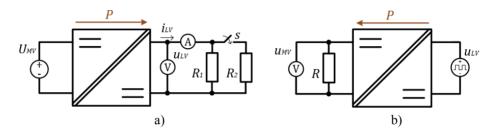

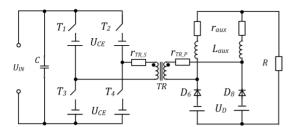

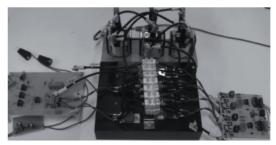

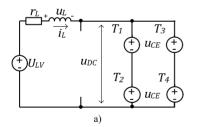

## 3.6 Laboratory Test Bench

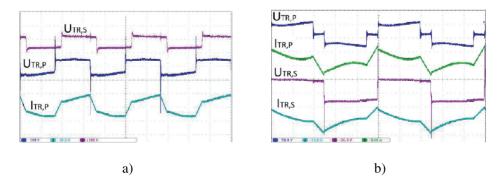

In order to experimentally analyze the proposed PEBB-s, a flexible prototype was developed. The prototype allows all four topologies to be tested under similar conditions and at the same power level. The test bench consists of the IGBT based VSI on the MV port, the MF transformer and the proposed PEBB-s on the LV port.

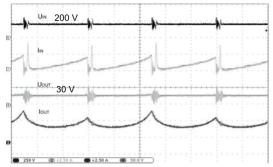

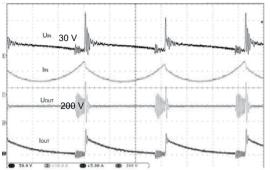

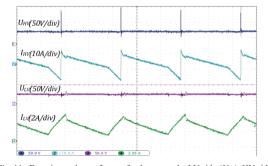

Although the final application, the PET, is a high-power device, the prototype was built for the lower voltage and power levels. The IGBT-s IRG7Ph42ud1pbf were chosen for the LV port VSI and IRG4PH50UDPbf for the MV port VSI. A low voltage side voltage of  $U_{LV} = 30$  V and high voltage side  $U_{MV} = 200$  V are used during the experimental investigation. A DSPIC33FJ64GS606 microcontroller is used to generate the gating signals for the IGBT driver circuits. The IR2181 type IGBT drivers are used to control the switches on the MV side VSI PEBB and MC33153 IGBT drivers were used to control the switches on the LV side VSI PEBB. The main parameters of the test bench and its components are summarized in Table 3.1 and the block diagram of the experimental prototype is shown in Figure 3.8.

| Table 3.1. | Parameters | of | the | laboratory | test bene | гh. |

|------------|------------|----|-----|------------|-----------|-----|

|            |            |    |     |            |           |     |

| Parameter                                  | Value      |

|--------------------------------------------|------------|

| Low side voltage $U_{LV}$                  | 30 V (DC)  |

| Medium side voltage $U_{MV}$               | 200 V (DC) |

| Saturation voltage of IGBT-s (LV) $U_{CE}$ | 1.7 V      |

| Saturation voltage of IGBT-s (MV) $U_{CE}$ | 2.7 V      |

| Voltage drop of the diodes $U_D$           | 1.1 V      |

| Blocking voltage of the IGBT-s             | 1200 V     |

| Nominal collector current $I_C$            | 30 A       |

| Switching frequency $f_S$                  | 30 kHz     |

Figure 3.8. Block diagram of the experimental test bench.

# 3.7 Summary

In order to overcome the challenges of the DAB and extend the control range of the isolation stage, three new PEBB-s were proposed: CDR PEBB, qZSI PEBB and CF-DC/DC PEBB. The combination of the proposed PEBB-s and a VSI PEBB resulted in the new topologies. The comparison of the VSI PEBB and the proposed PEBB-s are presented in Table 3.2. The CDR PEBB has a low number of switches, improved shoot-through immunity, very good voltage step-up properties and equal current sharing. However, the presence of three transformers increases the weight of the converter and causes significant overvoltage peaks (up to 225 %) during the turn-off of the switches that limits the use of this topology without additional snubber circuits. The qZSI PEBB has also improved shoot-through immunity and good voltage step-up properties, with reduced current stress on the capacitors and voltage stress on the switches. However increased number of passive elements increases the size of the converter and the conduction losses. CF-DC/DC PEBB has reduced number of passive elements in comparison with qZSI PEBB, however it has increased switching and conduction losses due to the additional switch and more complex control. The analytically obtained operating principle and waveforms were verified with simulations and tested on the experimental prototype. The experimental results showed the correspondence to the analytically obtained

waveforms. In addition, it was verified that proposed PEBB-s do not cause any instabilities in the forward and in the reverse operating modes. The design guidelines for the proposed PEBB-s were provided. During the design, the components should be selected according to the bi-directional mode of the converters.

Table 3.2. Comparison of the PEBB-s for the isolation stage.

|                                          | VSI<br>PEBB | CDR PEBB                       | qZSI PEBB                       | CF-DC/DC<br>PEBB                 |

|------------------------------------------|-------------|--------------------------------|---------------------------------|----------------------------------|

| No. of switches                          | 4           | 3                              | 5                               | 5                                |

| No. of diodes                            | 4           | 4                              | 5                               | 5                                |

| No. of passive elements                  | -           | 3                              | 4                               | 2                                |

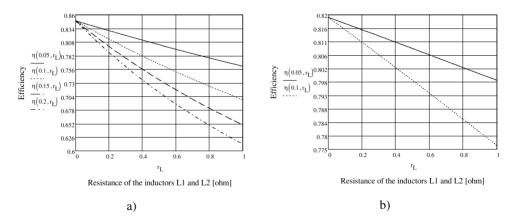

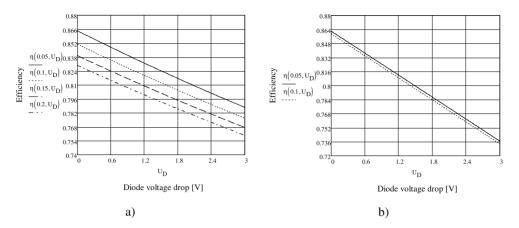

| ZV turn-on                               | Yes         | Yes                            | Yes                             | Yes                              |