#### **DOCTORAL THESIS**

## Assessment and Enhancement of Hardware Reliability for Deep Neural Networks

Mohammad Hasan Ahmadilivani

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2025 TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 19/2025

## Assessment and Enhancement of Hardware Reliability for Deep Neural Networks

MOHAMMAD HASAN AHMADILIVANI

TALLINN UNIVERSITY OF TECHNOLOGY School of Information Technologies Department of Computer Systems

### The dissertation was accepted for the defense of the degree of Doctor of Philosophy in Information and Communication Technologies on January 2, 2025.

| Supervisor:    | Professor Jaan Raik,<br>Department of Computer Systems, School of Information Technologies,<br>Tallinn University of Technology,<br>Tallinn, Estonia          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Co-supervisor: | Professor Masoud Daneshtalab,<br>Department of Computer Systems, School of Information Technologies,<br>Tallinn University of Technology,<br>Tallinn, Estonia |

| Opponents:     | Professor Yanjing Li,<br>University of Chicago,<br>Chicago, USA<br>Professor Luciano Ost,<br>Loughborough University,<br>Loughborough, UK                     |

Defense of the thesis: April 4, 2025, Tallinn

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for any academic degree elsewhere.

Mohammad Hasan Ahmadilivani

signature

Copyright: Mohammad Hasan Ahmadilivani, 2025 ISSN 2585-6898 (publication) ISBN 978-9916-80-275-5 (publication) ISSN 2585-6901 (PDF) ISBN 978-9916-80-276-2 (PDF) DOI https://doi.org/10.23658/taltech.19/2025 Printed by Koopia Niini & Rauam

Ahmadilivani, M. H. (2025). Assessment and Enhancement of Hardware Reliability for Deep Neural Networks [TalTech Press]. https://doi.org/10.23658/taltech.19/2025

TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 19/2025

# Riistvara töökindluse hindamine ja täiustamine süvanärvivõrkude jaoks

MOHAMMAD HASAN AHMADILIVANI

#### Contents

| List of Publications                         |                                 |          |            |                                                  |    |

|----------------------------------------------|---------------------------------|----------|------------|--------------------------------------------------|----|

| Author's Contributions to the Publications 1 |                                 |          |            | 11                                               |    |

| Abbreviations 12                             |                                 |          |            | 12                                               |    |

| 1                                            | Intro                           | duction  |            |                                                  | 14 |

|                                              | 1.1                             |          |            |                                                  | 16 |

|                                              | 1.2                             |          |            | ation and Research Questions                     | 18 |

|                                              | 1.3                             |          |            |                                                  | 19 |

|                                              | 1.4                             | Thesis   | Organizati | on                                               | 22 |

| 2                                            | Back                            | ground   |            |                                                  | 24 |

|                                              | 2.1                             | -        |            | ility                                            | 24 |

|                                              |                                 | 2.1.1    |            | n and Concept                                    | 24 |

|                                              |                                 | 2.1.2    |            | e Faults: Definition, Classification, and Impact | 25 |

|                                              |                                 | 2.1.3    |            | rs: Origination and Impact                       | 26 |

|                                              |                                 | 2.1.4    |            | erance Techniques                                | 27 |

|                                              |                                 | 2.1.5    |            | on and Metrics                                   | 28 |

|                                              | 2.2                             | Deep N   | Veural Net | works                                            | 29 |

|                                              |                                 | 2.2.1    | Convolut   | ional Neural Networks                            | 29 |

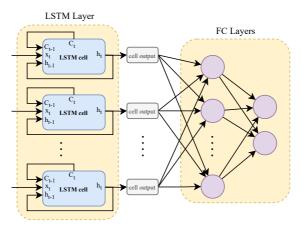

|                                              |                                 | 2.2.2    | Long Sho   | rt-Term Memory Neural Networks                   | 31 |

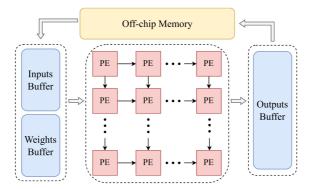

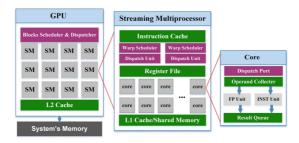

|                                              | 2.3                             | DNN H    |            | ccelerators                                      | 32 |

| 3                                            | Liter                           | ature Re | eview on t | he Reliability Assessment Methods for DNNs       | 35 |

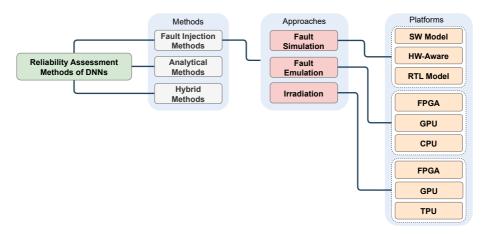

| 0                                            | 3.1                             |          |            |                                                  | 35 |

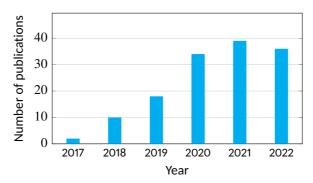

|                                              | 3.2                             |          |            | v Methodology                                    | 36 |

|                                              | 3.3                             |          |            | rends                                            | 37 |

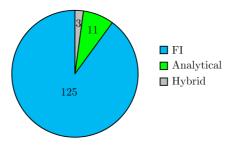

|                                              | 0.0                             | 3.3.1    |            | rization of Existing Methods                     | 37 |

|                                              |                                 | 3.3.2    |            | Trends                                           | 38 |

|                                              | 3.4                             |          |            | ethods                                           | 39 |

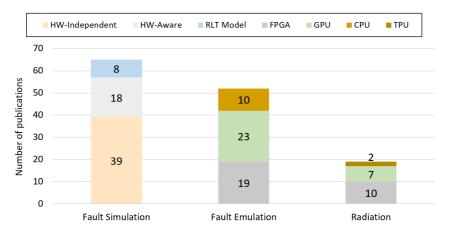

|                                              |                                 | 3.4.1    | -          | nulation                                         | 40 |

|                                              |                                 |          | 3.4.1.1    | Hardware-Independent Platform                    | 40 |

|                                              |                                 |          | 3.4.1.2    | Hardware-Aware Platform.                         | 42 |

|                                              |                                 |          | 3.4.1.3    | RTL Model Platform.                              | 43 |

|                                              |                                 | 3.4.2    | Fault Em   | ulation                                          | 43 |

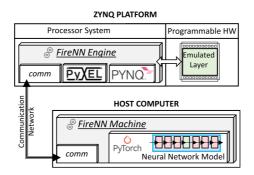

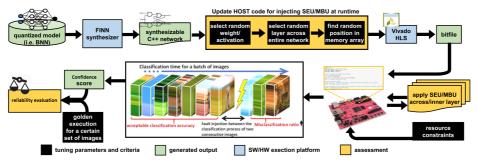

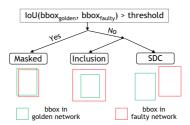

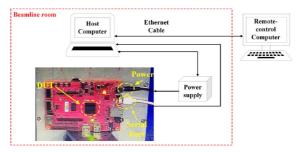

|                                              |                                 |          | 3.4.2.1    | FPGA Platform.                                   | 44 |

|                                              |                                 |          | 3.4.2.2    | GPU Platform.                                    | 46 |

|                                              |                                 |          | 3.4.2.3    | CPU Platform.                                    | 48 |

|                                              |                                 | 3.4.3    |            | on                                               | 49 |

|                                              |                                 |          | 3.4.3.1    | FPGA Platform.                                   | 49 |

|                                              |                                 |          | 3.4.3.2    | GPU Platform.                                    | 49 |

|                                              |                                 |          | 3.4.3.3    | TPU Platform.                                    | 50 |

|                                              | 3.5                             | Analyt   |            | ods                                              | 50 |

|                                              |                                 |          |            | 52                                               |    |

|                                              | 3.7                             |          |            | itative Comparison and Open Challenges           | 53 |

| 3.8 Chapter Conclusions                      |                                 |          |            | 56                                               |    |

| 4                                            | Reliability Assessment for CNNs |          |            |                                                  |    |

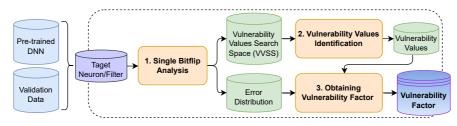

|   | 4.1     | DeepVi                                                      | gor: Vulne  | erabllity Value RanGes and FactORs                      | 58       |

|---|---------|-------------------------------------------------------------|-------------|---------------------------------------------------------|----------|

|   |         | 4.1.1                                                       | Fault Mo    | del                                                     | 58       |

|   |         | 4.1.2                                                       | Fault Pro   | pagation Analysis                                       | 58       |

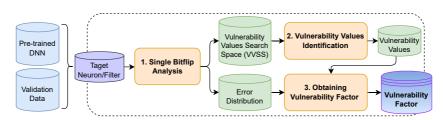

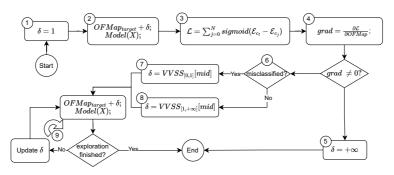

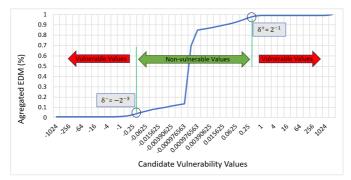

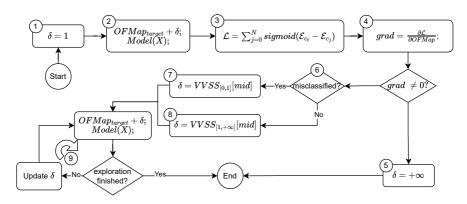

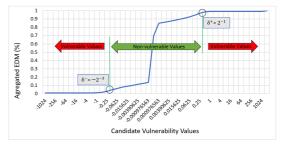

|   |         | 4.1.3                                                       | The Deep    | oVigor Method                                           | 58       |

|   |         | 4.1.4                                                       | Validating  | g DeepVigor By Fault Injection                          | 61       |

|   |         | 4.1.5                                                       | Experime    | ental Setup                                             | 62       |

|   |         | 4.1.6                                                       | Results a   | nd Validation                                           | 62       |

|   |         | 4.1.7                                                       | Run-Time    | e Analysis                                              | 63       |

|   |         | 4.1.8                                                       | Discussio   | n                                                       | 64       |

|   | 4.2     | DeepVigor+: Scalable and Accurate Fault Resilience Analysis |             |                                                         |          |

|   |         | 4.2.1                                                       |             | del                                                     |          |

|   |         | 4.2.2                                                       | Fault Pro   | pagation Model                                          | 66       |

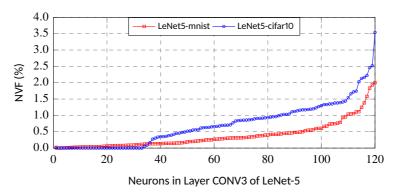

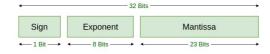

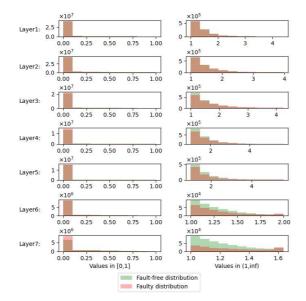

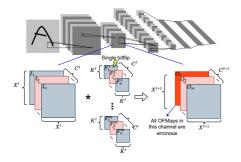

|   |         |                                                             | 4.2.2.1     | Single Fault Analysis in 32-bit Floating-Point          | 66       |

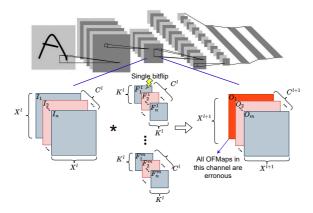

|   |         |                                                             | 4.2.2.2     | Single Fault Error Propagation in CNNs                  |          |

|   |         | 4.2.3                                                       |             | oVigor+ Method                                          |          |

|   |         | 4.2.4                                                       |             | ental Setup                                             |          |

|   |         |                                                             | 4.2.4.1     | DeepVigor+ Implementation                               |          |

|   |         |                                                             | 4.2.4.2     | Validating DeepVigor+ by Fault Injection                |          |

|   |         |                                                             | 4.2.4.3     | CNNs Under Study                                        |          |

|   |         | 4.2.5                                                       |             |                                                         |          |

|   |         | 7.2.5                                                       | 4.2.5.1     | DeepVigor+ Accuracy Compared to FI                      |          |

|   |         |                                                             | 4.2.5.2     | Sampling Analysis vs. Complete Analysis                 | 75       |

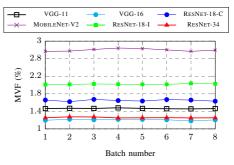

|   |         |                                                             | 4.2.5.3     | Run-Time and Scalability Investigation                  | 76       |

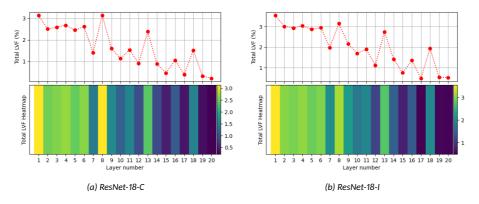

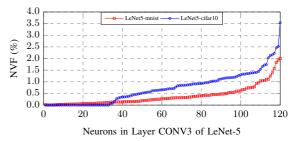

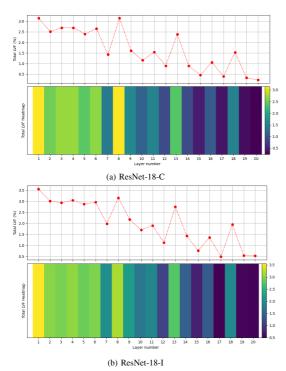

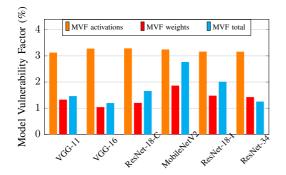

|   |         |                                                             | 4.2.5.4     | Reliability Visualization and Comparison for CNNs       | 78       |

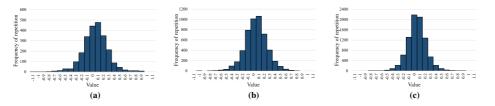

|   |         |                                                             | 4.2.5.5     | Impact of Input Data on the Quality of Results          | 80       |

|   |         | 4.2.6                                                       |             |                                                         |          |

|   | 4.3     |                                                             |             |                                                         | 80<br>81 |

|   | 4.3     |                                                             |             |                                                         |          |

|   |         | 4.3.1                                                       |             | er reliability enhancement for QNNs accelerators        | 81       |

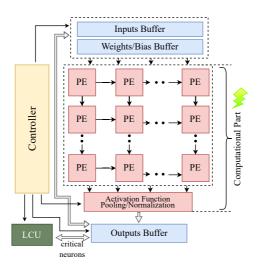

|   |         |                                                             | 4.3.1.1     | Accelerator Model                                       |          |

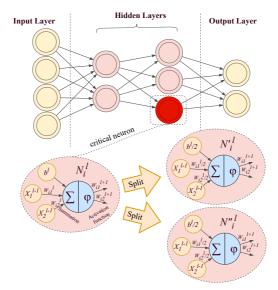

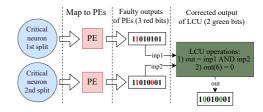

|   |         |                                                             | 4.3.1.2     | Identifying Critical Neurons by QDeepVigor              | 82       |

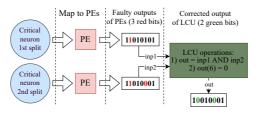

|   |         |                                                             | 4.3.1.3     | Resilience Enhancement by LCU and Neuron Splitting      |          |

|   |         |                                                             | 4.3.1.4     | Experimental Setup                                      |          |

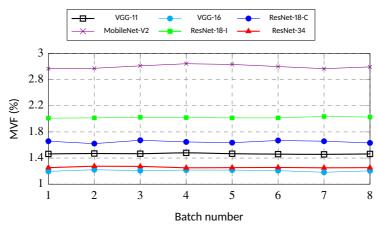

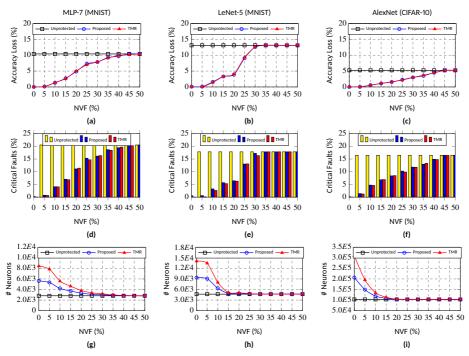

|   |         |                                                             | 4.3.1.5     | Results: An Exploration on NVF of QNNs                  |          |

|   |         | 4.3.2                                                       |             | Method for QNNs' Reliability Assessment                 |          |

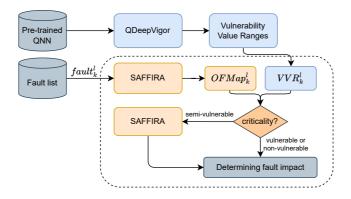

|   |         |                                                             | 4.3.2.1     | Hybrid Method: QDeepVigor and SAFFIRA                   |          |

|   |         |                                                             | 4.3.2.2     | Results: Simulation Speed-up                            |          |

|   | 4.4     | Chapte                                                      | r Conclusi  | ons                                                     | 89       |

| ~ | D - I'- | L                                                           | l           |                                                         | ~~       |

| 5 |         |                                                             |             | nt for CNNs                                             | 90       |

|   | 5.1     |                                                             |             | ault Tolerance for CNNs                                 | 90       |

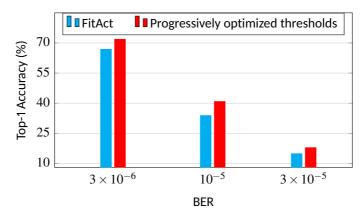

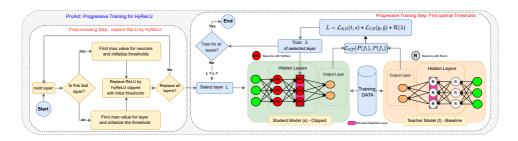

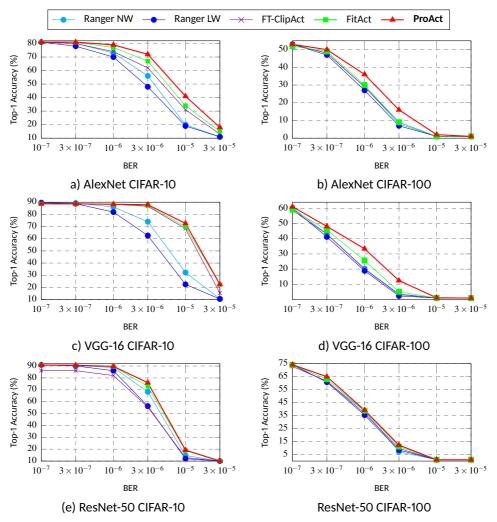

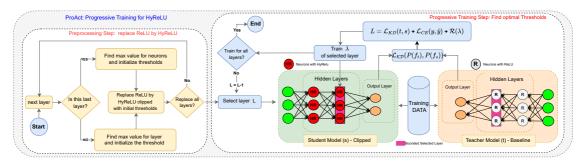

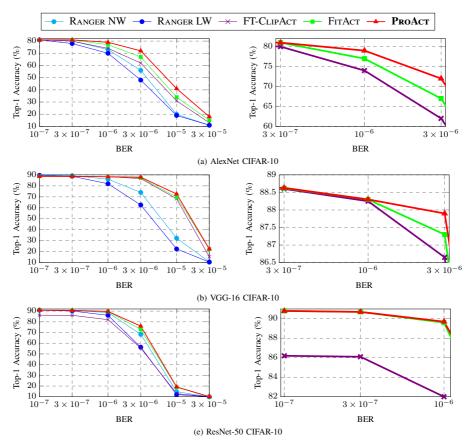

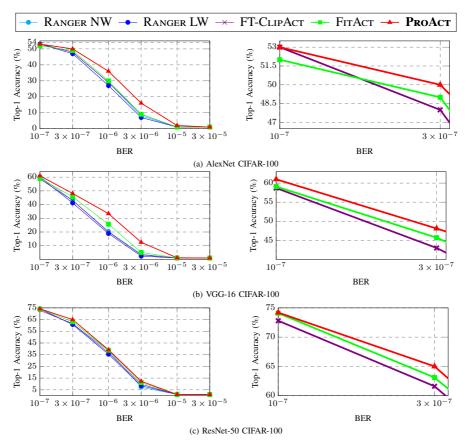

|   | 5.2     |                                                             | -           | ive Training for Hybrid Clipped Activation Function     | 92       |

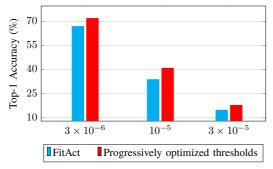

|   |         | 5.2.1                                                       |             | Motivation                                              | 92       |

|   |         | 5.2.2                                                       |             | ology: ProAct and HyReLU                                | 93       |

|   |         | 5.2.3                                                       | •           | ental Setup                                             | 96       |

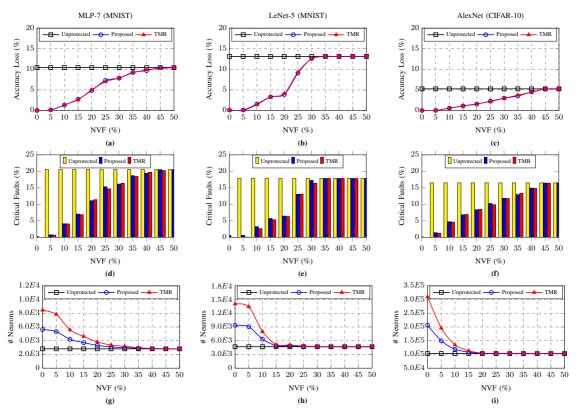

|   |         | 5.2.4                                                       |             | Overhead Reduction and Resilience Improvement           | 97       |

|   |         |                                                             | 5.2.4.1     | Effect of Activation Restriction Methods on DNNs' Base- |          |

|   |         |                                                             |             | line Accuracy- and Memory Footprint                     | 97       |

|   |         |                                                             | 5.2.4.2     | Resilience Comparison of Activation Restriction Methods | 98       |

|   |         | 5.2.5                                                       |             | n                                                       | 98       |

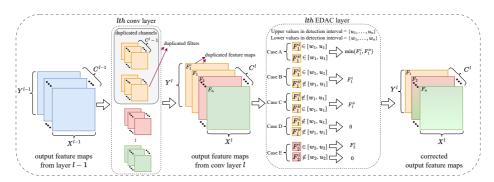

|   | 5.3     | Channe                                                      | el Duplicat | ion and Vulnerability-Aware Pruning                     | 99       |

|     |                     | 5.3.1     | CNN Model Hardening 100 |                                                           |      |

|-----|---------------------|-----------|-------------------------|-----------------------------------------------------------|------|

|     |                     |           | 5.3.1.1                 | Vulnerability Estimation                                  | 100  |

|     |                     |           | 5.3.1.2                 | CNN Model Hardening Method                                | 100  |

|     | 5.3.2 Experime      |           | Experime                | ental Setup                                               | 102  |

|     |                     | 5.3.3     | Results .               |                                                           | 103  |

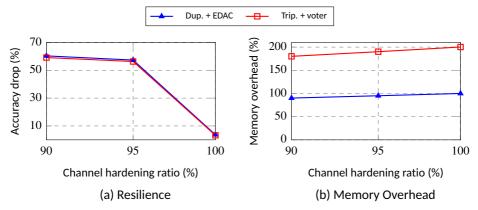

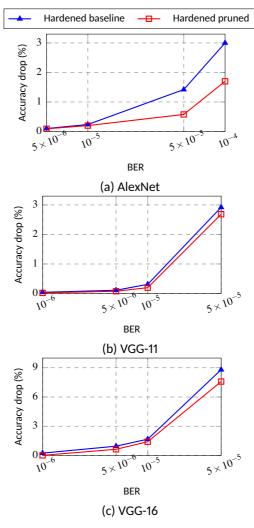

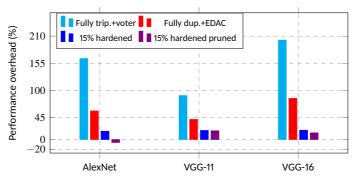

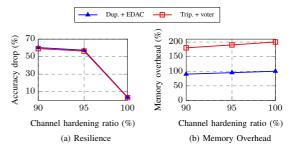

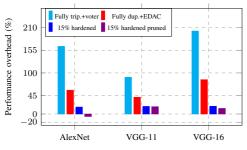

|     |                     |           | 5.3.3.1                 | Hardening by Channel Duplication vs. Triplication         | 103  |

|     |                     |           | 5.3.3.2                 | Hardening by Selective Channels Duplication and EDAC      |      |

|     |                     |           |                         | Layer                                                     | 103  |

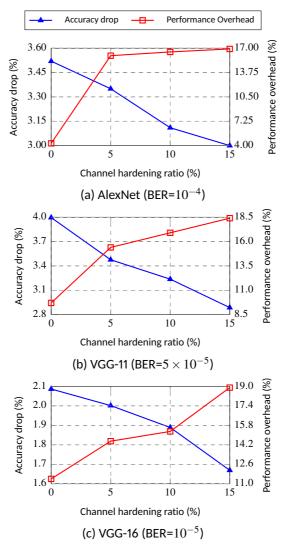

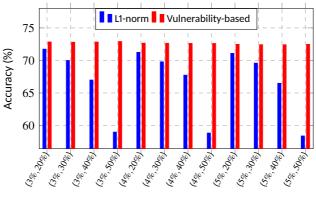

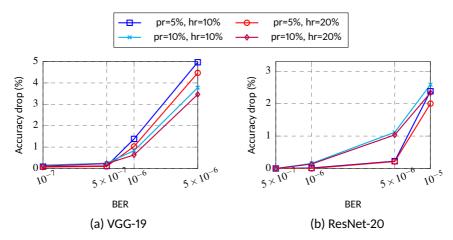

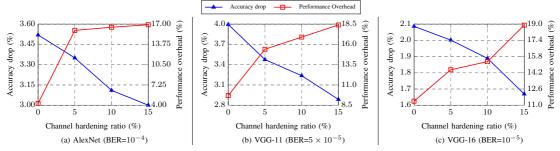

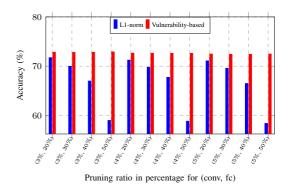

|     |                     | 5.3.4     | Overhead                | d Reduction by Pruning based on Parameters' Vulnerability | /104 |

|     |                     |           | 5.3.4.1                 | Vulnerability-Aware Pruning                               | 104  |

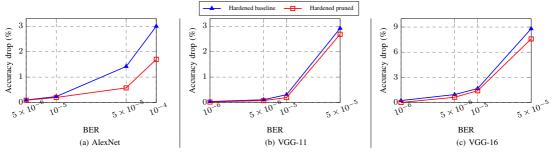

|     |                     |           | 5.3.4.2                 | Resilience and Overhead of the Hardened Pruned CNNs .     |      |

|     |                     | 5.3.5     | Discussio               | n                                                         | 108  |

|     | 5.4                 | Sentine   | elNN: Mod               | lel-Level CNN Hardening Framework                         | 108  |

|     |                     | 5.4.1     |                         | ental Setup                                               |      |

|     |                     | 5.4.2     |                         | ental Results                                             |      |

|     | 5.5                 |           | •                       | ons                                                       |      |

|     |                     |           |                         |                                                           |      |

| 6   | Relia               | bility As | sessment                | and Enhancement for LSTMs                                 | 111  |

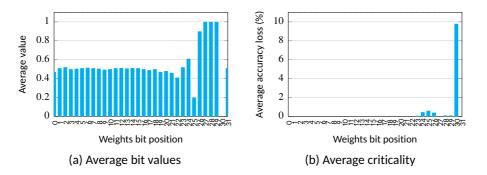

|     | 6.1                 |           |                         | for Gait Analysis                                         |      |

|     |                     | 6.1.1     |                         | Method: Resilience Assessment and Enhancement             |      |

|     |                     |           | 6.1.1.1                 | LSTMs Under Study                                         |      |

|     |                     |           | 6.1.1.2                 | Resilience Assessment by Fault Injection                  |      |

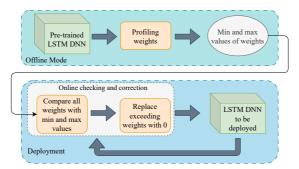

|     |                     |           | 6.1.1.3                 | Resilience Enhancement: Weights Online Checking and       |      |

|     |                     |           |                         | Correction                                                | 113  |

|     |                     | 6.1.2     | Experime                | ental Setup                                               |      |

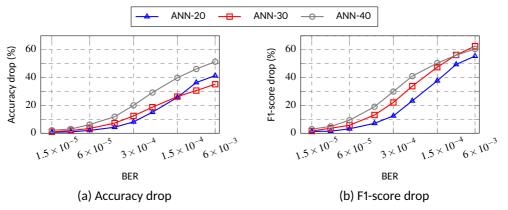

|     |                     | 6.1.3     |                         | ental Results                                             |      |

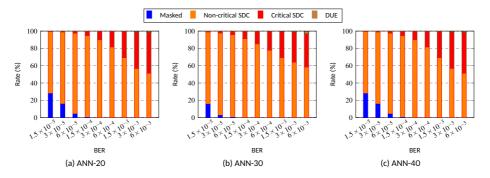

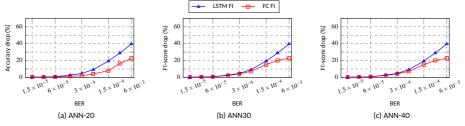

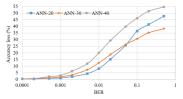

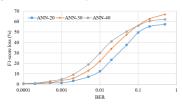

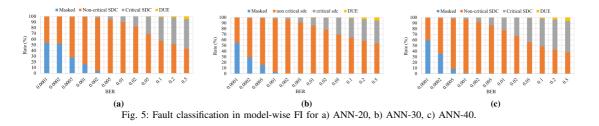

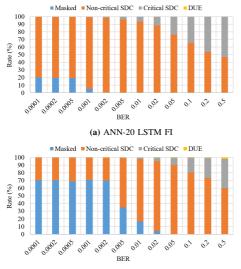

|     |                     |           | 6.1.3.1                 | Model-wise Resilience Analysis                            |      |

|     |                     |           | 6.1.3.2                 | Layer-wise Resilience Analysis.                           |      |

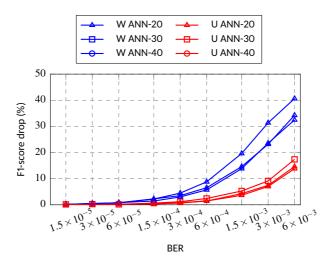

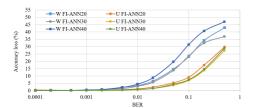

|     |                     |           | 6.1.3.3                 | Inter-LSTM Resilience Analysis: FI into U vs W            |      |

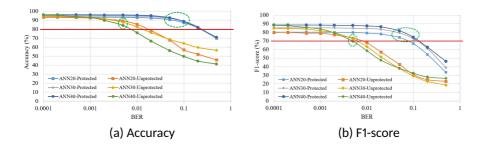

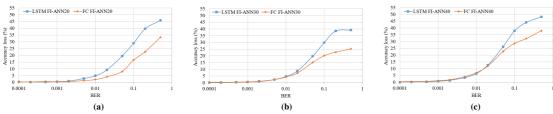

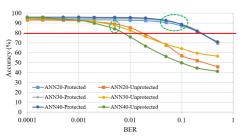

|     |                     |           | 6.1.3.4                 | Resilience Improvement of LSTM-based ANNs                 |      |

|     |                     | 6.1.4     |                         | n                                                         |      |

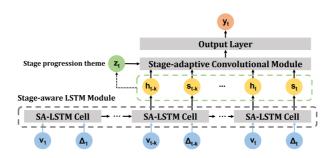

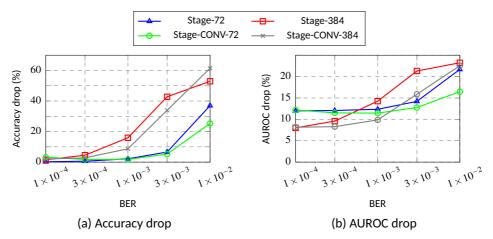

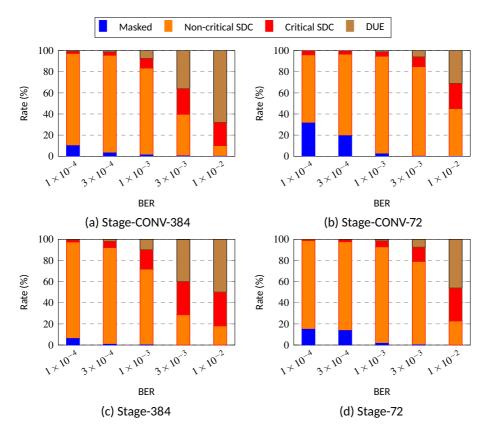

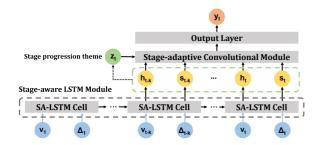

|     | 6.2                 | Convol    |                         | TM DNN for Disease Prediction                             |      |

|     | 0.2                 | 6.2.1     |                         | Method: Resilience Assessment and Enhancement             |      |

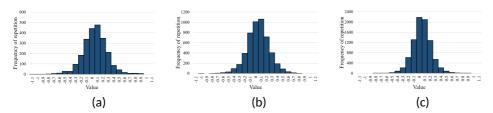

|     |                     | 0.2.1     | 6.2.1.1                 | LSTMs Under Study                                         |      |

|     |                     |           | 6.2.1.2                 | Resilience Assessment by Fault Injection                  |      |

|     |                     |           | 6.2.1.3                 | Resilience Enhancement: Weights and Activations Clip-     | 110  |

|     |                     |           | 0.2.110                 | ping                                                      | 119  |

|     |                     | 6.2.2     | Experime                | ental Setup                                               |      |

|     |                     | 6.2.3     |                         | ental Results                                             |      |

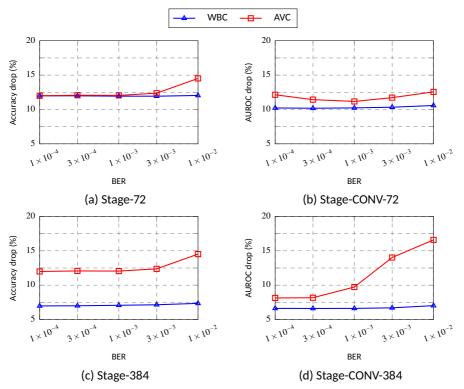

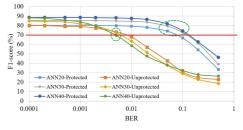

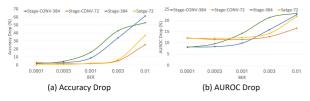

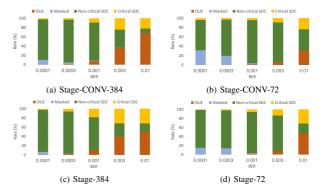

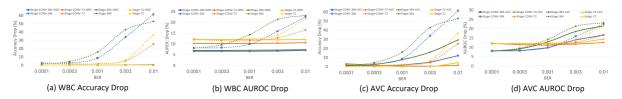

|     |                     | 0.2.0     | 6.2.3.1                 | Resilience Analysis Results                               |      |

|     |                     |           | 6.2.3.2                 | Resilience Improvement Results                            |      |

|     |                     | 6.2.4     |                         | n                                                         |      |

|     | 6.3                 |           |                         | ons                                                       |      |

|     | 0.5                 | Chapte    |                         | 0113                                                      | 120  |

| 7   | Cond                | lusions   | and Futur               | e Directions                                              | 124  |

| ,   | Cont                |           |                         |                                                           | 127  |

| Lis | List of Figures 127 |           |                         |                                                           |      |

|     | <b>.</b>            |           |                         |                                                           |      |

| Lis | List of Tables 128  |           |                         |                                                           |      |

|     |                     |           |                         |                                                           |      |

| References       | 129 |

|------------------|-----|

| Acknowledgements | 149 |

| Abstract         | 150 |

| Kokkuvõte        | 151 |

| Appendix 1       | 153 |

| Appendix 2       | 195 |

| Appendix 3       | 203 |

| Appendix 4       | 219 |

| Appendix 5       | 227 |

| Appendix 6       | 241 |

| Appendix 7       | 251 |

| Appendix 8       | 257 |

| Curriculum Vitae | 263 |

| Elulookirjeldus  | 265 |

#### **List of Publications**

The present Ph.D. thesis is based on the following publications that are referred to in the text by Roman numbers.

- I M. H. Ahmadilivani, M. Taheri, J. Raik, M. Daneshtalab, and M. Jenihhin. A Systematic Literature Review on Hardware Reliability Assessment Methods for Deep Neural Networks. ACM Computing Surveys, 56(6):1–36, 2024. DOI: https://doi.org/10.1145/3638242

- II M. H. Ahmadilivani, M. Taheri, J. Raik, M. Daneshtalab, and M. Jenihhin. DeepVigor: Vulnerability Value RanGes and FactORs for DNNs' Reliability Assessment. In IEEE European Test Symposium (ETS), pages 1–6. Venice, Italy, 2023. DOI: https://doi.org/10.1109/ETS56758.2023.10174133

- III M. H. Ahmadilivani, J. Raik, M. Daneshtalab, and M. Jenihhin. Deepvigor+: A Scalable, Accurate and Automated Framework for Resilience Analysis of Deep Neural Networks. Under review, pages 1–14, 2024.

DOI: https://doi.org/10.48550/arXiv.2410.15742

- IV M. H. Ahmadilivani, M. Taheri, J. Raik, M. Daneshtalab, and M. Jenihhin. Enhancing Fault Resilience of QNNs by Selective Neuron Splitting. In IEEE 5th International Conference on Artificial Intelligence Circuits and Systems (AICAS), pages 1–5. Hangzhou, China, 2023.

DOI: https://doi.org/10.1109/AICAS57966.2023.10168633

- V S. Mousavi, M. H. Ahmadilivani, J. Raik, M. Jenihhin, and M. Daneshtalab. ProAct: Progressive Training for Hybrid Clipped Activation Function to Enhance Resilience of DNNs. Under review, pages 1-12, 2024.

DOI: https://doi.org/10.48550/arXiv.2406.06313

- VI M. H. Ahmadilivani, S. Mousavi, J. Raik, M. Daneshtalab, and M. Jenihhin. Cost-Effective Fault Tolerance for CNNs Using Parameter Vulnerability Based Hardening and Pruning. In The 30th IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS), pages 1–6. Rennes, France, 2023. DOI: https://doi.org/10.1109/IOLTS60994.2024.10616072

- VII M. H. Ahmadilivani, J. Raik, M. Daneshtalab, and A. Kuusik. Analysis and Improvement of Resilience for Long Short-Term Memory Neural Networks. In IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pages 1–4. Juan-Les-Pennes, France, 2023. DOI: https://doi.org/10.1109/DFT59622.2023.10313559

- VIII B. Parchekani, S. Nazari, M. H. Ahmadilivani, A. Azarpeyvand, J. Raik, T. Ghasempouri, and M. Daneshtalab. Zero-Memory-Overhead Clipping-Based Fault Tolerance for LSTM Deep Neural Networks. In IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pages 1–4. Oxforshire, United Kingdom, 2024.

DOI: https://doi.org/10.1109/DFT63277.2024.10753533

#### **Other Publications**

IX M. H. Ahmadilivani, A. Bosio, B. Deveautour, F. F. Dos Santos, J. D. Guerrero Balaguera, M. Jenihhin, A. Kritikakou, R. L. Sierra, S. Pappalardo, J. Raik, J. E. Rodriguez Condia, M. Sonza Reorda, M. Taheri, and M. Traiola. Special Session: Reliability Assessment Recipes for DNN Accelerators. In IEEE 42nd VLSI Test Symposium (VTS), pages 1-11. Tempe, United States of America, 2024.

DOI: https://doi.org/10.1109/VTS60656.2024.10538707

- X N. Cherezova, S. Pappalardo, M. Taheri, M. H. Ahmadilivani, B. Deveautour, A. Bosio, J. Raik, and M. Jenihhin. Heterogeneous Approximation of DNN HW Accelerators based on Channels Vulnerability. In IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC). Tanger, Morocco, 2024. DOI: https://doi.org/10.1109/VLSI-SoC62099.2024.10767798

- XI M. Taheri, M. Riazati, M. H. Ahmadilivani, M. Jenihhin, M. Daneshtalab, J. Raik, M. Sjödin, and B. Lisper. DeepAxe: A Framework for Exploration of Approximation and Reliability Trade-Offs in DNN Accelerators. In IEEE 24th International Symposium on Quality Electronic Design (ISQED), pages 1–8. San Francisco, United States of America, 2023. DOI: https://doi.org/10.1109/ISQED57927.2023.10129353

- XII M. Taheri, M. H. Ahmadilivani, M. Jenihhin, M. Daneshtalab, and J. Raik. Appraiser: DNN Fault Resilience Analysis Employing Approximation Errors. In IEEE 26th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), pages 124-127. Tallinn, Estonia, 2023.

DOI: https://doi.org/10.1109/DDECS57882.2023.10139468

- XIII M. H. Ahmadilivani, M. Barbareschi, S. Barone, A. Bosio, M. Daneshtalab, S. Della Torca, G. Gavarini, M. Jenihhin, J. Raik, A. Ruospo, E. Sanchez, and M. Taheri. Special Session: Approximation and Fault Resiliency of DNN Accelerators. In IEEE 41st VLSI Test Symposium (VTS), pages 1–10. San Diego, United States of America, 2023. DOI: https://doi.org/10.1109/VTS56346.2023.10140043

- XIV I. Dadras, M. H. Ahmadilivani, S. Banerji, J. Raik, and A. Abloo. An Efficient Analog Convolutional Neural Network Hardware Accelerator Enabled by a Novel Memoryless Architecture for Insect-Sized Robots. In 11th International Conference on Modern Circuits and Systems Technologies (MOCAST), pages 1–6. Bremen, Germany, 2022. DOI: https://doi.org/10.1109/MOCAST54814.2022.9837551

- XV I. Dadras, S. Seydi, M. H. Ahmadilivani, J. Raik, and M. E. Salehi. Fully-Fusible Convolutional Neural Networks for End-to-End Fused Architecture with FPGA Implementation. In 30th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 1-5. Istanbul, Turkey, 2023. DOI: https://doi.org/10.1109/ICECS58634.2023.10382831

- XVI J. Rostovski, M. H. Ahmadilivani, A. Krivošei, A. Kuusik, and M. M. Alam. Real-Time Gait Anomaly Detection Using 1D-CNN and LSTM. In Nordic Conference on Digital Health and Wireless Solutions, pages 260-278. Oulu, Finland, Springer, 2024. DOI: https://doi.org/10.1007/978-3-031-59091-7\_17

#### Author's Contributions to the Publications

- I In I, I was the main author, defined the scope and research questions, conducted a systematic search for the literature review, selected 139 papers to be included, and studied them. I developed a taxonomy for categorizing the identified methods and wrote the manuscript.

- II In II, I was the main author, conceptualized the fault resilience analysis, and implemented the method. I conducted the experiments and simulations, analyzed the results, and wrote the manuscript.

- III In III, I was the main author, extended the method, and developed the open-source tool. I conducted the experiments and simulations, analyzed the results, and wrote the manuscript.

- IV In IV, I was the main author, developed and implemented the methodology. I conducted the experiments and simulations, analyzed the results, and wrote the manuscript.

- V In V, I was a co-author and contributed to conceptualizing the methodology. I analyzed the results and wrote the manuscript.

- VI In VI, I was the main author, designed and implemented the method for model-level fault tolerance. I conducted the experiments and simulations, analyzed the results, and wrote the manuscript.

- VII In VII, I was the main author, I designed and implemented LSTMs for gait analysis as well as fault resilience assessment and enhancement. I conducted the experiments and simulations, analyzed the results, and wrote the manuscript.

- VIII In VIII, I was a co-author, initiated the topic, and contributed to designing and implementing the method. I analyzed the results and wrote the manuscript.

#### Abbreviations

| ABFT   | Algorithm-Based Fault Tolerance          |

|--------|------------------------------------------|

| Al     | Artificial Intelligence                  |

| ALU    | Arithmetic Logic Unit                    |

| ASIC   | Application-Specific Integrated Circuits |

| BNN    | Binarized Neural Networks                |

| BER    | Bit Error Rate                           |

| CNN    | Convolutional Neural Network             |

| COTS   | Commercial Off-The-Shelf                 |

| CPU    | Central Processing Unit                  |

| CVV    | Candidate Vulnerability Values           |

| CVF    | Channel Vulnerability Factor             |

| DEF    | Data Extraction Form                     |

| DHA    | DNN Hardware Accelerator                 |

| DNN    | Deep Neural Network                      |

| DL     | Deep Learning                            |

| DMR    | Dual Modular Redundancy                  |

| DUE    | Detected Unrecoverable Error             |

| ECC    | Error Correction Code                    |

| EDAC   | Error Detection and Correction           |

| EDAC   | Error Distribution Map                   |

| FF     | Flip Flop                                |

| FPGA   | Field-Gate Programmable Logic            |

| FI     | Fault Injection                          |

| FIT    | Failure In Time                          |

| GAN    | Generative Adversarial Network           |

| GPU    | Graphical Processing Unit                |

| HDL    | Hardware Description Language            |

| HW     | Hardware                                 |

| HLS    | High-Level Synthesis                     |

| IC     | Integrated Circuits                      |

| IFMap  | Input Feature Map                        |

| IoT    | Internet of Things                       |

| ISA    | Instruction Set Architecture             |

| IVF    | Instruction Vulnerability Factor         |

| IP     | Intellectual Property                    |

| <br>KD | Knowledge Distillation                   |

| KVF    | Kernel Vulnerability Factor              |

| LSTM   | Long Short-Term Memory                   |

| LCU    | Lightweight Correction Unit              |

| LVF    | Layer Vulnerability Factor               |

| MAC    | Multiply-and-Accumulate                  |

| MBU    | Multi-bit Upset                          |

| MEA    | Mean Absolute Error                      |

| ML     | Machine Learning                         |

| MLP    | Multi-Layer Perceptron                   |

| mPA    | mean Average Precision                   |

| MTTF   | Mean Time to Failure                     |

|        |                                          |

| MWTF  | Mean Work To Failure                          |

|-------|-----------------------------------------------|

| MPSoC | Multi-Processor System-on-Chip                |

| NPU   | Neural Processing Unit                        |

| OFMap | Output Feature Map                            |

| OSR   | Open-Set Recognition                          |

| PE    | Processing Element                            |

| PC    | Personal Computer                             |

| PVF   | Program Vulnerability Factor                  |

| QNN   | Quantized Neural Network                      |

| RNN   | Recurrent Neural Network                      |

| RTL   | Register-Transfer Level                       |

| RQ    | Research Question                             |

| SA    | Systolic Arrays                               |

| SBU   | Single Bit Upset                              |

| SDC   | Silent Data Corruption                        |

| SER   | Soft Error Rate                               |

| SEU   | Single Bit Upset                              |

| SFI   | Statistical Fault Injection                   |

| SIHFT | Software Implemented Hardware Fault Tolerance |

| SIMD  | Single Instruction, Multiple Data             |

| SLR   | Systematic Literature Review                  |

| SM    | Streaming Multiprocessors                     |

| SW    | Software                                      |

| SoC   | System-on-Chip                                |

| TPU   | Tensor Processing Unit                        |

| TMR   | Triple Modular Redundancy                     |

| ViT   | Vision Transformers                           |

| VF    | Vulnerability Factor                          |

| VVSS  | Vulnerability Values Search Space             |

| VVR   | Vulnerability Value Range                     |

#### **1** Introduction

Computer science is one of the most prominent achievements of human life throughout history and has revolutionized all aspects of our activities, including but not limited to communications, manufacturing, business, education, transportation, etc. One of its most significant recent outcomes that is increasingly penetrating into various applications is Artificial Intelligence (AI). AI is an outstanding breakthrough in computer science that allows computer machines to acquire intelligence and perform decision-making as human does [172].

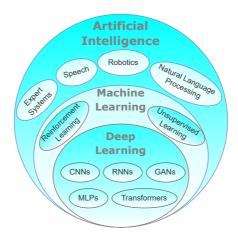

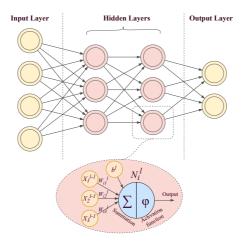

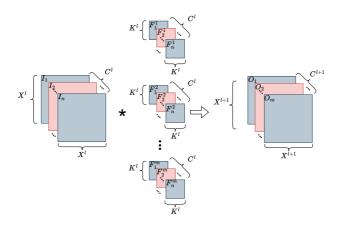

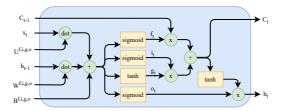

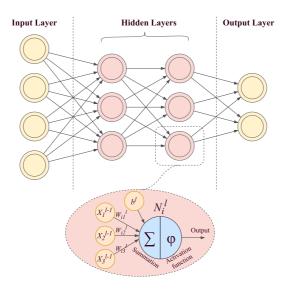

Machine Learning (ML) is a primary branch of AI that enables computer systems to gain the ability to learn and solve complex problems efficiently. Deep Neural Networks (DNNs) are brain-inspired algorithms that can learn and analyze complex patterns from data and provide highly accurate results for many complex tasks such as image classification, object detection, regression, signal processing, prediction, etc. [223]. Fig. 1.1 illustrates an overview of AI, ML, and Deep Learning (DL) and generally depicts their different branches and divisions based on [172].

Figure 1.1: An overview of AI, ML, and DL.

With the evolution of powerful processing systems in the recent decade, DNNs have emerged to be larger and deeper, employed in an ever broader extent of domains. Due to the high capabilities of DNNs in solving various tasks with a high accuracy, they are widely adopted in safety-critical applications [41, 84]. Safety is the avoidance of unacceptable risk. Risk is the probability of occurrence and the severity of a physical injury to the health of people as a result of the system failure [133]. Safety-critical applications refer to the use cases in which the failure of a system could result in consequences considered as *unacceptable* and affect the well-being of the people surrounding the system [134].

As AI and DNNs are increasingly leveraged in safety-critical applications such as automotive, space, healthcare, avionics, etc., the significance of safety is drawing more attention. In compliance with the US National AI Initiative Act [2] and the European Union's AI Act [6], any AI system that may pose a threat to people's health and safety must be rigorously evaluated and tested before deployment which reflects the importance of safety assessment for AI systems deployment. One of the Major concerns in designing a system for safety-critical applications is hardware reliability [190]. Hardware reliability is a characteristic of digital systems expressing the probability of perfectly performing their required function in given conditions within a time interval [37]. Hardware reliability is jeopardized by faults that can be caused by intrinsic characteristics of chips such as manufacturing defects, process variation, aging, or environmental issues such as radiation, temperature variation, and electromagnetic disturbances [41, 173, 213]. Faults influence logic circuits or memory cells of digital devices by altering their functionality during deployment, which may lead to a system failure [173]. By transistor scaling, the intrinsic fault rate of modern digital systems is drastically increasing, exacerbating their vulnerability to faults [120, 212].

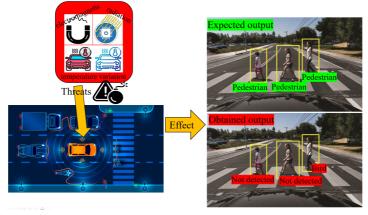

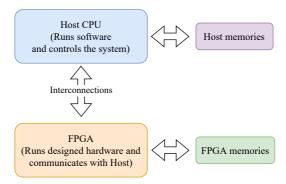

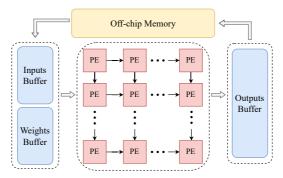

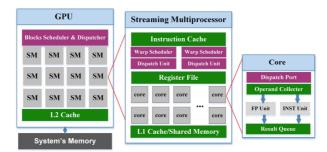

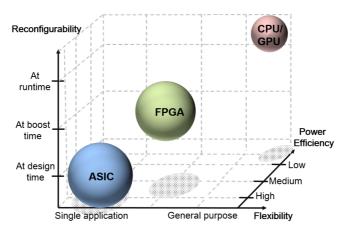

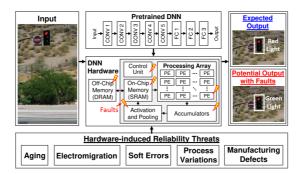

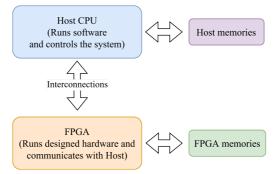

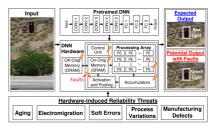

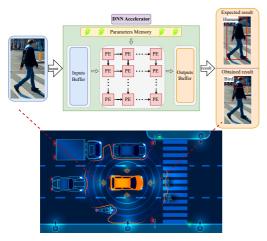

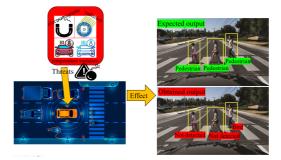

DNNs are deployed by various hardware devices and accelerators including Field-Programmable Gate Arrays (FPGAs), Application-Specific Integrated Circuits (ASICs), Graphics Processing Units (GPUs), and Central Processing Units (CPUs) [169, 227]. Hardware reliability of DNNs concerns the ability of DNN accelerators to operate correctly in the presence of faults during the deployment. Hardware faults can modify the operations or parameters of DNNs, producing errors that may propagate to their outputs and lead to misclassification, which may result in a catastrophe if safety-critical applications are concerned. It has been shown in several studies that DNNs are highly susceptible to faults and their accuracy can significantly drop with a few random bitflips [42, 80, 131]. As an example, Fig. 1.2 illustrates an autonomous vehicle possessing digital devices for executing DNNs to perform object detection. During the driving operation, faults influence the operations, and as a result, pedestrians are wrongly detected. Therefore, the vehicle continues driving and leads to a potentially fatal risk situation.

Figure 1.2: Potential impact of faults in DNN accelerators in a safety-critical application.

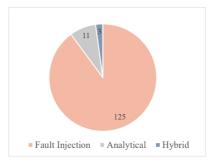

To address the hardware reliability concerns in DNN deployment, their fault resilience should be first assessed and then enhanced. *Reliability assessment* is the process of measuring the reliability of a modeled or presented system with quantitative evaluation metrics. It is the first step to achieving a fault-tolerant design and a reliable deployment. Generally, the reliability assessment of a system can be conducted by three methods: Fault Injection (FI), analytical, and hybrid methods [83]. In FI methods, faults are injected into the system implemented either in software or hardware, during the simulation or execution. In analytical methods, the function of the system and its reliability is mathematically modeled, based on the target architecture. In hybrid methods, a combination of FI and analytical methods is developed to estimate the reliability. Reliability assessment using

FI methods is generally more realistic and accurate than analytical and hybrid methods; however, FI is a non-scalable process with a high computational complexity and execution time [201].

Reliability assessment not only provides reliability measurement but also identifies the vulnerabilities in a DNN and its accelerator. *Reliability enhancement* is the process of mitigating the vulnerability of DNNs against hardware faults leading to a fault-tolerant design. Redundancy (in time, space, or data) is the key to achieving fault tolerance which can be applied at different levels of system abstraction from the software level down to the transistor level, depending on the application and system constraints [173, 190]. Reliability assessment and enhancement are tightly coupled to each other, necessitating an elegant and accurate process to ensure the safety of the system in deployment. In this thesis, some of the most significant challenges of reliability assessment and enhancement for DNNs are identified and addressed to enable extending the exploitation of DNNs in safetycritical applications with reliable deployment.

#### 1.1 Motivation

According to IBM's global AI adoption index in 2023 [5], 81% of enterprises in the automotive sector and 72% in the healthcare sector are either actively deploying AI or exploring its integration into their business operations. Furthermore, projections indicated that the AI global market size in the automotive industry will expand from USD 3.22 billion in 2023 to USD 35.7 billion by 2033 [4], while in the healthcare industry, it is expected to grow from USD 19.5 billion in 2023 to USD 490 billion by 2032 [3]. These numbers reflect the increasing need for AI as well as DNN deployment in the markets of safety-critical applications, and therefore, reliability assessment and enhancement are essential issues to address.

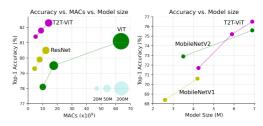

With the growth of DNN exploitation, the size of emerging DNNs in terms of the amount of parameters and computations is rapidly rising. Fig. 1.3 illustrates the size of emerging DNNs in terms of the number of parameters and Multiply-and-Accumulate (MAC) operations for CNNs [75] and Vision Transformers (ViT) [246]. It is observed that emerging DNNs possess billions of parameters and require billions of computations to achieve high accuracy. The gigantic size of DNNs places a huge complexity on their reliability assessment and enhancement, necessitating efficient and innovative solutions to reduce this complexity and overheads.

Several papers have been published on reliability assessment and enhancement in recent years [168, 220]. Due to the variety of DNN models and accelerators, different papers have considered their own customized setups to address their identified challenges. As the extent of DNNs and their accelerators is increasingly widening, their reliability study requires various techniques to enable specialized reliability assessment and enhancement. This diversity has led to an ambiguous space for researchers to comprehend the methods for hardware reliability assessment of DNNs and their accelerators. Therefore, a Systematic Literature Review (SLR) is required to allow comprehension of the essentials of studying the reliability of DNNs. Throughout the literature, there is no survey characterizing existing solutions for the reliability assessment of DNNs, hindering researchers from identifying the challenges and gaps in this area and addressing them.

By overviewing the literature, it can be observed that the hardware reliability of DNNs is mainly assessed by the means of FI [203]. However, given the huge size of emerging DNNs and the complexity of their accelerators, FI is prohibitively complex and impractical. Achieving statistically high-confident results using FI requires weeks and months of simulations by powerful GPUs [200]. Therefore, one of the main challenges in the literature is to tackle the high complexity of FI by devising alternative scalable methods for

(b) Vision Transformers (ViT) [246]

Figure 1.3: Growing size of emerging DNN models regarding their computations and memory requirements.

evaluating and quantifying the fault resilience of DNNs.

DNNs are inherently resilient to faults and they can mask a huge amount of faults, yet their accuracy is considerably compromised by faults [147, 176]. Fault tolerance can be achieved by redundancy either at hardware or software levels [135]. As mentioned, hardware devices, including general-purpose processors (e.g., CPUs and GPUs) and specialized accelerators (e.g., FPGAs and ASICs), are exploited to efficiently deploy DNNs [169]. Safety-critical applications such as autonomous vehicles are characterized as edge applications where the processing of data is performed at the edge of the network instead of exploit-ing external service providers as in cloud computing [167]. In many cases in edge AI applications, hardware accelerators are not configurable and it is not conceivable to modify the underlying hardware to enhance the fault tolerance of the deployed DNNs; especially with the general purpose accelerators as well as with off-the-shelf Integrated Circuits (ICs) and hard cores. In these cases, fault tolerance can be achieved by Software-Implemented Hardware Fault Tolerance (SIHFT) [98]. In the case of DNNs, it can be obtained by introducing redundancy to the DNN models' architecture (e.g., parameters, functions, and operations) without redesigning the underlying hardware.

On the other hand, achieving fault tolerance through redundancy lays overhead to the system pertaining to the DNN's memory footprint and execution performance [123, 213]. Whereas hardware accelerators in edge computing pose several constraints in terms of latency, power, and memory size [167]. Therefore, the trade-off between DNNs' reliability and memory/performance is a crucial consideration in DNNs fault tolerance. Conventional fault-tolerant techniques such as Triple Modular Redundancy (TMR) or Dual Modular Redundancy (DMR) introduce a massive overhead to DNNs which are already gigantic, making them inefficient compared to their effectiveness. Therefore, there is a need for

cost-effective model-level approaches to enhance the fault resilience of DNNs.

#### **1.2 Problem Formulation and Research Questions**

In the frame of this thesis, the objective is to identify the major challenges in the literature concerning hardware reliability assessment and enhancement for DNNs in safety-critical applications. In this regard, four problems (P) are identified as follows:

- P1. Ambiguity in the reliability assessment literature for DNNs: Due to the variety of DNNs and accelerators, there exists a wide range of research papers with distinct methods evaluating the reliability of DNNs and their accelerator. Because of the extent of the domain, researchers approach the problem of the reliability of DNNs from various perspectives. We are confronted with a multitude of DNN applications as well as a variety of DNN architectures and accelerators for different tasks. This variety creates an ambiguous research area, restraining researchers from precisely identifying and comprehending the gaps in the literature. Multiple factors affect the variety of reliability evaluations of DNN accelerators leading to different ways of assessment methods and experiments: DNN architectures, hardware accelerators, system abstraction level, and fault models. Existing surveys [123, 168, 203, 213, 220, 229] focus on reliability enhancement methods but there is no comprehensive survey for reliability assessment methods. To tackle this ambiguity in the literature, there is a need for a comprehensive literature review to characterize the existing methods and identify the gaps. The Research Questions (RQ) regarding this problem are as follows:

- RQ1.1. What are the existing methods in this domain?

- RQ1.2. How could the existing methods be characterized?

- **RQ1.3.** What are the open challenges in this domain?

- P2. Scalability of reliability assessment: Fault injection is the major method that is employed for hardware reliability assessment for CNNs. It is a realistic method and provides the possibility of modeling various fault types and injecting them at diverse system abstraction levels from software down to RTL level. Nonetheless, since emerging CNNs are gigantic and their accelerators are complex, FI's non-scalability leads to an obstacle to reliability assessment. Achieving high-confidence and accurate results by FI for CNNs takes weeks and months. On the other hand, existing analytical resilience analysis methods for DNNs [27, 28, 161, 206, 210, 237] could not tackle this gap in the literature. Although they are faster than FI, they do not quantify reliability and are not as accurate as FI. To our knowledge, there is no scalable, fast, and accurate approach to reliability assessment for CNNs. The RQs regarding this problem are as follows:

- **RQ2.1.** How to quantify the reliability of emerging CNNs as accurately as FI?

- **RQ2.2.** How to obtain the reliability of fine-grain components of CNNs and identify the more vulnerable ones?

- **RQ2.3.** How to perform a scalable and fast resilience analysis yet accurate for emerging CNNs?

- **RQ2.4.** How to apply the resilience analysis outputs for optimized resilience assessment or enhancement methods?

■ P3. Costly fault tolerance: Fault-tolerant techniques for CNN accelerators are carried out at the architecture and algorithm level [168]. Architecture-level techniques are accelerator-specific and exploit hardware redundancy with performance and memory overhead and they do not apply to general-purpose processors and predesigned IPs. Meanwhile, algorithm-level techniques modify the CNN models in software that any accelerator executes. Throughout the literature, several cost-effective algorithm-level fault tolerance techniques for enhancing the reliability of CNNs are presented [49, 53, 93, 113, 143, 247, 252], yet they are either too complex, or induce considerable overhead, or provide low fault resilience compared to the induced overhead. Therefore, there is a need for low-overhead model-level approaches for CNNs to significantly enhance their deployment reliability. The corresponding RQs concerning this problem are as follows:

- **RQ3.1.** How to effectively enhance the fault tolerance for off-the-shelf CNN accelerators?

- RQ3.2. How to provide high fault resilience for CNNs with minimal overheads?

- **RQ3.3.** How to allow trade-off controllability over resilience vs. overhead based on the application's constraints?

- P4. Missing the study of reliability for Recurrent Neural Networks (RNNs): Throughout the literature, numerous papers extensively examined the reliability assessment and enhancement of feed-forward DNNs [123, 220]. Nonetheless, the reliability of RNNs, in particular Long Short-Term Memory (LSTM) DNNs, is not explored. However, they are widely deployed in safety-critical applications, particularly in healthcare for diagnosis, treatment, and prediction of diseases and anomalies [165]. Therefore, there is a gap in the literature on the impact of faults on LSTMs and how to improve their fault resilience. The research questions pertaining to this problem are as follows:

- RQ4.1. How vulnerable are LSTM-based DNNs to faults?

- **RQ4.2.** How to improve their resilience against faults with a low overhead?

#### **1.3 Contributions**

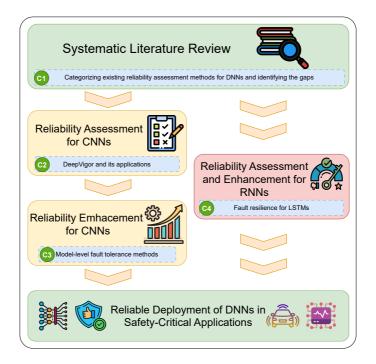

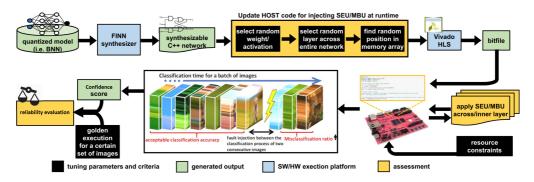

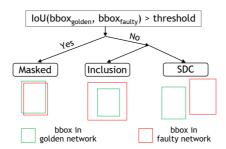

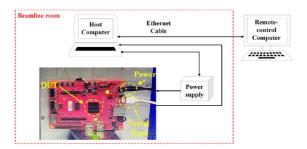

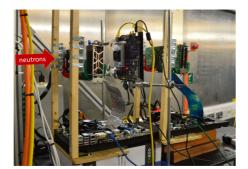

This thesis attempts to address the identified problems in the research domain and the raised research questions. Fig. 1.4 summarizes the contributions of this dissertation with respect to the aforementioned problems, that go beyond state-of-the-art as follows:

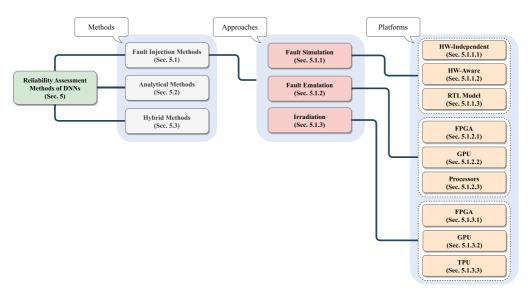

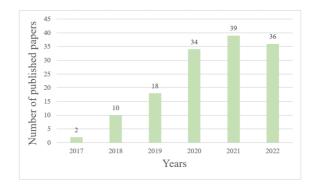

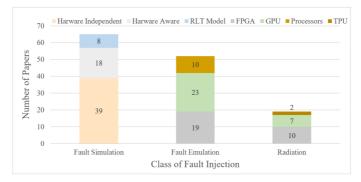

■ C1. Systematic literature review on hardware reliability assessment for DNNs: To address *P1* and *RQ1.1-RQ1.3*, the first Systematic Literature Review (SLR) focused exclusively on all methods of reliability assessment of DNNs is conducted. This study establishes a comprehensive picture of the reliability assessment methods for DNNs and systematically reviews the pertinent literature. The primary objective of this review is to explore the methods of reliability assessment for DNNs, generalize and classify them, and identify the existing challenges in the field. To the best of our knowledge, this survey constitutes the first in-depth literature review concerning reliability assessment methods for DNNs. The review encompasses all relevant papers published from 2017 to 2022, identified through a systematic search. The key highlights of this contribution which is based on paper I are:

Figure 1.4: An overview of the contributions of the thesis.

- Presenting a thorough and systematic survey on the reliability assessment methods for DNNs;

- Analyzing publication trends across different years and methods;

- Classifying and characterizing reliability assessment methods for DNNs;

- Categorizing fault injection methods based on the DNN hardware platforms;

- Introducing analytical and hybrid reliability assessment methods as alternatives to FI;

- Highlighting open challenges in the field and proposing recommendations for future research.

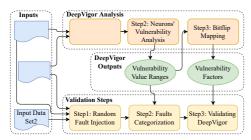

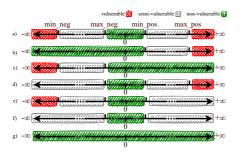

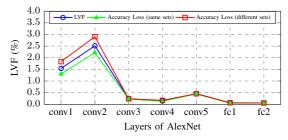

- C2. Scalable, fast, and accurate resilience analysis for CNNs: This contribution addresses P2 and RQ2.1-RQ2.4 by introducing novel semi-analytical methods for reliability assessment of CNNs, DeepVigor and its optimized version DeepVigor+. In this thesis's contribution, the concept of neurons' vulnerability ranges is first introduced in DeepVigor, which indicates whether a fault in the output of neurons would lead to a CNN misclassification. This enables a comprehensive reliability study through a novel resilience analysis method, where Vulnerability Factors (VF) of layers, neurons, and bits within CNNs are derived. The key highlights of this contribution, which is based on paper II, are as follows:

- Proposing DeepVigor, an innovative, metric-oriented, and accelerator-agnostic resilience analysis method for CNNs that is faster than FI with comparable accuracy;

- Introducing and calculating vulnerability ranges for all neurons in CNNs, supported by a fault propagation analysis, resulting in accurate categorization of critical/non-critical faults;

- Providing fine-grain VF as reliability quantification metrics for layers, neurons, and bits in CNNs, validated through comparison with fault injection;

The DeepVigor method is further optimized as DeepVigor+ to overcome the scalability challenges in reliability analysis. DeepVigor+ leverages an optimal fault propagation analysis across neurons and entire CNNs to acquire VFs in an optimized manner. To the best of our knowledge, DeepVigor+ represents the first scalable semi-analytical alternative to FI with a comparable accuracy for resilience analysis of CNNs in the literature. Additionally, DeepVigor+ is made available as an open-source tool, facilitating reliability analysis for emerging CNNs and enabling researchers to quickly evaluate CNNs' reliability and design fault-tolerant CNNs. The key highlights of this contribution which is based on paper III, are as follows:

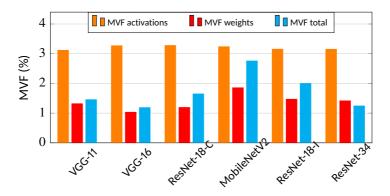

- Introducing DeepVigor+, a scalable, fast, and accurate resilience analysis for deriving VFs for CNNs' layers and models by analyzing both parameters and activations and utilizing an optimal error propagation analysis;

- Employing a novel statistical approach in DeepVigor+ based on stratified sampling, enabling fast and accurate resilience analysis for emerging CNNs.

Furthermore, QDeepVigor is an extended version of DeepVigor for Quantized Neural Networks (QNNs) and its analysis results are exploited for various purposes:

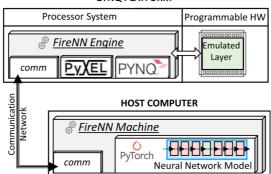

- Cross-layer reliability enhancement for QNNs accelerators: In this work, which is based on paper IV, the more critical neurons in a QNN are identified by QDeepVigor and are split into two equivalent neurons. Then a Lightweight Correction Unit (LCU) is designed for Systolic Arrays (SAs) to correct faults in the identified critical neurons. The results indicate the same fault resilience as TMR with half overhead;

- A hybrid method for QNNs' reliability assessment: In this work, which is based on paper IX, QDeepVigor is exploited to prune the fault space using the vulnerability value ranges for neurons in QNNs executing on an SA. This hybrid reliability assessment method leads to a significant speed-up in fault simulation.

- C3. Cost-effective model-level fault-tolerance for CNNs: This contribution attempts to address *P3* and *RQ3.1-RQ3.3* by proposing model-level fault tolerance methods for CNNs as SIHFT-based techniques. In the first method, a novel low-cost activation restriction method, called ProAct, is introduced and combined with progressive training based on Knowledge Distillation (KD) [112] to achieve significant resilience in CNNs with minimal memory overhead. The source code for ProAct, along with other state-of-the-art activation restriction methods, is published and made publicly accessible for researchers for the first time. The key highlights of this work which is based on paper V, are as follows:

- Proposing Hybrid Clipped ReLU (HyReLU) activation function, which restricts activation values by trainable threshold parameters in a neuron-wise manner at the last layer and operates layer-wise in the other layers of CNNs;

• Introducing progressive training to acquire clipping thresholds in HyReLU for each layer individually, resulting in more optimal and effective clipping threshold values that ensure high resilience for CNNs.

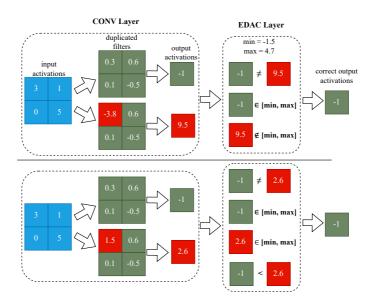

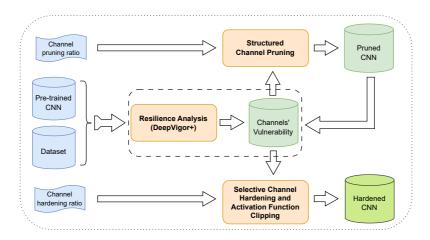

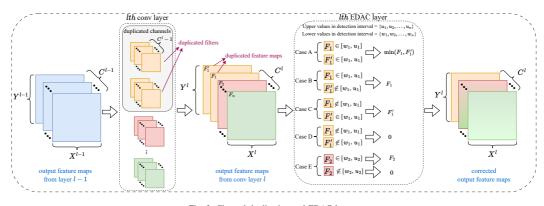

The second method introduces an innovative model-level hardening solution that modifies the architecture of CNNs to inherently enable fault correction during inference. An efficient error correction mechanism is designed, achieved by selectively duplicating channels within the CNNs structure. In this approach, the vulnerability of the weight channels of CNNs is analyzed, and the most vulnerable ones are duplicated. Subsequently, a correction layer detects and corrects erroneous outputs based on duplicated values. The key highlights of this work, which is based on paper VI, are as follows:

- Proposing a model-level hardening method for CNNs to improve their fault tolerance during inference. The approach involves duplicating parameters in most vulnerable channels and integrating an efficient Error Detection and Correction (EDAC) layer to correct erroneous feature maps;

- Introducing a channel pruning technique based on the parameter vulnerability, allowing significant reductions in the overhead associated with the hardening technique;

- providing a set of user-defined constraints based on the application to manage the trade-off between performance and memory overheads vs. the expected fault resilience.

Eventually, all proposed methods for reliability assessment and enhancement of CNNs in this thesis, are integrated into the SentinelNN framework. This open-source framework obtains channel vulnerability factors for CNN models using DeepVigor+ to perform vulnerability-aware pruning and hardening. SentinelNN hardens the CNN models by incorporating selective channel duplication and correction as well as activation restriction.

- C4. Low-overhead resilience assessment and enhancement for LSTMs: This contribution addresses *P4* and *RQ4.1-RQ4.2* by analyzing and improving the fault resilience of LSTMs for healthcare applications. To our knowledge, this gap is addressed for the first time. The key highlights of this contribution which is based on papers VII and VIII, are as follows:

- Conducting a comprehensive analysis of the resilience of various LSTM-based DNNs using fault injection into their parameters;

- Proposing multiple fault-tolerant techniques for LSTM-based DNNs, resulting in remarkably mitigating the impact of faults on LSTM-based DNNs;

#### **1.4 Thesis Organization**

This thesis consists of 7 Chapters. Chapter 2 presents a thorough background on the theoretical aspects of the dissertation. It discusses the definition and concept of hardware reliability and explains the impacts of hardware faults and soft errors and how they can be measured and mitigated. Furthermore, the basics of DNNs and their accelerators are presented. Chapter 3 presents a systematic literature review on the reliability assessment methods for DNNs. This Chapter thoroughly categorizes the existing methods and identifies the gaps in the literature. Chapter 4 presents a novel scheme for fault resilience analysis for CNNs, called Deep-Vigor, and tackles the scalability of conventional methods based on fault injection. Deep-Vigor is exploited not only for fault resilience but also for fault enhancement of accelerators. Chapter 5 proposes SIHFT-based methods for enhancing the fault resilience of CNNs, beyond state-of-the-art. It presents ProAct for optimal activation restriction with a minimal overhead. Furthermore, this Chapter introduces EDAC layers accompanied by selective channel-duplication in CNNs, which is facilitated by vulnerability-aware pruning for a cost-effective fault tolerance in CNNs. This Chapter also introduces the SentinelNN framework that integrates the proposed methods for reliability assessment and enhancement in this dissertation. In the following, Chapter 6 investigates fault resilience assessment and enhancement for various LSTM-based DNNs. Finally, Chapter 7 concludes the thesis.

#### 2 Background

To convey the essence of this thesis, several concepts must be explained. This Chapter presents the theoretical and technical background for the thesis in detail.

#### 2.1 Hardware Reliability

The rapid increase in software and hardware complexity has been driven by the tremendous advances in electrical and computer technology in the past century. The growth of microelectronics is generally associated with the evolution of the microprocessor, often described as "Moore's Law". Moore predicted that chip complexity would double every two years, which has been on track for the past decades [228]. In this context, transistor miniaturization has resulted in high-performance computing systems, which are also expected to operate safely and reliably.

Since microelectronics have permeated all aspects of our daily lives, it is crucial to employ them safely and reliably. However, several threats can compromise their safety and reliable operation. Hardware faults are a major threat to the safety of digital devices, especially in their safety-critical applications. The following subsections describe the concept of hardware reliability, its associated threats (hardware faults), and methods to evaluate and improve it.

#### 2.1.1 Definition and Concept

Hardware reliability of a system is defined as the probability that no failure or user-visible error occurs in its functional operation over a given period [37, 173, 214]. Reliability is a function of time and represents the likelihood that a system can operate as intended for a specific duration. As stated in reference [173], reliability is expressed as R(t) = P(T > t), where *T* denotes the lifetime of a system. If a population of  $N_0$  identical systems is considered, R(t) is equal to the fraction of the systems that survive beyond time *t*. Supposing  $N_t$  is the number of survived systems until time *t*, and E(t) is the number of systems that encountered errors in the interval (0, t], then, reliability can be expressed as Eq. (2.1).

$$R(t) = \frac{N_t}{N_0} = \frac{N_0 - E(t)}{N_0} = 1 - \frac{E(t)}{N_0}$$

(2.1)

Differentiating Eq. (2.1) yields the instantaneous error rate i.e., hazard rate h(t) which is defined as the probability that a system experiences an error during a time interval  $\Delta t$ , given that it has prevailed until time t. It means that h(t) is the probability of an error occurring in the time interval (t, t+t]. Therefore, we can extend the mathematics as noted in Eq. (2.2) [173].

$$\frac{dR(t)}{dt} = -\frac{\frac{dE(t)}{dt}}{N_0}$$

$$h(t) = P(t < T < t + \Delta t | (T > t)) = -\frac{\frac{dE(t)}{dt}}{N_t} = \frac{-\frac{E(t)}{N_0}}{\frac{N_t}{N_0}} = \frac{dR(t)}{R(t)}$$

$$\Rightarrow \frac{dR(t)}{dt} = -h(t)R(t)$$

(2.2)

The solution to this differential equation is written in Eq. (2.3) [173].

$$R(t) = e^{-\int h(t)dt}$$

(2.3)

Assuming that h(t) has a constant failure rate ( $\lambda$ ) during its useful lifetime phase and the system is not affected by aging, the reliability of the system can be expressed as Eq. (2.4) [173].

$$R(t) = e^{\lambda t} \tag{2.4}$$

To elaborate on the concept of reliability, we refer to an example from [214]. Consider 50 systems being tested over 1,000 hours, with two failures occurring during the test. The probability of failure,  $P_f$ , for this system over 1,000 hours of operation is calculated as  $P_f(1,000) = \frac{2}{50} = 0.04$ . The probability of success, known as the reliability R, is given by  $R(1,000) = 1 - P_f(1,000) = 0.96$ . The failure rate,  $f_r$ , for this system is  $f_r = \frac{2}{50 \times 1,000} = 4 \times 10^{-5}$ , representing the probability of failure of an instance for an individual system in 1,000 hours of operation. Using the reliability function in Eq. (2.4):

$$R(1,000) = e^{-4 \times 10^{-5} \times 1,000} = 0.96$$

(2.5)

which is consistent with the previous calculation.

#### 2.1.2 Hardware Faults: Definition, Classification, and Impact

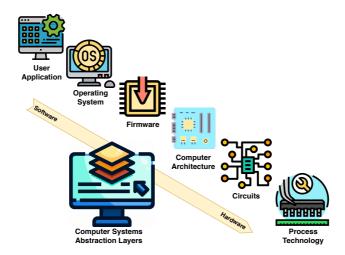

In a computer system, the abstraction layers are generally divided into six broad categories, organized from top (software) to bottom (hardware), as shown in Fig. 2.1: user application, operating system, firmware, architecture, circuits, and process technology. Faults typically originate at the process technology or within the silicon chip itself. Hardware faults can result from manufacturing defects in a silicon chip or environment interactions such as bitflips caused by cosmic ray strikes [173].

Figure 2.1: Abstraction layers of computer systems, inspired by [173].

Faults are generally categorized into three classes: permanent, intermittent, and transient. Permanent faults persist indefinitely until a correction mechanism is applied, such as oxide wearout leading to a transistor failure in a silicon chip. Intermittent faults repeatedly show up and vanish, as seen in the case of partial oxide wearout. Transient faults, on the other hand, appear briefly and then disappear, such as bitflips in memory or gate malfunctions in logic caused by alpha particles or neutron strikes [173]. Hardware faults may not always result in a user-visible error for two reasons. First, a fault may be masked in an intermediate layer; for instance, a defective transistor caused by oxide wearout might impact performance but not disrupt the correct functioning of the architecture. Second, different layers within the system might be designed with fault tolerance. For example, radiation-hardened cells can detect and recover from faults in transistors. Each abstraction layer in Fig. 2.1 can thus be designed to handle faults originating from lower layers. If a fault is managed at a specific layer, it prevents errors from propagating to higher layers [173].

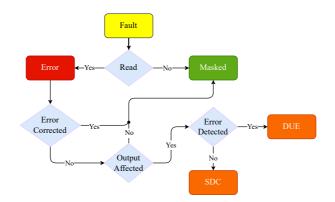

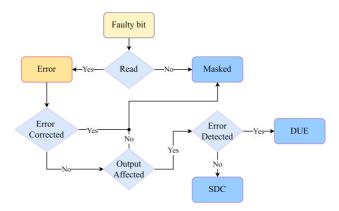

*Errors* are the observable consequences of faults. While faults are necessary for errors to occur, not all faults manifest as errors, particularly if they are masked or tolerated. *Failure* refers to a system malfunction that prevents the system from meeting its expected correct outputs. A failure is essentially a specific case where an error becomes visible to the user. Fig. 2.2 illustrates the impact of faults on a system's output. As depicted, when a fault occurs, it is considered *masked* if the affected bit or transistor is not read, or if the corresponding error is corrected. If the fault leads to a user-visible error, it manifests as a *Silent Data Corruption (SDC)*, i.e., failure. If it is detected but not corrected it appears as a *Detected Unrecoverable Error (DUE)*, which may lead to temporary system unavailability [173]. As mentioned in [98], failure's consequences can be categorized in four grades:

- Benign: No major impact on the system's task or performance,

- *Significant*: The system's task is disrupted, leading to reduced efficiency of the delivered service,

- Serious: The system's task is severely disrupted,

- *Catastrophic*: The system's task is completely halted, resulting in the destruction of the controlled process or causing human injury or death.

Figure 2.2: Faults impact on the output of a system, inspired by [173].

#### 2.1.3 Soft Errors: Origination and Impact

Transient faults in semiconductor devices can occur due to various factors, including transistor variability, thermal cycling, erratic fluctuations in the minimum operational voltage of a circuit, and soft errors caused by external radiation. Transistor variability stems from random dopant fluctuations, sub-wavelength lithography, and high heat flux amongst the silicon die. Thermal cycling results from repeated stress due to temperature variations. Erratic fluctuations in the circuit's minimum voltage can occur as a result of gate oxide soft breakdown combined with high gate leakage [173].

Radiation-induced soft errors are a significant threat to system reliability and can lead to circuit malfunctions or system crashes. Soft errors occur when data is corrupted, whereas the device itself remains undamaged. These errors are difficult to trace or identify as the root cause of system malfunctions through failure analysis. Therefore, it is crucial to mitigate their effects in the system design. In terrestrial applications, the primary sources of soft errors are neutrons and alpha particles, produced by cosmic radiation, solar activities, etc. When these high-energy particles strike transistors, they induce energy, generating a current pulse that can result in an upset in transistors [178].

Radiation impacts semiconductors from sea level to space, with neutron flux intensifying at higher altitudes. Consequently, space applications face the highest risk, while terrestrial applications are at a lower risk. It is estimated that the average terrestrial neutron flux that can potentially lead to soft errors is 14  $\frac{neutrons}{cm^2.hour}$ . On the other hand, at the altitude of 10 km, neutron flux increases by a factor of 228 compared to sea level. This highlights that digital devices are exposed to soft errors at any altitude, stressing the need for fault tolerance mechanisms, particularly for safety-critical applications [173].

As mentioned, a transistor can collect charge from an alpha particle or a neutron strike. When this charge exceeds the circuit's threshold at the gate or cell level, it results in a bitflip. In memory devices, a transient fault occurs when a bit stored in a cell flips. However, in logic devices, a transient fault is only considered to occur when this fault propagates to a forward latch or storage cell. These bitflips are classified as Single-Event Effects (SEEs), which may impact single or multiple bits in memory cells or latches. For a bitflip and subsequent malfunction to occur, the accumulated charge in a cell or circuit must exceed a minimum threshold, known as the critical charge [173].

Transistor scaling has a remarkable impact on the susceptibility of transistors to soft errors due to its effect on the critical charge. For instance, the Soft Error Rate (SER) in SRAMs increases by a factor of 6-7 from 130 *nm* to 22 *nm* process [120]. This indicates that emerging digital systems are becoming increasingly susceptible to soft errors. SER refers to the rate at which soft errors occur in a device within a specific environment. The SER is measured in Failure In Time (FIT), where one FIT is equal to one failure in  $10^9$  device hours [178].

#### 2.1.4 Fault Tolerance Techniques

Fault-tolerant computing refers to the ability to maintain correct computation despite the presence of errors in a system, thus enhancing reliability. Achieving fault tolerance primarily involves leveraging and managing redundancy. Redundancy is the property of having an excess of resources beyond the minimum required to perform a task. When failures occur, this redundancy is utilized to mask or bypass the failures, ensuring the system continues to operate at the intended level of functionality [135, 214].

Redundancy can be exploited in different methods at the hardware or software level, in spatial and temporal ways. Hardware redundancy is provided by incorporating extra hardware into the design to either detect or override the effects of a failed component. For example, instead of having a single processor, we can use two or three processors, each performing the same function. By having two processors (Dual Modular Redundancy-DMR), we can detect the failure of a single processor; by having three (Triple Modular Redundancy-TMR), we can use the majority output to override the wrong output of a single faulty processor. These forms of hardware redundancy incur high overheads, and their use is therefore normally reserved for critical systems where such overheads can be justified [135].

Information redundancy encompasses techniques such as Error Detection and Correction Codes (ECCs) or Algorithm-Based Fault Tolerance (ABFT). ECCs utilize additional bits, i.e., check bits, which are appended to the original data to enable the detection and potential correction of errors. On the other hand, ABFTs integrate redundant computations into algorithms to detect, locate, and correct errors caused by hardware faults during normal operations. Both ECCs and ABFTs are widely employed in memory units and storage devices to protect against benign failures. However, they often necessitate additional hardware to handle the processing of redundant data [135, 235].

Processing components can exploit time redundancy by re-executing the same program, primarily to counteract transient faults. Since most hardware faults are transient, it is unlikely that successive executions will encounter the same fault. This makes time redundancy an effective method for detecting transient faults that might otherwise remain undetected. Additionally, it can be employed when other error detection mechanisms are available, allowing the system to recover from a fault and repeat the computation. While time redundancy imposes significantly lower hardware and software overhead compared to other methods, it lays a substantial performance cost [135].

Software Implemented Hardware Fault Tolerance (SIHFT) refers to a set of techniques that exploit redundancy at the software level to detect and correct hardware faults, without requiring modifications to the hardware design. SIHFT offers a cost-effective alternative to traditional hardware or information redundancy approaches and is particularly beneficial when using Commercial Off-The-Shelf (COTS) microprocessors or predesigned IP cores, which typically lack native or strong error detection and correction capabilities. In SIHFT, the software not only performs its primary designed functions and requirements, but also incorporates monitoring functions to detect, signal, and correct hardware errors when they occur [98, 135].

#### 2.1.5 Evaluation and Metrics