# **DOCTORAL THESIS**

# Photovoltaic String Converter with Universal Compatibility with AC and DC Microgrids

Oleksandr Matiushkin

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2022

# TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 27/2022

# Photovoltaic String Converter with Universal Compatibility with AC and DC Microgrids

**OLEKSANDR MATIUSHKIN**

#### TALLINN UNIVERSITY OF TECHNOLOGY

School of Engineering

Department of Electrical Power Engineering and Mechatronics

This dissertation was accepted for the defence of the degree 17/05/2022

**Supervisor**: Prof. Dmitri Vinnikov

Department of Electrical Power Engineering and Mechatronics

Tallinn University of Technology

Tallinn, Estonia

**Co-supervisor**: Dr. Oleksandr Husev

Department of Electrical Power Engineering and Mechatronics

Tallinn University of Technology

Tallinn, Estonia

Opponents: Prof. Pavol Bauer

Department of Electrical Sustainable Energy

Delft University of Technology

Delft, Netherlands

Prof. Sergiy Peresada

Department of Electromechanical Systems Automation and Electrical Drives

National Technical University of Ukraine "Kyiv Polytechnic Institute"

Kyiv, Ukraine

Defence of the thesis: 17/06/2022, Pärnu

#### **Declaration:**

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for a doctoral or equivalent academic degree.

Oleksandr Matiushkin

-----signature

Copyright: Oleksandr Matiushkin, 2022

ISSN 2585-6898 (publication)

ISBN 978-9949-83-839-4 (publication)

ISSN 2585-6901 (PDF)

ISBN 978-9949-83-840-0 (PDF) Printed by Koopia Niini & Rauam

# TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 27/2022

# Alalis- ja vahelduvvoolu mikrovõrkudega ühilduv universaalne muundur päikese- elektrijaamadele

**OLEKSANDR MATIUSHKIN**

# Contents

| List of Publications                                                                         | 7    |

|----------------------------------------------------------------------------------------------|------|

| Author's Contribution to the Publications                                                    | 8    |

| Abbreviations                                                                                | 9    |

| Symbols                                                                                      | 10   |

| 1 Introduction                                                                               | 13   |

| 1.1 Background                                                                               | 13   |

| 1.2 Motivation of the Thesis                                                                 |      |

| 1.3 Aims, Hypothesis and Research Tasks                                                      |      |

| 1.4 Research Methods                                                                         |      |

| 1.5 Contributions and Disseminations                                                         |      |

| 1.6 Experimental Setup and Instruments                                                       |      |

| 1.7 Thesis Outline                                                                           | 18   |

| 2 Concept of the Universal dc-dc/ac Converters                                               |      |

| 2.1 Protection Issue                                                                         |      |

| 2.1.1 Grounding Issue                                                                        |      |

| 2.1.2 Output Filter Selection in Terms of Protection                                         |      |

| 2.2 Summary                                                                                  |      |

| 3 Application Oriented Design                                                                |      |

| 3.1 Design of the Filters                                                                    |      |

| 3.2 Verification of the Filter Design                                                        |      |

| 3.2.1 Special Modulation Techniques                                                          |      |

| 3.3 Summary                                                                                  |      |

|                                                                                              |      |

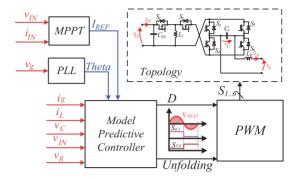

| 4 Model Predictive Control as a Feasible Solution for Industrial Application                 |      |

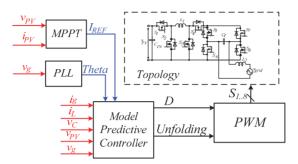

| 4.1 MPC for Twisted Buck-Boost Inverter Based on the Unfolding Circuit                       |      |

| 4.1.2 Cost Function Based on the Input Inductor Current                                      |      |

| 4.2 Summary                                                                                  |      |

| ·                                                                                            |      |

| 5 Technology Demonstrator of the Universal Converter                                         |      |

| 5.1 Control and Measurement System5.2 Twisted Buck-Boost Inverter Based on Unfolding Circuit |      |

| 5.2.1 Solving of Zero Crossing Distortion                                                    |      |

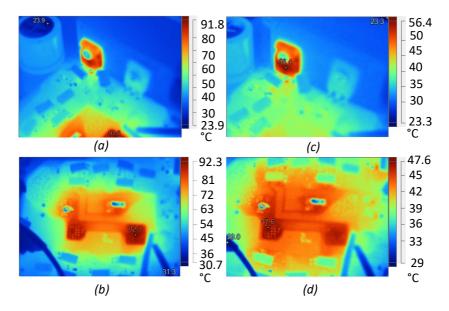

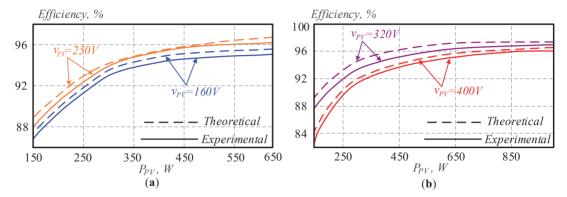

| 5.2.2 Efficiency Estimation                                                                  |      |

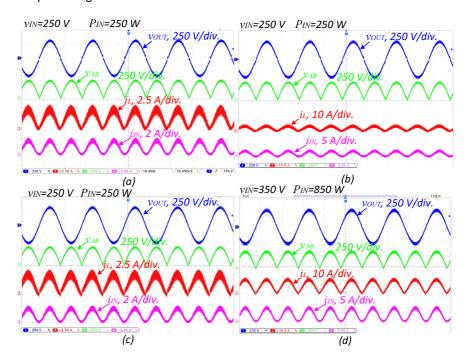

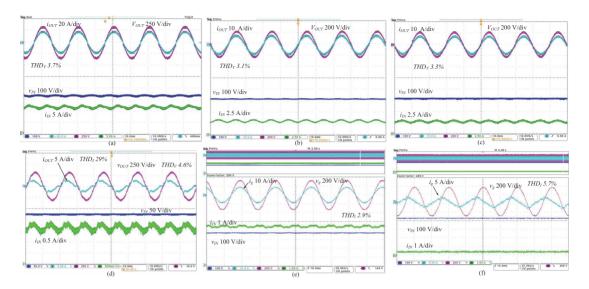

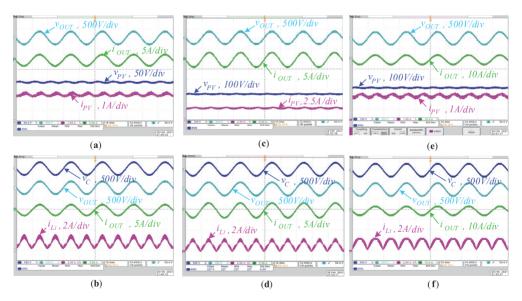

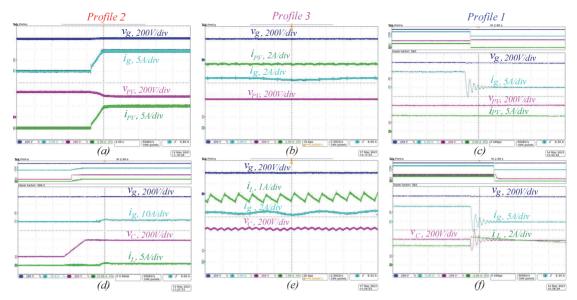

| 5.2.3 Experimental Results of Grid-Connected System                                          |      |

| 5.3 Buck-Boost Inverter Based on Unfolding Circuit                                           |      |

| 5.3.1 Dc-ac Mode                                                                             |      |

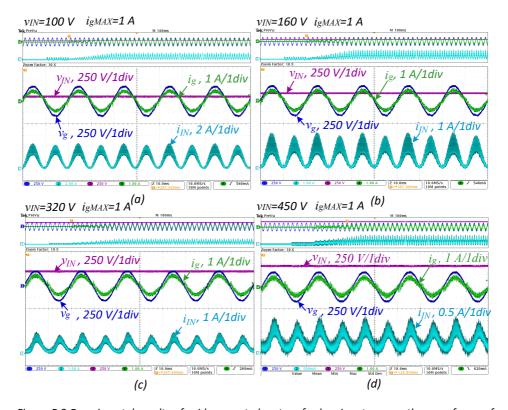

| 5.3.2 Dc-dc Mode                                                                             | . 59 |

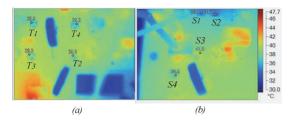

| 5.3.3 Efficiency Study                                                                       |      |

| 5.4 Summary                                                                                  | . 63 |

| 6 Conclusions                                                                                | . 64 |

| List of Figures                                                                              | . 65 |

| List of Tables                                                                               | 68   |

| References                                                                                   | 69   |

| Acknowledgements | 74  |

|------------------|-----|

| Abstract         | 75  |

| Lühikokkuvõte    | 76  |

| Appendix         | 77  |

| Curriculum vitae | 177 |

| Flulookirieldus  | 178 |

#### **List of Publications**

The following is a list of author's publications, on the basis of which the thesis has been prepared:

- [PAPER-I] O. Husev, O. Matiushkin, C. Roncero-Clemente, F. Blaabjerg, D. Vinnikov, "Novel Family of Single-Stage Buck-Boost Inverters Based on Unfolding Circuit," *IEEE Trans. on Pow. Electron.*, vol. 34, no. 8, Aug. 2019. DOI: 10.1109/TPEL.2018.2879776.

- [PAPER-II] O. Husev, O. Matiushkin, D. Vinnikov, C. Roncero-Clemente, S. Kouro, "Novel Concept of Solar Converter with Universal Applicability for DC and AC Microgrids," *IEEE Trans. on Ind. Electron.*, vol. 69, no. 5, May 2022. DOI: 10.1109/TIE.2021.3086436.

- [PAPER-III] O. Matiushkin, O. Husev, J. Rodriguez, H. Young, I. Roasto, "Feasibility Study of Model Predictive Control for Grid-Connected Twisted Buck-Boost Inverter," *IEEE Trans. on Ind. Electron.*, vol. 69, no. 3, Mar. 2022. DOI: 10.1109/TIE.2021.3068663.

- [PAPER-IV] A. Fesenko, O. Matiushkin, O. Husev, D. Vinnikov, R. Strzelecki, P. Kołodziejeko, "Design and Experimental Validation of a Single-Stage PV String Inverter with Optimal Number of Interleaved Buck-Boost Cells," open access Energies, Apr. 2021. https://doi.org/10.3390/en14092448.

- [PAPER-V] O. Husev, O. Matiushkin, C. Roncero-Clemente, D. Vinnikov, V. Chopyk, "Bidirectional Twisted Single-Stage Single-Phase Buck-Boost DC-AC Converter," open access Energies, Sep. 2019. https://doi.org/10.3390/en12183505.

- [PAPER-VI] O. Matiushkin, O. Husev, D. Vinnikov, C. Roncero-Clemente, "Optimal LCL-filter study for Buck-Boost Inverter Based on Unfolding Circuit," in proc. of 2020 IEEE 14th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), online event, Setubal, Portugal, Jul. 8-10, 2020. DOI: 10.1109/CPE-POWERENG48600.2020.9161683.

- [PAPER-VII] O. Matiushkin, D. Vinnikov, O. Husev, "Performance Evaluation of the Universal Photovoltaic String Converter During the Operation in DC Microgrid Environment," in proc. of IECON 2021 – 47th Annual Conference of the IEEE Industrial Electronics Society, online event, Toronto, ON, Canada, Oct. 13-16, 2021. DOI: 10.1109/IECON48115.2021.9589473.

#### **Author's Contribution to the Publications**

The author's contributions to the papers in this thesis are:

- [PAPER-I] Oleksandr Matiushkin is co-author of the paper. He was responsible for the simulation, calculation of the passive elements, and development of software for the experimental tests.

- [PAPER-II] Oleksandr Matiushkin has co-authored the paper and provided the experimental results of both types of system: open-loop and closed loop based on the Model Predictive Control (MPC). The parts for the control and measurement system of the prototype were developed by him.

- [PAPER-III] Oleksandr Matiushkin as main author developed the MPC system within the experimental prototype for a grid-connected system. Oleksandr Matiushkin has provided a literature analysis, calculation processes, and the writing. He was responsible for submission and contact with editors during peer-reviewing rounds.

- [PAPER-IV] Oleksandr Matiushkin has co-authored the paper and provided a methodology of calculation and software developing for the experimental prototype. Oleksandr took part in the writing, review and editing of the paper.

- [PAPER-V] Oleksandr Matiushkin is co-author of the paper. He was responsible for methodology, software developing, writing and draft preparation and for experimental validation.

- [PAPER-VI] Oleksandr Matiushkin as a main author of the paper was responsible for the literature review, the writing, submission, and a calculation process. He has performed validation of the calculation in simulation. Oleksandr Matiushkin presented the paper online in virtual event IEEE 14th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG) 2020.

- [PAPER-VII] Oleksandr Matiushkin was a main author of the paper. He has performed a literature review, experimental tests, writing and submission. He has developed a control system for the experimental setup. He presented the paper on virtual conference IECON 2021 47th Annual Conference of the IEEE Industrial Electronics Society.

#### **Abbreviations**

AC or ac Alternative Current

ADC Analog to Digital Converter

BVSI Voltage Source Inverter with Boost Cell

CB Circuit Breaker

CEC California Energy Commission

SiC Silicon Carbide

DC or dc Direct Current

DCMG Direct Current Microgrid

EMI Electromagnetic Interference

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

MCU Micro Controller Unit

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

MPC Model Predictive Control

MPP Maximum Power Point

MPPT Maximum Power Point Tracking

PCB Printed Circuit Board

PLL Phase Locked Loop

PMC Phase-Modular Converter

PV Photovoltaic

PWM Pulse Width Modulation

RMS Root Mean Square

SSA Steady State Analysis

SSCB Solid State Circuit Breaker

SSR Solid State Relay

TalTech Tallinn University of Technology

THD Total Harmonic Distortion

TRL Technology Readiness Level

VSI Voltage Source Inverter

# **Symbols**

$C_{IN}$  Input capacitor for decoupling the input current

$C_s$  Snubber capacitor of solid-state relay  $C_S$  Output capacitor of the converter

$C_x$  Capacitor D Duty cycle

D' Inverted duty cycle and equals 1-D Diode of the buck-boost part

Dab Duty cycle for buck-boost mode for Twisted buck-boost inverter

based on Unfolding circuit

$D_{BOOST}$  Duty cycle for boost mode  $D_{BUCK}$  Duty cycle for buck mode  $D_{Sx}$  Duty cycle of the switch  $\varepsilon$  Efficiency of the converter

f PWM frequency  $f_g$  Grid frequency  $f_{SAMPLE}$  Sample frequency

F Fuse

$I_{DC}$  Current of dc grid

$i_{CI}$  Current of the unfolding capacitor  $i_{CS}$  Current of the output capacitor

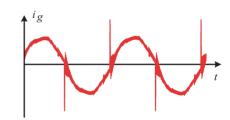

$egin{array}{ll} i_g & {\sf Grid~current} \ i_{IN} & {\sf Input~current} \end{array}$

$\Delta i_L$  Current change in the input inductance during PWM period

$i_L$  Current of the input inductance

$I_{LMAX}$  Maximum current value of the input inductance in ac mode  $\Delta i_{Lf}$  Current change in the output inductance during PWM period

$i_{Lf}$  Current of the output inductance

$I_{LfMAX}$  Maximum current value of the output inductance in ac mode

$i_{LREF}$  Reference signal for input inductor current

$i_O$  Output current of the off-gird mode  $i_{REF}$  Reference signal for grid current

$K_C$  Ripple factor of unfolding capacitor voltage  $K_{Cs}$  Ripple factor of output capacitor voltage  $K_L$  Ripple factor of input inductance current  $K_{Lf}$  Ripple factor of output inductance current

$L_f$  Output inductor of the converter

$L_g$  Grid side filter inductances

$L_x$  Inductance

$N_C$  Number of capacitors  $N_L$  Number of inductors

P Input power of the converter  $R_C$  Unfolding capacitor's resistance  $R_{CIN}$  Input capacitor's resistance  $R_{Cs}$  Output capacitor's resistance

$R_g$  Grid resistance  $R_{IN}$  Input line resistance

$R_L$  Input inductance's resistance  $R_{Lf}$  Output inductance's resistance

$R_s$  Snubber resistance of solid-state relay

$R_{SWx}$  On state resistance of high-frequency transistor  $R_{UNFOLD}$  On state resistance of switch of unfolding circuit

$REL_x$  Mechanical relay

$S_{1-1}$ - $S_{1-2}$  Solid state relay switches

$S_{Wx}$  Switch based on mechanical relay

$S_x$  High frequency switch

$T_S$  PWM period

$T_x$  Low frequency transistor  $\Delta V_C$  Voltage spike at the grid side

$\Delta v_{CI}$  Voltage change of the unfolding capacitor during PWM period

$v_{CI}$  Voltage across unfolding capacitor

$V_{CIMAX}$  Maximum voltage value of the unfolding capacitor in ac mode  $\Delta v_{CS}$  Voltage change of the output voltage during PWM period  $V_{CSMAX}$  Maximum voltage value of the output capacitor in ac mode

$V_{C\ MAX}$  Maximum voltage value at the grid side during disconnection from

dc grid

$egin{array}{ll} V_{DC} & ext{Voltage of dc grid} \\ v_g & ext{Grid voltage} \\ v_{IN} & ext{Input voltage} \\ \end{array}$

$v_{LI}$  Voltage across input inductance  $v_{Lf}$  Voltage across output inductance

$V_M$  Amplitude of the grid voltage in ac mode  $v_{OUT}$  Output voltage of the off-grid mode

$v_{REF}$  Reference signal

$W_{ix}$  Weight factor of cost function

$Z_g$  Grid impedance

#### 1 Introduction

#### 1.1 Background

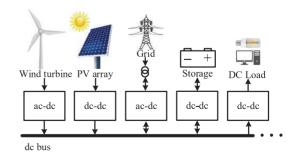

Most of the electronic devices that we are using every day at home or at the office require a similar approach in terms of the power electronics. For example, in residential buildings with a traditional ac grid most loads have a dc nature, therefore all our devices at home require an additional converter. A traditional laptop's battery voltage is 15 V - 22 V. It is known that the rectified ac grid voltage equals a peak of a one grid phase 310 V - 325 V. Consequently, a laptop battery requires a converter, which rectifies the sinusoidal voltage to a constant 320 V (ac-dc converter: a rectifier diode bridge) and which reduces 320 V to the necessary constant 15 V - 22 V (dc-dc converter). Thus, the main power electronics of traditional electronic devices are intended to rectify the traditional ac grid in a constant voltage level and subsequently convert it to the necessary voltage value (laptop charger, phone charger, TV, light systems, PC, etc.), as shown in Fig. 1.1a. At the same time, the amount of renewable energy systems which produce a dc voltage and current is increasing each year. The issue thus arises: "Is it reasonable to use devices with a redundant ac part, instead of simple dc-dc converter?".

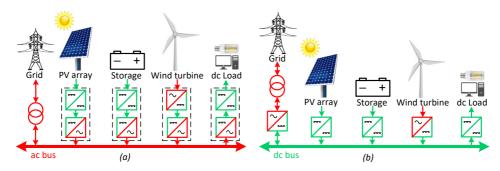

Although the war between Tesla and Edison has long finished, the modern systems have forced humanity to revive this issue with renewed vigour [1], [2]. Nowadays, dc microgrids attract more attention because many sources and loads have a dc nature. For example, solar panels, fuel cells and energy storage systems generate only dc voltage and current. It would be logical to connect all devices with a common dc bus [3], [4], without redundant ac conversion. Fig. 1.1b shows an example of the possible DCMG architecture addressed in [5]-[8]. The considered DCMG system is more efficient and reliable. Moreover, the dc grid is free from harmonics and does not provide a reactive power. DCMG systems do not need complex synchronisation and control units.

Figure 1.1 Traditional ac distribution system (a), Considered energy transmission system based on common dc bus (b).

However, the ac grid still dominates because there is no clear standard for the dc grid. From an economical point of view the voltage level of 326 V is the most sustainable for the dc grid [9]. This voltage level is applicable to the grid systems using existing cables. However, a company in Netherlands claims that the possible standards are 350 V for low power and 700 V for high-power applications [10]. It is proven in [11] that a high-voltage dc system is more efficient than a traditional ac distribution system. Possible dc distribution systems imply the creation of a different voltage level standard for dc grid types, such as

DCMG, dc nano grid, etc. [12], [13]. The modern base of the power electronics can provide any transformation of the power, however the price for that is still high.

One of the main challenges for dc distribution systems is to develop a circuit breaker for dc grid systems. A conventional ac circuit breaker determines short circuit and works under a zero-crossing point (standardised solutions IEC 61869, IEC 60255, IEC 61850, and IEC 60834). The clearing time in ac grid systems is 80 ms (4 cycles) [14]. Dc grid voltage does not fall to zero, so the conventional protection systems are not suitable. In contrast to conventional relays, it should be a device that keeps the same features as traditional and disconnects the circuit fast. One possible solution is Solid State Relay (SSR) or hybrid mechanical breakers [15]. This type of breaker should offer following features [16]: a fast response, low power losses, high reliability, compact size, long lifetime, and low cost. There are several ideas for the implementation of a dc breaker [17],[18]. Despite the drawbacks of the dc systems, the benefits outweigh the disadvantages. The dc grid will probably appear during the next decade and is already attracting attention as a future electric transmission system.

#### 1.2 Motivation of the Thesis

Since the dc grid appeared as a trend, devices applicable to both types of grids have come into demand. For example, hybrid converters have several terminals for each grid bus [19], [20]. Most of the solar hybrid converters have intended power electronics for each type of electrical distribution system. Moreover, a hybrid converter usually has a dc terminal for a storage element. However, there is a converter that has several terminals for the ac and dc grid. The general term for this type of device is a multiphase or multiport converter [21], [22], [23]. Multiphase converters can be useful for multiphase ac and dc applications. Another possible solution is an energy router for residential applications [24],[25],[26]. They have terminals for each part of the system (dc grid, ac grid, storage, PV panels, etc.). However, all the mentioned converters have a significant drawback as an internal redundancy. This is because these converters require different parts of power electronics to provide transmission energy from/to source to/from the undefined grid. Moreover, these converters will have separate control units and induvial protection systems for each type of grid.

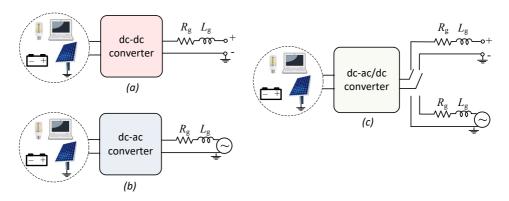

Figure 1.2 Connection of loads, storage systems or solar string to: dc grid with dc-dc converter (a), ac grid with dc-ac converter (b), any type of the grid with universal dc-ac/dc converter (c).

On the other hand, if in the near future the dc grid will be integrated into our residential buildings, a type of converter should also be suitable for the ac grid. For example, the dc grid socket will be integrated in a building and logically a customer will buy a dc-dc charger (Fig. 1.2a). In the second case, when this customer comes to an old building with a traditional ac grid socket, he will require an ac-dc charger for his laptop, as shown in Fig. 1.2b. From an economical part of view, a universal solar converter is cheaper and offers the benefits of dc-dc and dc-ac converters. The universal solar converter takes away inconvenience for the customer because the market is limited for dc-dc devices. Such a converter can be connected to both types of grid by the same terminals and at the same time has minimal internal redundancy (Fig 1.2c). The universal converter with minimum redundancy will use the same protection system and control unit for both types of grid, while the control system will automatically detect a type of connected grid. At the same time the universal converter can be bidirectional and suitable for PV applications or other renewable energy sources.

This thesis was conducted according to one of the research directions of the Power Electronics Group of Tallinn University of Technology. The aim is to gather knowledge and develop the universal solar converter for residential dc and ac grids with minimum redundancy. The current work was supported by PRG675 "New Generation of High-Performance Power Electronic Converters Simultaneously Applicable for dc and ac Grids with Extended Functionalities", and by EAG122 "Universal dc/ac battery storage interface (UniBSI)", and by PRG1086 "Future-Proof Power Electronic Systems for Residential Microgrids" from Estonian Research Council, and by TAR16012AT "Zero energy and resource efficient smart buildings and districts" from the Archimedes Foundation and.

### 1.3 Aims, Hypothesis and Research Tasks

The main aim of the PhD research project is to develop and experimentally confirm a concept of universal dc-dc/ac converter which is applicable for both types of grid. It considers a solution which may speed up transition from conventional ac systems to the hybrid dc/ac systems. The author set a goal to obtain acceptable efficiency in comparison with popular solutions by using the low-frequency unfolding circuit. The outcome of this work is to develop and launch TRL 6 prototype with a real ac grid and virtual dc grid.

#### **Hypotheses:**

- 1. Buck-boost cells with unfolding circuit may provide the universal operation with minimal redundancy.

- 2. Buck-boost cells with unfolding circuit may provide the reactive current injection in the ac grid-connected mode.

- 3. Synchronous switches operation reduces zero crossing distortions and improves quality of the grid current.

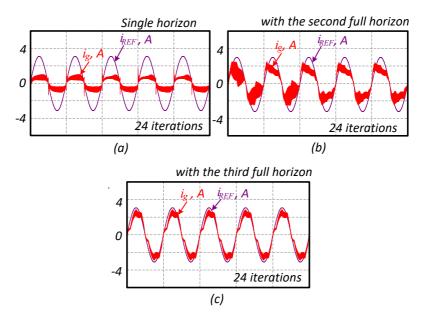

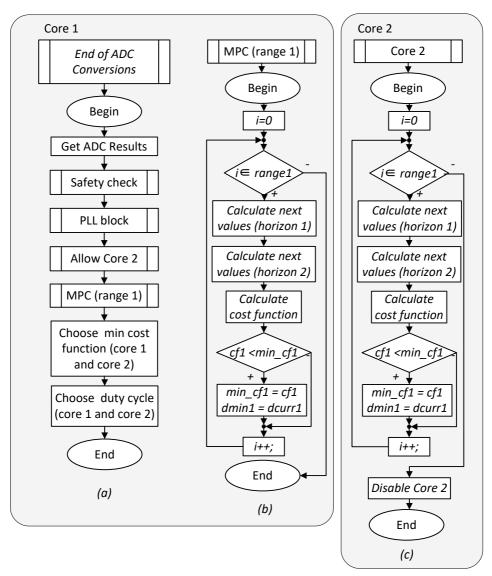

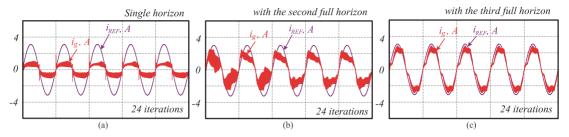

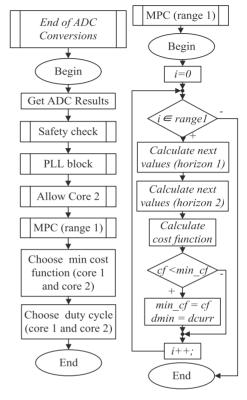

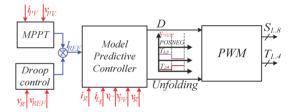

- Model Predictive Control (MPC) with modified cost function can be feasible for implementation with low-cost microcontrollers.

#### Research tasks:

- 1. To review the existing solutions on the market.

- 2. Research and design the most suitable power electronic interface for universal application.

- 3. Research power electronics interface requirements for simultaneous applicability for AC and dc grids.

- 4. Research and develop a control regulator for a grid-connected system.

- 5. Design of the experimental setup and experimental verification of the universal converter simultaneously applicable for ac and dc grids.

#### 1.4 Research Methods

The research methods used to carry out the thesis are based on the mathematical analysis, simulation models and experimental verification. New developed topologies and circuits are mathematically analysed using Steady-State Analysis (SSA) [27], [28] as well as transient analysis using functional analysis, including Laplace and Fourier transform techniques. To study the operating properties of the new topologies and control algorithms, dynamic and static models (with and without losses in components) are developed. Computer simulations are generally performed in the MATLAB, Altium Designer and PSIM software packages, which are all available at the Tallinn University of Technology (TalTech). Experimental investigation and validation of theoretically predicted results are performed using small laboratory physical models (≤5 kW) of new topologies, circuits, and unconventional arrangement. The Power Electronics Research Laboratory of TalTech has modern facilities (digital oscilloscopes and function generators, power quality and efficiency analyzers, microprocessor development tools, PCB prototyping, and assembling tools, etc.) for the hardware and software development.

#### 1.5 Contributions and Disseminations

The results of the research are presented via scientific publications, conferences, symposiums, doctoral schools, and presentations. During PhD studies the author contributed to 18 publications. Among them, nine papers were published in peer-reviewed international journals. The remaining papers were reported at international IEEE conferences. The dissertation is based on seven main scientific publications, including five journals and two conference papers presented at two IEEE international conferences.

#### **Scientific novelties:**

- Development of novel family of topologies suitable for universal application.

- Definition of requirements for the power electronics interface for universal application.

- Synthesis of novel modulation approach for dc-dc or dc-ac converters.

- Synthesis and control the grid current of the minimum phase system using MPC.

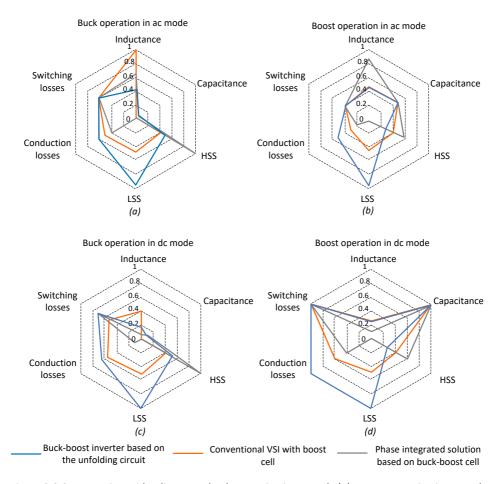

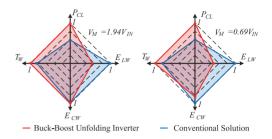

- Comprehensive comparative analysis of buck-boost inverter based on unfolding circuit and conventional solution as a H5, H6 and HERIC topologies.

#### **Practical novelties:**

- Reducing zero crossing distortion of the topologies based on the unfolding circuit using synchronous switches instead of diodes and shift methods.

- Developing a new type of device applicable for both types of grid with the same terminals and minimum redundancy.

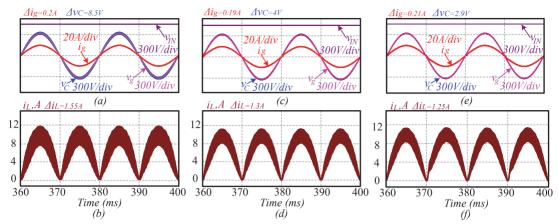

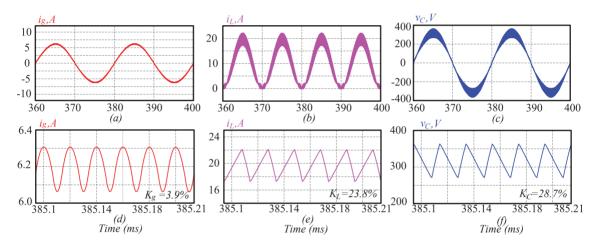

Two buck-boost inverters based on the unfolding circuit were assessed and experimentally confirmed with a grid-connected system: single-stage buck-boost inverter based on the unfolding circuit; twisted buck-boost inverter based on the unfolding circuit.

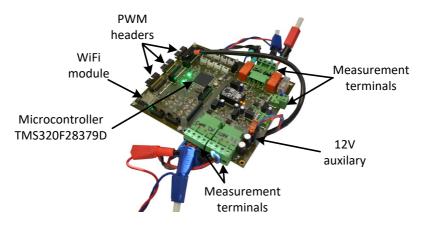

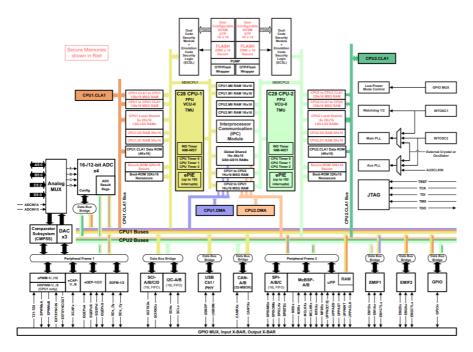

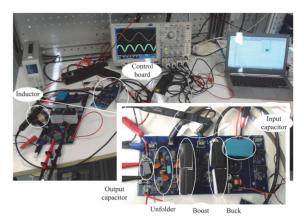

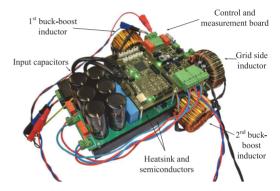

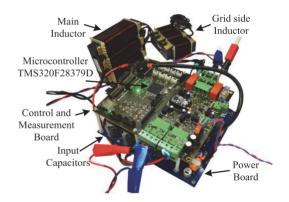

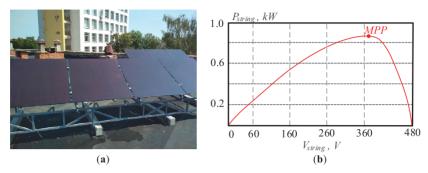

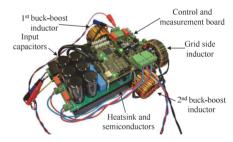

#### 1.6 Experimental Setup and Instruments

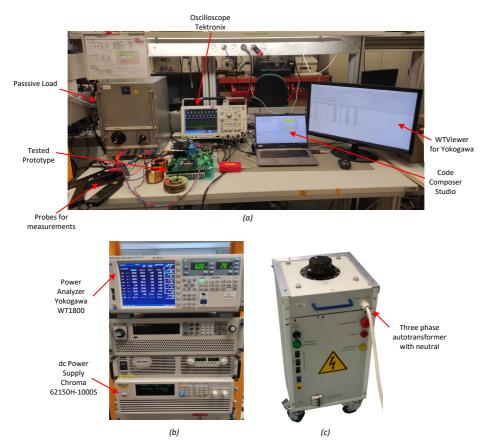

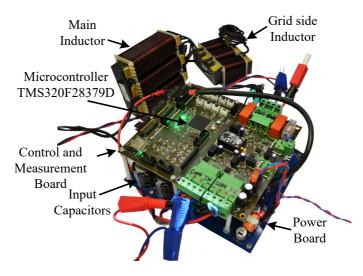

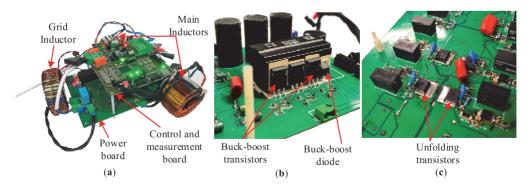

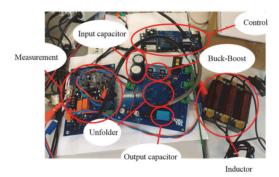

The experimental setup was assembled in the power electronics laboratory of Tallinn University of Technology. The workspace in the lab is shown in Fig. 1.3a. The oscilloscope Tektronix MDO4034B-3 helps to catch the waveforms of voltages and currents of the passive components. The special probes Tektronix P5205A and Tektronix TCP0030A are useful for voltage and current measurements respectively. The Code Composer Studio is an environment for writing a code for MCU from Texas Instruments and was used during code developing.

Figure 1.3 Workplace in the laboratory of power electronics (a), Power analyser with a dc source for the experimental setup (b), An autotransformer for a grid connected system (c).

Power Analyzer Yokogawa WT1800 was used for efficiency measurement within software application WTViewer for remote equipment access. The solar simulator equipment Chroma 62150H-1000S was used as an input voltage source for an experimental prototype, as shown in Fig. 1.3b. The passive load Frizlen BW 20 was used

in the open loop system, while the autotransformer was chosen for the grid-connected system as a grid (Fig. 1.3c).

#### 1.7 Thesis Outline

Chapter 2 describes the concept of the universal dc-ac/dc converter based on the buck-boost converter with an unfolding circuit. The passive element design is considered in Chapter 2. The experimental results based on the open loop system are presented.

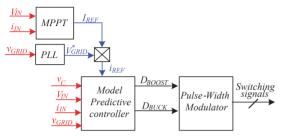

In Chapter 3 control system details are discussed. The non-linear control block based on the MPC is a main regulator, which is considered in Chapter 3. The special control strategy simplifies a calculation and decreases computational time.

The experimental results for the grid-connected system are presented in Chapter 4. The chapter considers all experimental setups that were developed based on the thesis topic.

The last Chapter 5 provides a comparison of the buck-boost inverter based on the unfolding circuit with conventional solution as a H5, H6 and HERIC topologies. The comparison results allowed the possibility to choose the necessary semiconductors.

# 2 Concept of the Universal dc-dc/ac Converters

The target of dc grid integration of PV plants leads to the appearance of a string dc-dc converter, although conventional dc-ac inverters are still in demand. The market for the solar microinverters concluded the same statement. The isolated dc-dc solar converters are useful for customers. Currently companies [10], [29], [30] consider dc-dc solar optimizers and string dc-dc converters as a future target market. However, the universal dc-dc/ac converter can be useful as an alternative solution. This alternative solution provides flexibility and the possibility of a connection to dc grid or to ac grid. The same features can be found in any of the renewable energy converters.

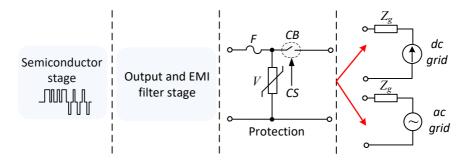

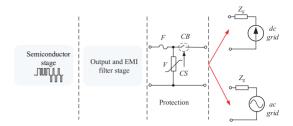

The simplified structure of the universal dc-dc/ac solar converter is shown in Fig. 2.1. The structure contains a semiconductor stage depending on topology, an output filter along with an Electromagnetic Interference (EMI) filter, protection hardware circuit and grid side with an impedance. Such a structure can be considered as an interface between dc input voltage source and any residential grid (dc or ac). Moreover, a similar system is suitable for an ac voltage source as well. This solution can be generalized for any application with a grid connection.

Figure 2.1 Simplified structure of the universal dc-dc/ac solar converter.

One of the main aims of this chapter is to define the requirements for power electronics converters and a possible internal structure for a universal solar converter for dc and ac operation modes.

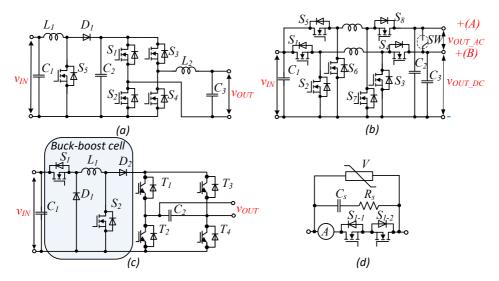

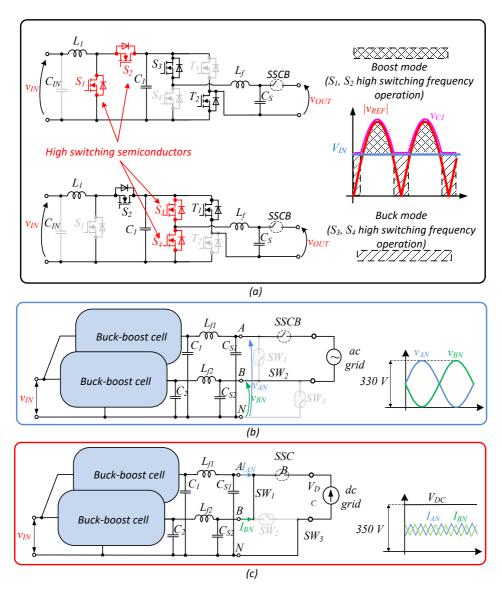

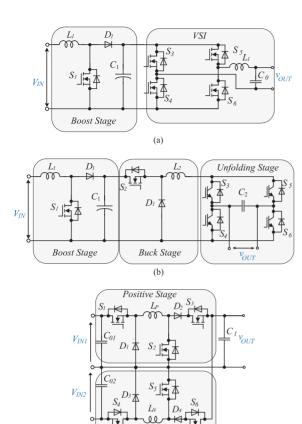

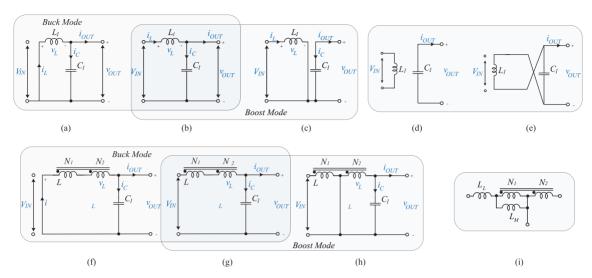

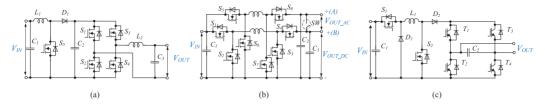

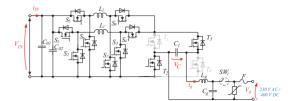

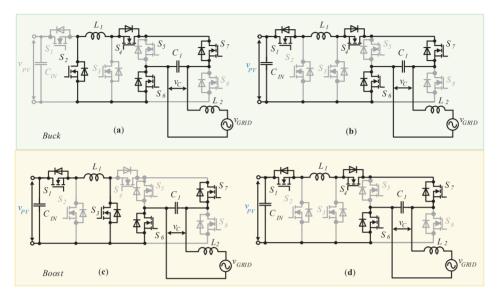

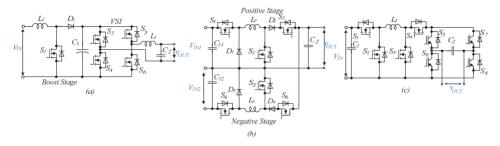

Fig. 2.2 shows several possible topologies for a semiconductor stage of the single-phase universal string solar converter. The conventional Voltage Source Inverter (VSI) with an intermediate dc-dc boost cell can be connected to the dc grid (Fig. 2.2a). A simple full-bridge inverter with a boost dc-link has a wide range of the input voltage regulation, a simple control strategy and freewheeling states. Some good overviews of the conventional solar inverters are provided in [31], [32]. At the same time many inverters can work in the dc-dc mode. High step-up inverters [33], [34], [35] or common ground inverters can also be competitive solutions [36], [37]. However, they may have inherited limited power range or lower efficiency from dc-ac mode.

On the other hand, Fig. 2.2b shows one more possible solution for a universal single-phase dc-dc/ac solar converter. The structure of such a topology is similar to an interleaved synchronous buck-boost converter. The similar approach for boost converter and common input voltage source was discussed in [38].

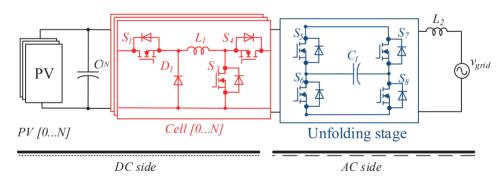

The third option as a possible universal solar converter is an inverter based on the unfolding circuit [39], [40], [41]. Fig. 2.2c shows a buck-boost inverter as part of the family of inverters based on unfolding circuit [42]. Such a solution can easily be adapted for the

dc-dc operation mode by the control system without any impact on redundancy. Moreover, the high number of semiconductors does not produce an excessive amount of switching losses, because the system has the minimal number of simultaneously switching semiconductors. At the same time, a buck-boost inverter based on the unfolding circuit does not have problems with leakage current, because it does not have a high-frequency component in the common-mode voltage.

Figure 2.2 Conventional VSI as a universal dc-dc/ac solution (a), Buck-boost derived universal dc-dc/ac converter (b), Buck-boost inverter based on unfolding circuit as universal dc-dc/ac converter (c), Solid-state relay based on four-quadrant switch (d).

#### 2.1 Protection Issue

The protection circuit is a usual tool for disconnecting the converter from the grid line. Such instruments are a standardised solution (IEC 61869, IEC 60255, IEC 61850, and IEC 60834). The important part of protection is a circuit breaker for a fast system break from the grid side. The main internal structure of ac CB is electromechanical components, which allows the possibility to disconnect the circuit during the zero-crossing point, which is a traditional principle of fault isolation. EMI filter is needed for avoiding higher harmonics propagation. As mentioned in Chapter 1, the time of CB in ac system equals around 80 ms, which corresponds to 4 cycles. An additional protection tool such as a fuse can prevent burning out all switches and unnecessary system activation after a fault. A varistor saves the system from overvoltage of the grid side.

However, a traditional CB became an unusual tool with the appearance of the dc grid concept, because dc voltage does not fall to zero value. Thus, designing a good protection system for the dc microgrid has been a challenge over the past few years [16]. A target fault clearing time in dc transmission system is considered as 2.5 ms.

The structure of the possible protection circuit between the power electronic converter and the low voltage dc grid can be the same. However, the main problem is the nature of the dc fault current because it can rapidly rise to more than a hundred times the nominal current. The dc microgrid has a low line impedance Zg. As a result, the fault current deviation is so big, and during a couple of milliseconds the current

increases to hundreds of amps. It means that ac protection instruments cannot be useful for dc grid protection. Dc grid protection should include high communication speed and good breaker functionalities [43]. As mentioned, one of the possible solutions for CB is a solid-state relay. These solutions offer such key features as fast response, high reliability, low conduction loss, long lifetime, and low cost. On the other hand, if CB is suitable for dc grid protection, it can be applied to the ac grid as well. Fig. 2.2d shows the possible solid-state relay for a dc grid CB. The SSR is based on a four-quadrant switch and a current sensor. An additional snubber in parallel provides smooth switching, while a varistor save CB from overvoltage.

#### 2.1.1 Grounding Issue

Grounding is another issue which relates to safety and protection. The traditional ac system ground has or may have the same potential as a neutral ground. However, the potential between ac and dc ground is undefined if ac and dc grids coexist together in the future. The main reason is that the dc bus line will be derived by rectification of the ac voltage. There are several options that can be utilized for grounding. The first solution is to use galvanic isolation between the dc and ac sides via using a transformer. The other options are to set low or high resistance grounding or without grounding [44], [45]. None of these solutions have an impact on the discussed universal solutions. If a universal converter works with an ac system, where the impedance between ground and neutral wires are low, then it can work with the dc grounded system as well.

Another important issue is a leakage current, which appears in all transformerless no-common-ground converters. In most cases it can be solved by common-mode filters [46], [47], that can be easily integrated into a circuit. Another way is to apply special modulation techniques to reduce a leakage current [48], [49]. The universal solar converters based on the unfolding circuit have a very small high-frequency common-mode voltage component. Thus, the EMI filter is not needed for universal dc-dc/ac converters. The negative output terminal of buck-boost inverter based on the unfolding will be connected to common ground in the case of dc mode and a leakage current will be absent.

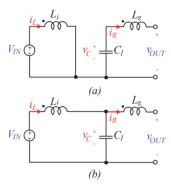

#### 2.1.2 Output Filter Selection in Terms of Protection

Another important parameter is the grid current quality. Filters with inductors at the grid side are the most suitable to control the grid current. In many cases the grid side inductance is assumed as an internal grid impedance. The calculation guidelines are well-known and have been widely studied [50]. The topic of the dc grid systems along with converters connected to the dc grid has become popular. However, the grid filter design is not so widely studied. Usually, the capacitor is used at the grid side, but the specific value of grid capacitor is not defined.

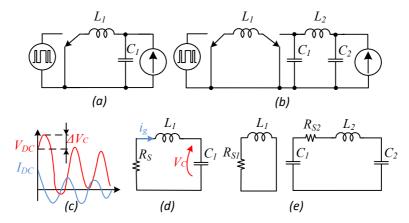

A simple filter can be integrated into a simple boost converter where the input inductor is not connected to the output capacitor. The same LC-filter can be suitable for a conventional buck converter, see Fig. 2.3a. In both cases the grid capacitor should be small in order to prevent high spikes during connection to the grid, because there can be a voltage difference. On the other hand, Steady State Analysis does not require an additional capacitor for grid current quality. At the same time, a sudden disconnection from the grid can be accompanied by a voltage spike due to the presence of the output inductor. Thus, this capacitor can be considered as a suppressor to limit possible voltage spike.

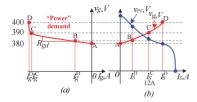

The CLC-filter in Fig. 2.3b can be considered as a further derivation of a C-filter suitable for boost converters. The capacitor  $C_I$  along with the inductor  $L_I$  are the main filtering elements, while the grid side capacitor  $C_2$  is a suppressor. Fig. 2.3d shows a simplified equivalent circuit of a sudden dc grid disconnection process in the case of a grid side LC-filter. The control system has to perform a short circuit at the output side of the converter to minimise the voltage spike  $\Delta V_C$  across the capacitor  $C_I$  after detecting a sudden dc grid disconnection.

Figure 2.3 Switching process during sudden dc-grid disconnection: disconnection schematic for LC-filter (a), disconnection schematic for the LCLC-filter (b), transient process of the output voltage and output inductor current (c), equivalent circuit of the LC-filter (d), equivalent circuit of the LCLC-filter (e).

The perfect transient waveforms are shown in Fig. 2.3c. As usual the waveform of transient process is oscillation. The above process describes the equivalent circuit in Fig. 2.3d, and it is possible to derive differential equations:

$$L_1 \cdot \frac{di_g}{dt} = -i_g \cdot R_S - v_C, \quad C_1 \cdot \frac{dv_C}{dt} = i_g \quad . \tag{2.1}$$

If the disconnection from the dc grid occurred, the initial conditions will be as follows:

$$i_{g}(0) = I_{DC}, \ v_{C}(0) = V_{DC},$$

(2.2)

where  $V_{DC}$  is a dc grid voltage at the moment of disconnection, while the  $I_{DC}$  is a grid current at the moment of disconnection.

The voltage across the output capacitor is starting to grow up to maximum value  $V_{C\_MAX}$  after disconnection from dc grid due to the accumulated energy in the inductor. The solution of eq. (2.1) is simple, but it is massive. The series resistance defines the damping ratio of this oscillation but does not have a significant influence on the maximum value  $V_{C\_MAX}$ .

If to neglect parasitic resistance Rs, it is possible to find a simplified expression of the maximum voltage across the capacitor. The entire accumulated energy in the inductor is flowing to the capacitor:

$$\frac{L_1 \cdot I_{DC}^2}{2} = \frac{C_1 \cdot \left(V_{C_{-MAX}}^2 - V_{DC}^2\right)}{2} \,. \tag{2.3}$$

Finally, the expression for the voltage spike  $\Delta V_C$  across the capacitor  $C_I$  can be calculated:

$$\Delta V_C = V_{C_{-MAX}} - V_{DC} = \sqrt{\frac{L_1}{C_1} \cdot I_{DC}^2 + V_{DC}^2} - V_{DC}.$$

(2.4)

The value of the voltage spike is proportional to the initial current and filtering inductance, while it is opposite to the value of the suppressing capacitor. As a result, design guidelines must consider a maximum voltage spike across the capacitor and maximum power of the converter.

Fig. 2.3e shows the equivalent circuit in the case of CLC- and LCLC-filters after dc grid disconnection. Based on this circuit, the expression of the suppression capacitor can be obtained in a similar way to solving differential equations. In the case of the CLC-filter, one more differential equation is needed:

$$L_1 \cdot \frac{di_g}{dt} = -i_g \cdot R_S$$

,  $C_1 \cdot \frac{dv_{C1}}{dt} = -i_g$ ,  $C_2 \cdot \frac{dv_{C2}}{dt} = i_g$ . (2.5)

The initial values are the same as before and correspond to grid voltage and current:

$$i_{\sigma}(0) = I_{DC}, \ v_{C1}(0) = V_{DC}, \ v_{C2}(0) = V_{DC}.$$

(2.6)

In the same way it is possible to identify energy between capacitors and inductor after disconnecting from the dc grid. It is possible to write a system of equation to get the suppressor voltage spike:

$$\begin{cases} C_{1} \cdot \frac{V_{DC} - V_{C\_MAX1}}{t_{0}} = C_{2} \cdot \frac{V_{C\_MAX} - V_{DC}}{t_{0}} \\ \frac{L_{2} \cdot I_{DC}^{2}}{2} = C_{1} \cdot \frac{V_{C\_MAX1}^{2} - V_{DC}^{2}}{2} + C_{2} \cdot \frac{V_{C\_MAX}^{2} - V_{DC}^{2}}{2} \end{cases}$$

(2.7)

Finally, solving equation system 2.7 gives a result for the voltage spike across the suppression capacitor:

$$\Delta V_C = \frac{I_{DC} \sqrt{C_1 C_2 L_2 (C_1 + C_2)}}{2C_2 (C_1 + C_2)}.$$

(2.8)

All other passive components of the universal converter part can be calculated similarly to the classical approach [PAPER-VI], [51] keeping the ripple in the current as a main parameter to be reduced.

#### 2.2 Summary

The converter based on unfolding stage can naturally provide dc or ac output voltage without additional redundancy. The power electronics converter that was initially designed for dc-ac application with an output filter stage for dc grid and fast protection relay can be considered as a universal solution. The CB must cover all demands of dc grid protection, while the output filter can be chosen as a filter for conventional ac application with an additional output capacitor (suppressor) to eliminate voltage spike at a sudden grid disconnection. The considered approach can be used as an industrial solution for low-voltage dc and ac systems.

### 3 Application Oriented Design

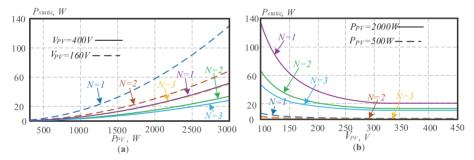

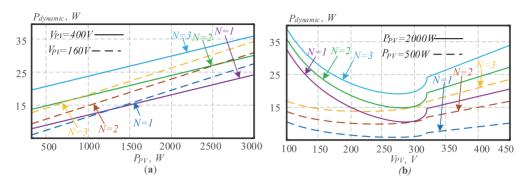

The fundamental waveforms of a converter are independent of the selection of components and electric parameters (e.g. switching frequency, selected semiconductors) and result from the basic modulation scheme and yield some general requirements for the dimensioning of the components. General requirements include passive components' estimation taking into account the same current ripple in the inductors and the same voltage ripple across capacitors.

The volume of a core of the inductor as well as the volume of capacitor can be estimated based on its maximum accumulated energy:

$$Vol_{L} \cong \sum_{i=1}^{N_{L}} L_{i} \cdot \hat{i}_{Li}^{2}, \quad Vol_{C} \cong \sum_{i=1}^{N_{C}} C_{i} \cdot \hat{v}_{Ci}^{2}, \tag{3.1}$$

where  $L_i$  and  $C_i$  are values of i inductance and capacitor,  $N_L$  is number of inductors and  $N_C$  is number of capacitors.  $\hat{i}_{Li}$  is a peak inductor current and  $\hat{\mathcal{V}}_{Ci}$  is a peak of capacitor voltage.

Moreover, the relative switching and conduction losses that are independent from the selection of semiconductors can be introduced. First of all, the relative conduction losses are proportional to the square of the switch current. As a result, total conduction losses can be scaled to the following scale:

$$CL \cong \sum_{i=1}^{N_S} \tilde{i}_{Si}^2, \tag{3.2}$$

where  $\tilde{i}_{Si}$  is RMS switch current,  $N_S$  is a number of switches.

Neglecting the current ripple, both the semiconductor voltage  $v_{Si}$  and semiconductor current  $i_{Si}$  influence the hard switching losses [56]. The average value of the product  $v_{Si}$  and  $i_{Si}$  over a fundamental period T express a good measure to indicate switching losses:

$$SL \cong \sum_{i=1}^{N_S} \left\langle \hat{i}_{Si} \cdot \hat{v}_{Si} \right\rangle_T. \tag{3.3}$$

Table 3.1 Target parameters of the universal interface converter.

| Parameters                                      | Value             |

|-------------------------------------------------|-------------------|

| RMS grid voltage $V_{grid}$ , V                 | 230 ac/350 dc     |

| Output power range P, W                         | 100-3600/100-5000 |

| Input voltage range, V                          | 100-500           |

| Maximum input current, A                        | 10/18             |

| Maximum input current ripple, %                 | 40                |

| THD of the output current in the ac mode, %     | 5                 |

| Maximum output current ripple in the dc mode, % | 5                 |

| Maximum switching frequency                     | 62 kHz            |

Obviously, unfolding transistors do not contribute to the switching losses, as no switching transitions occur. Taking into account the size and price optimisation, it is necessary to calculate the minimal values of passive components that are able to provide acceptable input and output power quality. At the same time, due to the

non-conventional utilisation, it has to take into account both dc and ac modes. Table 3.1 summarises the parameters of the universal interface converter including target demands for passive components.

#### 3.1 Design of the Filters

Steady state analysis is considered as the main tool for calculations. SSA allows to obtain the expressions of the passive components with sufficient tolerance. The calculation of inverters based on the infolding circuit has a difference to a simple SSA because the system is the 4<sup>th</sup> order type in buck mode and the 3<sup>d</sup> order type in boost mode. The calculation is too bulky, which is why only a buck-boost inverter with an unfolding circuit which operates in a buck mode was considered. The same approach was applied to all selected topologies for all modes: buck and boost.

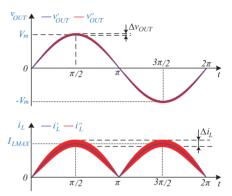

Basically, the calculation of the passive components with using SSA relates to the dc-dc converter. On the other hand, the ac grid-connected system also operates with a high switching frequency. It is possible to underline that, during several PWM periods, any power parameter is in a steady state. The output voltage is a sinusoidal power signal, while the output current directly depends on the output voltage and the load:

$$v_{OUT} = V_M \cdot \sin(\varphi)$$

,  $i_O = \frac{v_{OUT}}{R_I}$ , (3.4)

where  $V_M$  is the peak of the output voltage,  $R_L$  is a resistance load.

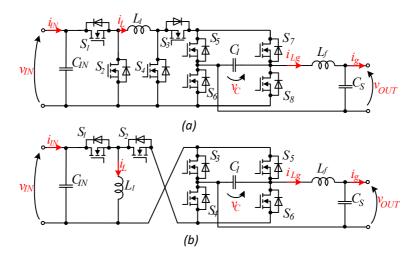

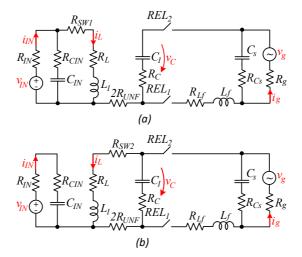

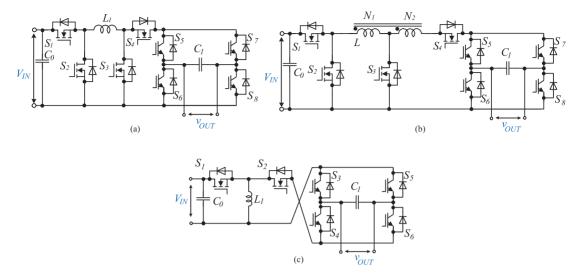

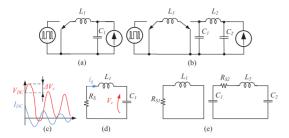

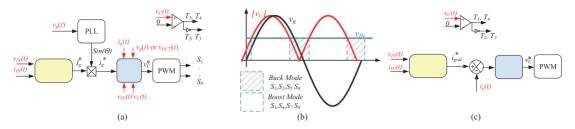

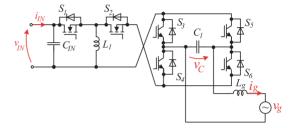

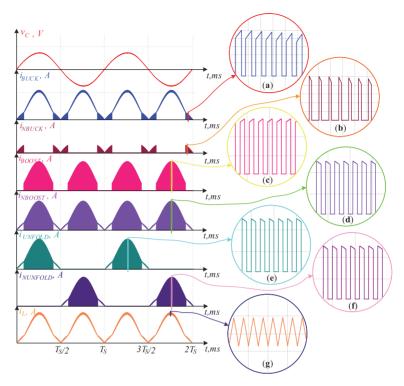

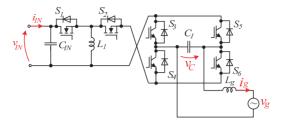

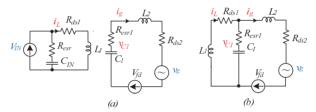

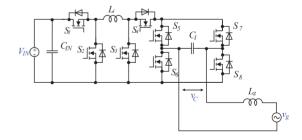

Fig. 3.1 shows the topologies of the buck-boost inverters based on the unfolding circuit that were proposed as the inverter's family in [42].

Figure 3.1 Family of the single-phase buck-boost inverters based on the unfolding circuit: Buck boost inverter with unfolding circuit (a), Twisted buck-boost inverter based on unfolding circuit (b).

The first topology of the inverter's family is a single buck-boost inverter based on the unfolding circuit with two inductors (Fig. 3.1 $\alpha$ ): the input inductor is a main part of converter and the second is a grid filter inductor. The circuit consists of an input inductance  $L_I$ , a small capacitor  $C_I$  instead of a big dc-link capacitor, the output LC-filter for protection and current quality and eight switches  $S_I$ — $S_S$ . In part, the principle of

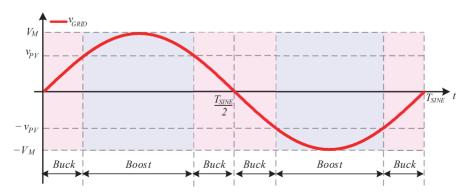

operation is described in [52], which selects the mode of operation based on the ratio between the input and the output voltage.

The unfolding circuit is operating with a low frequency of switching, while the buck-boost part is working with high frequency. Despite a high number of switches that generally decrease reliability, it provides a very flexible modulation strategy. Switches  $S_I$  and  $S_2$  correspond to buck mode and  $S_3$ ,  $S_4$  are working in boost operational mode. At the same time, transistors  $S_I$  and  $S_3$  are the main switches of the basic operation modes of the converter.

The transistors  $S_2$  and  $S_4$  can be replaced by diodes in case unidirectional operation is required. In the case of bidirectional power flow, the switches  $S_2$  and  $S_4$  should be selected as transistors. A bidirectional power flow allows the possibility to work as a rectification converter, which may be useful in another application. Transistors  $S_5$ - $S_8$  work as a simple unfolding circuit in accordance to the classical unfolding circuit. Potentially, the unfolding switches can also be used with a high-frequency modulation.

The buck mode will be applied when the input voltage  $v_{I\!N}$  will be higher than the instantaneous value of the output voltage. The buck mode operates using a traditional duty cycle dependence:

$$v_{OUT} = D_{S1} \cdot v_{IN} . \tag{3.5}$$

where  $D_{SI}$  is a duty cycle for the transistor  $S_I$ . The converter works in two states: active state corresponds to conduct switch  $S_I$  and zero state, where  $S_2$  is conducting.

Otherwise, if the input voltage is smaller than the output instantaneous value of the output voltage  $v_{OUT}$ , the boost mode will be chosen. During boost mode transistor  $S_I$  is conducting, complementary switches  $S_3$  and  $S_4$  are responsible for boost function:

$$v_{OUT} = \frac{v_{IN}}{1 - D_{S3}},\tag{3.6}$$

where  $D_{S3}$  is duty cycle of the switch  $S_3$ . Therefore, the buck or boost functionality is selected based on the ratio between the input and output levels.

The second topology is the twisted buck-boost inverter based on the unfolding circuit, which is shown in Fig. 3.1b. The details regarding a twisted inverter based on the unfolding circuit are presented in [PAPER-V]. The operational principle of this converter is slightly different to the first topology. The main difference is the number of switches and one operational mode. The converter works only with a buck-boost mode and does not require tracking the ratio between input and output voltages. The twisted inverter is based on the conventional buck-boost dc-dc converter with known gain factor:

$$v_{OUT} = \frac{D_{S1}}{1 - D_{S1}} \cdot v_{IN} \,. \tag{3.7}$$

Switch  $S_I$  is responsible for generating necessary value of the output voltage, while  $S_2$  can be replaced by a diode for unidirectional power flow. The unfolding circuit is realized by transistors  $S_3$ - $S_6$  with low switching frequency.

A significant number of the semiconductors does not cause a significant switching loss, because only two transistors are switching in any operation point. The common mode voltage of any of these solutions does not have high-switching harmonic, as a result small size of the common mode filter is required.

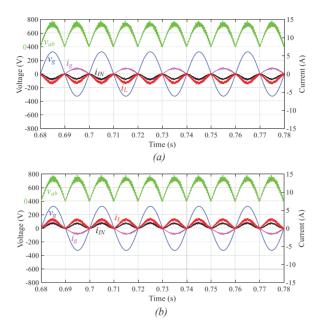

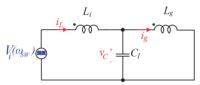

Figure 3.2 Equivalent circuits of buck-boost inverter based on unfolding circuit: buck mode (a)-(b), boost mode (b)-(c).

Then the buck-boost inverter based on the unfolding circuit operates in buck mode, and two states are used: active and zero. The equivalent circuits of the buck operation are shown in Figs. 3.2a and 3.2b. Two LC-filters provide small ripples at the output side during buck mode. Figs. 3.2b and 3.2c show the equivalent circuits of the boost mode. The purpose of the boost case is to store energy in the input coil and to transfer accumulated energy immediately to the load via the CLC-filter.

As a first action, the Kirchhoff rules should be considered to obtain the basic equations of each equivalent circuit:

$$\begin{cases} v_{L1} = v_{IN} - v_{C1} \\ i_{C1} = i_L - i_{Lf} \\ v_{Lf} = v_{IN} - v_{L1} - v_{OUT} \\ i_{Cs} = i_{Lf} - i_{o} \\ Fig. 3.2a \end{cases}, \begin{cases} v_{L1} = -v_{C1} \\ i_{C1} = i_L - i_{Lf} \\ v_{Lf} = -v_{L1} - v_{OUT} \\ i_{Cs} = i_{Lf} - i_{o} \\ Fig. 3.2b \end{cases}$$

$$(3.8)$$

where  $v_{LI}$  is the voltage on the input inductance,  $v_{Lf}$  is the voltage across the output inductor,  $i_{CI}$  is the current of the unfolding circuit capacitor,  $i_{Cs}$  is the current of the output capacitor,  $v_{IN}$  is the input voltage,  $v_{OUT}$  is the output voltage.

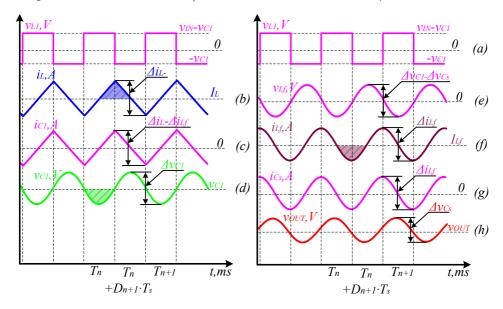

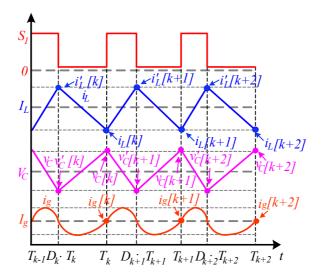

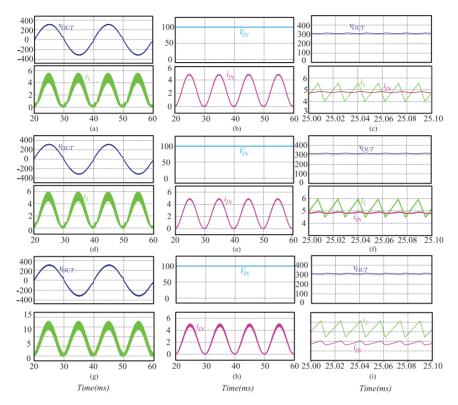

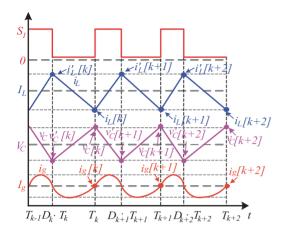

Fig. 3.3 shows the waveforms of the inductor currents and the voltages across the capacitors. A singularity of the buck mode is that all high-switching pulsations depend on the ripple of the input inductor current. Furthermore, the pulsation of the unfolding capacitor voltage depends on the current of the output inductor. The ripples of inductor  $L_f$  current depend on the capacitor voltages. Finally, the output capacitor fluctuation depends on the output inductor current. Thus, the filled areas of calculation in Fig. 3.3 are needed to obtain each high-frequency ripple:

$$L_{1}\Delta i_{L} = DT_{S} \cdot v_{IN} - \int_{0}^{DT_{S}} \left[ v_{C1}(t) \right] dt, L_{f}\Delta i_{Lf} = \int_{0}^{DT_{S}} \left[ v_{C1}(t) - v_{CS}(t) \right] dt,$$

(3.9)

$$C_{1}\Delta v_{C1} = \int_{\frac{DT_{S}}{2}}^{DT_{S}} \left[i_{L}(t) - i_{Lf}(t)\right] dt + \int_{0}^{\frac{DT_{S}}{2}} \left[i'_{L}(t) - i'_{Lf}(t)\right] dt , \qquad (3.10)$$

$$C_{s}\Delta v_{Cs} = \int_{\frac{DT_{s}}{2}}^{DT_{s}} \left[i_{lf}\left(t\right)\right] dt + \int_{0}^{\frac{D'T_{s}}{2}} \left[i'_{lf}\left(t\right)\right] dt, \qquad (3.11)$$

where  $\Delta i_L$  is a high-frequency ripple of the input inductor current,  $T_S$  equals the PWM period, D is a duty cycle, D' is an inverted duty cycle and equals 1-D,  $\Delta v_{CI}$  is a high-frequency ripple of the unfolding circuit voltage (across capacitor  $C_I$ ),  $\Delta i_{Lf}$  is a ripple of the grid inductance current,  $L_I$ ,  $L_f$ ,  $C_I$ ,  $C_S$  are nominal values of the passive elements.

Figure 3.3 High-frequency waveforms of ripples in the passive components: a voltage across the input inductor  $L_1$  (a), a triangular input inductor current (b), capacitor current ict (c),  $2^{nd}$  order shape voltage of the unfolding capacitor  $C_1$  (d), the voltage across output inductance  $L_1$  (e),  $3^d$  order shape of the output inductor current (f), the output capacitor current (g),  $4^{th}$  order shape of the output voltage (h).

The ripple of the input inductor current is a triangular waveform (Fig. 3.3b). The inductor current depends on the high-frequency ripple and the steady state value:

$$i_L\left(t\right) = \frac{\Delta i_L \cdot t}{D \cdot T_S} - \frac{\Delta i_L}{2} + i_o, \quad i_L'\left(t\right) = \frac{\Delta i_L \cdot t}{D' \cdot T_S} + \frac{\Delta i_L}{2} + i_o. \tag{3.12}$$

As mentioned, the buck mode has two LC-filters; they are working continuously during the buck mode. Therefore, the capacitor of the first LC-filter has the second order high-frequency pulsation. It corresponds to a parabola shape, as shown in Fig. 3.3d. The voltage expression of the capacitor  $C_1$  during active state is as follows:

$$v_{C1}(t) = \frac{2 \cdot \Delta v_{C1} \cdot t^2}{(D \cdot T_S)^2} - \frac{2 \cdot \Delta v_{C1} \cdot t}{D \cdot T_S} + v_{OUT}.$$

(3.13)

The grid inductance current has the third order shape of ripple (Fig. 3.3f). The equations of the inductor current with an active and a zero state are shown below:

$$i_{Lf}(t) = \frac{2\Delta i_{Lf} \cdot t^3}{(D \cdot T_s)^3} - \frac{3\Delta i_{Lf} \cdot t^2}{(D \cdot T_s)^2} + \frac{\Delta i_{Lf}}{2} + i_o,$$

(3.14)

$$i'_{Lf}(t) = \frac{2\Delta i_{Lf} \cdot t^3}{(D' \cdot T_S)^3} + \frac{3\Delta i_{Lf} \cdot t^2}{(D' \cdot T_S)^2} - \frac{\Delta i_{Lf}}{2} + i_o.$$

(3.15)

The voltage across the grid capacitor has the fourth order shape pulsation (Fig. 3.3h), which depends on the steady state value and the pulsations across the grid capacitor in the active state:

$$v_{Cs}(t) = \frac{8\Delta v_{Cs} \cdot t^4}{5(D \cdot T_S)^4} - \frac{16\Delta v_{Cs} \cdot t^3}{5(D \cdot T_S)^3} + \frac{8\Delta v_{Cs} \cdot t}{5D \cdot T_S} + v_{OUT}.$$

(3.16)

Based on eq. (3.8)-(3.16) it is possible to obtain a linear system with 4 unknown variables. These unknown variables are ripples in passive components and the mathematical system has the following format:

$$\begin{cases}

\Delta i_{L} = \frac{\left(v_{IN} - v_{OUT}\right) \cdot v_{IN}}{L_{1} \cdot v_{OUT} \cdot f}, \Delta i_{Lf} = \frac{\left(\Delta v_{C} + \Delta v_{Cs}\right) \cdot v_{OUT}}{3 \cdot L_{f} \cdot v_{IN} \cdot f}, \\

\Delta v_{C1} = \frac{4 \cdot \Delta i_{L} + 5 \cdot \Delta i_{Lf}}{32 \cdot C_{1} \cdot f}, \Delta v_{Cs} = \frac{5 \cdot \Delta i_{Lf}}{32 \cdot C_{s} \cdot f}

\end{cases}$$

(3.17)

where f is the PWM frequency. Solving of the system (3.17) gives the equations of the ripple in each passive component.

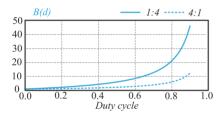

Table 3.2 Expressions of passive components and duty cycle for buck and boost modes.

| •                    |                                                                                                           | , , ,                                                                                                      |                                                                                                                                            |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tanalagu             | Buck-boos                                                                                                 | t inverter                                                                                                 | Twisted buck-boost inverter                                                                                                                |  |  |

| Topology             | based on unfolding                                                                                        | g circuit (Fig. 3.1a)                                                                                      | based on unfolding circuit (Fig. 3.1b)                                                                                                     |  |  |

| Mode                 | Buck                                                                                                      | Boost                                                                                                      | Buck-Boost                                                                                                                                 |  |  |

| Duty cycle           | $rac{\left  v_{_{REF}}  ight }{v_{_{IN}}}$                                                               | $\frac{\left v_{REF}\right -v_{IN}}{\left v_{REF}\right }$                                                 | $\frac{\left  \mathbf{v}_{REF} \right }{\left  \mathbf{v}_{REF} \right  + \mathbf{v}_{IN}}$                                                |  |  |

| Inductance $L_I$     | $\frac{v_{OUT} \cdot V_M \cdot \left(v_{IN} - v_{OUT}\right)}{2 \cdot K_L \cdot P \cdot v_{IN} \cdot f}$  | $\frac{v_{IN}^2 \cdot \left(v_{OUT} - v_{IN}\right)}{2 \cdot K_L \cdot P \cdot v_{OUT} \cdot f}$           | $\frac{v_{OUT} \cdot V_M \cdot v_{IN}^2}{2 \cdot K_L \cdot P \cdot \left(v_{OUT} + v_{IN}\right) \cdot \left(V_M + v_{IN}\right) \cdot f}$ |  |  |

| Inductance $L_{\!f}$ | $\frac{v_{OUT} \cdot V_M^2 \cdot \left(K_C + K_{Cs}\right)}{6 \cdot K_{Lf} \cdot P \cdot v_{IN} \cdot f}$ | $\frac{V_M^2 \cdot \left(4 \cdot K_C + 5 \cdot K_{Cs}\right)}{64 \cdot K_{Lf} \cdot P \cdot f}$            | $\frac{V_M^2 \cdot \left(4 \cdot K_C + 5 \cdot K_{Cs}\right)}{64 \cdot K_{Lf} \cdot P \cdot f}$                                            |  |  |

| Capacitor $C_I$      | $\frac{P \cdot \left(4 \cdot K_L + 5 \cdot K_{Lf}\right)}{16 \cdot K_C \cdot V_M^2 \cdot f}$              | $\frac{2 \cdot P \cdot (v_{OUT} - v_{IN})}{K_C \cdot V_M \cdot v_{OUT}^2 \cdot f}$                         | $\frac{2 \cdot P \cdot v_{OUT}^2}{K_C \cdot V_M^3 \left(v_{OUT} + v_{IN}\right) \cdot f}$                                                  |  |  |

| Capacitor $C_s$      | $\frac{5 \cdot K_{Lf} \cdot P}{16 \cdot K_{Cs} \cdot V_M^2 \cdot f}$                                      | $\frac{2 \cdot P \cdot K_{Lf} \cdot (v_{OUT} - v_{IN})}{3 \cdot K_{Cs} \cdot V_M^2 \cdot v_{OUT} \cdot f}$ | $\frac{2 \cdot P \cdot K_{Lf} \cdot v_{OUT}}{3 \cdot K_{Cs} \cdot V_M^2 \left(v_{OUT} + v_{IN}\right) \cdot f}$                            |  |  |

| Point of maximum     | $v_{OUT} = \frac{v_{IN}}{2}$                                                                              | $v_{OUT} = V_M$                                                                                            | $v_{OUT} = V_M$                                                                                                                            |  |  |

Usually, the ripple factor is used for the calculation of the passive elements:

$$K_{L} = \frac{\Delta i_{L}}{I_{LMAX}}, K_{Lf} = \frac{\Delta i_{Lf}}{I_{LfMAX}},$$

(3.18)

$$K_{C} = \frac{\Delta v_{C1}}{V_{C1MAX}}, K_{Cs} = \frac{\Delta v_{Cs}}{V_{CsMAX}},$$

(3.19)

where  $I_{LMAX}$ ,  $I_{LfMAX}$  are the maximum current values in inductances,  $V_{CIMAX}$ ,  $V_{CSMAX}$  are the peaks of the capacitor voltages.

The next step of the calculation is to find the maximum ripple during the grid period because each expression depends on the phase of the output voltage. Taking the derivative reveals the maximum of the ripple.

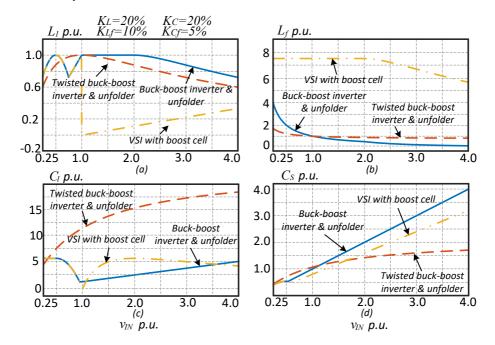

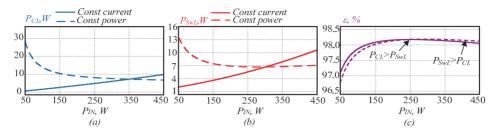

Tables 3.2 and 3.3 contain the expressions with the values of passive components for the considered family of topologies. The maximum pulsation in the buck mode corresponds the point when the output voltage equals half of the input voltage. The point of maximum of the twisted buck-boost inverter coincides with boost mode points in another topology. The presented calculation approach allows to obtain values of the passive components with the predefined ripples.

Table 3.3 Values of passive components as a function of converter parameters.

| Topology                          | Conventional VSI with boost cell (Fig. 2.2a)                                                       |                                                                                                             | Phase-integrated solution based on buckboost cell (Fig. 2.2b) $v_{AN} = \left(v_{OUT} + V_{M}\right)/2$                                                                                                                        |                                                                                                  |

|-----------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Mode                              | Buck                                                                                               | Boost                                                                                                       | Buck Boost                                                                                                                                                                                                                     |                                                                                                  |

| Inductanc e $L_I$                 | $\frac{v_{IN}^2 \cdot K_C}{16 \cdot K_L \cdot P \cdot f}$                                          | $\frac{v_{IN}^2 \cdot \left(v_{OUT} - v_{IN}\right)}{2 \cdot K_L \cdot P \cdot v_{OUT} \cdot f}$            | $\frac{v_{\scriptscriptstyle AN} \cdot V_{\scriptscriptstyle M} \cdot \left(v_{\scriptscriptstyle IN} - v_{\scriptscriptstyle AN}\right)}{2 \cdot K_{\scriptscriptstyle L} \cdot P \cdot v_{\scriptscriptstyle IN} \cdot f}$   | $\frac{v_{lN}^2 \cdot \left(v_{AN} - v_{lN}\right)}{2 \cdot K_L \cdot P \cdot v_{AN} \cdot f}$   |

| Inductanc e $L_f(L_{fl}, L_{f2})$ | $\frac{V_{M} \cdot v_{OUT} \cdot (v_{IN} - v_{OUT})}{4 \cdot K_{Lf} \cdot P \cdot v_{IN} \cdot f}$ | $\frac{V_M^2 \cdot \left(4 \cdot K_C + 5 \cdot K_{Cs}\right)}{64 \cdot K_{Lf} \cdot P \cdot f}$             | $\frac{v_{\scriptscriptstyle AN} \cdot V_{\scriptscriptstyle M}^2 \cdot \left(K_{\scriptscriptstyle C} + K_{\scriptscriptstyle Cs}\right)}{6 \cdot K_{\scriptscriptstyle Lf} \cdot P \cdot v_{\scriptscriptstyle IN} \cdot f}$ | $\frac{V_M^2 \cdot \left(4 \cdot K_C + 5 \cdot K_{Cs}\right)}{64 \cdot K_{Lf} \cdot P \cdot f}$  |

| `Capacitor $C_I$                  | $\frac{2 \cdot P \cdot \left(v_{IN} - v_{OUT}\right)}{K_C \cdot v_{IN}^3 \cdot f}$                 | $\frac{2 \cdot P \cdot \left(v_{OUT} - v_{IN}\right)}{K_C \cdot V_M \cdot v_{OUT}^2 \cdot f}$               | $\frac{P \cdot \left(4 \cdot K_L + 5 \cdot K_{Lf}\right)}{16 \cdot K_C \cdot V_M^2 \cdot f}$                                                                                                                                   | $\frac{2 \cdot P \cdot (v_{AN} - v_{IN})}{K_C \cdot V_M \cdot v_{AN}^2 \cdot f}$                 |

| Capacitor $C_S$                   | $\frac{P \cdot K_{L_g}}{4 \cdot K_{C_g} \cdot V_M^2 \cdot f}$                                      | $\frac{2 \cdot P \cdot K_{Lg} \cdot (v_{OUT} - v_{IN})}{3 \cdot KCg \cdot V_{M}^{2} \cdot v_{OUT} \cdot f}$ | $\frac{5 \cdot K_{Lf} \cdot P}{32 \cdot K_{Cs} \cdot V_M^2 \cdot f}$                                                                                                                                                           | $\frac{P \cdot K_{Lf} \cdot (v_{AN} - v_{IN})}{3 \cdot K_{Cs} \cdot V_M^2 \cdot v_{AN} \cdot f}$ |

| Point of maximum                  | $v_{OUT} = \frac{v_{IN}}{2}$                                                                       | $v_{OUT} = V_M$                                                                                             | $v_{OUT} = \frac{v_{IN}}{2}$                                                                                                                                                                                                   | $v_{OUT} = V_M$                                                                                  |

Table 3.4 Current and voltage stress across passive components as a function of converter parameters.

| Topology                                                            | Buck-boost<br>inverter based on<br>unfolding circuit<br>(Fig. 3.1a) |                                            | Twisted buck-<br>boost inverter<br>based on<br>unfolding circuit<br>(Fig. 3.1b) | Conventional VSI<br>with boost cell<br>(Fig. 2.2a) |       | Phase-integrated solution based on buck-boost cell (Fig. 2.2b) |                                              |  |

|---------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|-------|----------------------------------------------------------------|----------------------------------------------|--|

| Mode                                                                | Buck                                                                | Boost                                      | Buck-boost                                                                      | Buck                                               | Boost | Buck                                                           | Boost                                        |  |

| Maximum current Inductance $L_I$                                    | $\frac{2 \cdot P}{V_{\scriptscriptstyle M}}$                        | $\frac{2 \cdot P}{v_{IN}}$                 | $\frac{2 \cdot P}{v_{IN}} + \frac{2 \cdot P}{V_M}$                              | $\frac{2 \cdot P}{v_{\scriptscriptstyle IN}}$      |       | $\frac{2 \cdot P}{V_{\scriptscriptstyle M}}$                   | $\frac{2 \cdot P}{V_{\scriptscriptstyle M}}$ |  |

| Maximum current Inductance $L_f$ $(L_{f1}, L_{f2})$                 |                                                                     | $rac{2\cdot P}{V_{\scriptscriptstyle M}}$ |                                                                                 |                                                    |       |                                                                |                                              |  |

| Maximum voltage Capacitor $C_{I_s}$                                 |                                                                     |                                            |                                                                                 | $V_{\scriptscriptstyle M}$                         |       |                                                                |                                              |  |

| Total voltage<br>stress across<br>high-<br>switching<br>transistors | $2 \cdot V_M + 2 \cdot V_{IN}$ $2 \cdot V_M +$                      |                                            | $2 \cdot V_M + 2 \cdot V_{IN}$                                                  | $4 \cdot V_{_M}$                                   |       | $4 \cdot V_M + 4$                                              | $1 \cdot V_{_{I\!N}}$                        |  |

| Total voltage<br>stress across<br>low-switching<br>transistors      | 4.                                                                  | $V_{\scriptscriptstyle M}$                 | $4 \cdot V_{\scriptscriptstyle M}$                                              | $2 \cdot V_{\scriptscriptstyle M}$                 |       | 0                                                              |                                              |  |

In advance, Table 3.4 shows the current and voltage stress across passive components as a function of converter parameters for all compared topologies. It will be used for further comparative evaluation. Equations contain input power P, maximum output voltage  $V_M$  and input voltage  $v_{IN}$  and output voltage  $v_{OUT}$ . The output voltage corresponds to the general case of ac and dc modes. If the dc mode is considered, this value is equal to the maximum output voltage  $V_M$ , while in ac mode it is the absolute value of sinusoidal voltage waveform.

Output filter ( $L_i$ ) in the case of buck operation of BVSI is calculated according to the classical approach that takes into account the THD of the output current rated for 75% of maximum output power. This design approach does not differ from any other conventional inverter. It includes  $V_{INV}$  output high-frequency component of the inverter voltage before filter.

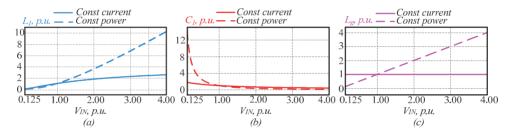

#### 3.2 Verification of the Filter Design

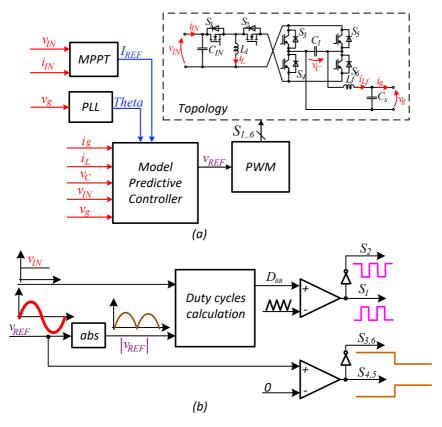

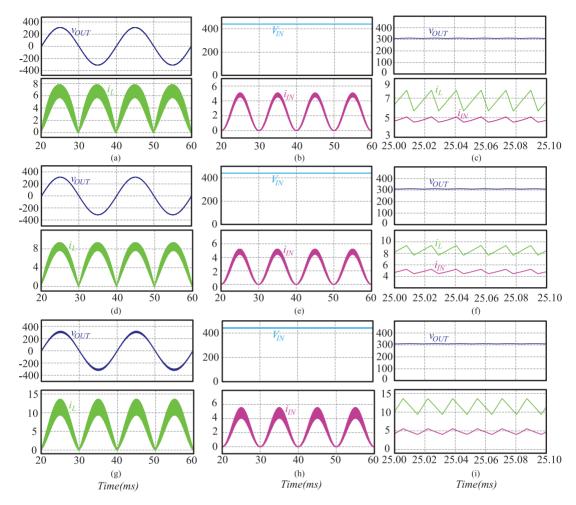

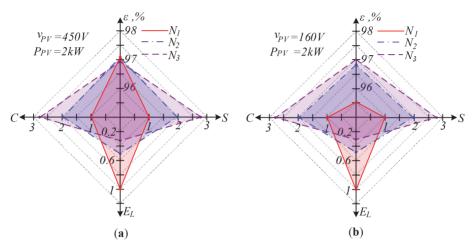

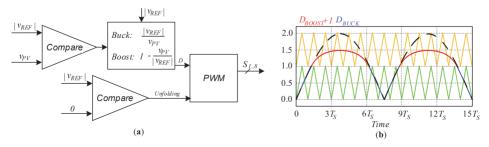

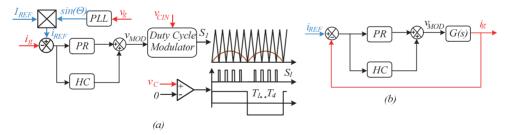

#### 3.2.1 Special Modulation Techniques

Several modulation techniques can be used for the proposed topologies. In general, the modulation method can lead to different conduction and switching loss, computational time, and quality of the output current and voltage. During calculation of the duty cycle for an open-loop system some reference signal such as  $v_{REF}$  should be used. Basically, the reference signal corresponds to the expected output voltage. In the case of a grid connected closed-loop system the control block uses MPC for a generating reference signal. It is possible to highlight two main cases: the input voltage is less than the amplitude of the reference voltage  $v_{REF}$  and when the input voltage is higher than the

peak of  $v_{REF}$ . In the first case, the converter will operate in buck and boost mode, depending on the comparison between input voltage and instantaneous reference value, as shown in Fig. 3.4a. If input voltage is higher than the reference signal, the buck mode with buck duty cycle is chosen:

$$D_{BUCK} = \frac{\left| v_{REF} \right|}{v_{DV}}.$$

(3.20)

where reference signal  $v_{REF}$  is taken as absolute value because the output side is kept as positive for the input side during a negative half cycle.

Otherwise, the converter will enter boost mode with a corresponding duty cycle:

$$D_{BOOST} = \frac{|v_{REF}| - v_{IN}}{|v_{RFF}|}.$$

(3.21)

where  $D_{BOOST}$  is a duty cycle of the switch  $S_3$ , while the main buck switch  $S_1$  is always turned on.

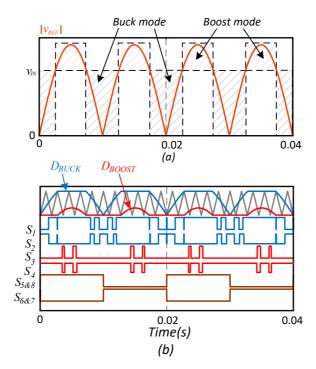

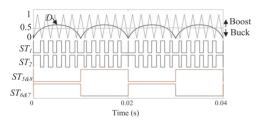

These duty cycles are compared with high-frequency carrier signals to generate gate signals for each corresponding switch. At the same time, the unfolding signals can be derived by comparing the reference signal  $v_{\it REF}$  with zero. The frequency of the unfolding circuit is the same as industrial grid frequency and equals 50 Hz. Fig. 3.4b shows the principle of signal generation for buck, boost and unfolding circuit switches. This case corresponds to a situation where the input voltage is lower than a peak of the reference signal. The modulation technique discussed is valid for a buck-boost inverter based on the unfolding circuit.

Figure 3.4 Switching signals generation for the buck-boost inverter based on unfolding: the case when  $v_{IN}$  is lower than the peak value of  $v_{REF}$  (a) and PWM signals of each transistor (b).

The same approach is used for a twisted buck-boost inverter based on the unfolding circuit, but this circuit only works with one operational mode for the buck and boost feature. This regime can be called the buck-boost mode.

The duty cycle similarly depends on the absolute value of the reference signal, and is calculated as follows:

$$D_{BB} = \frac{|v_{REF}|}{|v_{REF}| + v_{IN}},$$

(3.22)

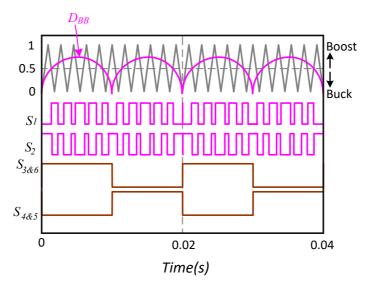

where  $D_{\it BB}$  represents the duty cycle of buck-boost mode for switch  $S_{\it I}$ . The unfolding signals are generated in the same way as in the first circuit. Fig 3.5 shows the principle of signal generation for the twisted buck-boost inverter based on the unfolding circuit. If apply duty cycle more than 0.5 the boost mode will be chosen, otherwise the system will work in buck mode.

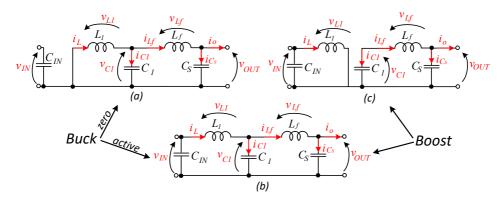

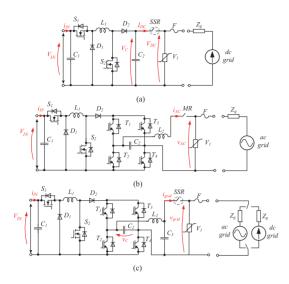

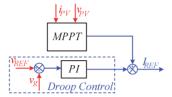

Fig. 3.6 $\alpha$  describes the operation principle of the conventional solution for universal PV application. A non-conventional modulation approach is considered for implementation. In some research studies it was called a time-sharing dual mode control scheme [53], [54]. A very similar control approach is called cooperative control [55]. The shape of the voltage across capacitor  $C_1$  follows the modulation voltage in the boost mode. In this case only boost transistors are working in the high-switching mode, while VSI transistors perform an unfolding function.

Figure 3.5 Switching signals generation for twisted buck-boost inverter based on the unfolding inverter in a case when  $v_{IN}$  is lower than the peak value of reference signal.

Figs. 3.6b and 3.6c illustrate the concept of universal applicability of the Phase-Modular Converter (PMC). In the first case, internal commutators (switches)  $SW_1$ - $SW_3$  are configured to provide sinusoidal output voltage (Fig. 3.6b).  $SW_{12}$  is conducting, while other commutators are switched off. In the second case, the commutators (switches)  $SW_1$  and  $SW_3$  are conducting, which leads to the connections of the positive output's terminals of each cell providing only the dc component. The interleaved mode that is activated in this case reduces the output and input current ripple.

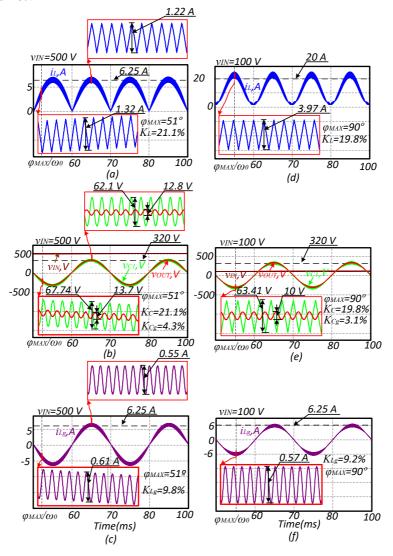

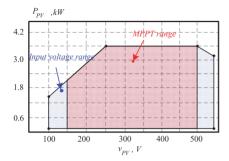

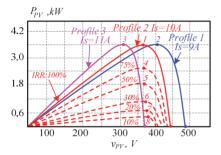

A simple open-loop system was chosen as verification. The values of the ripple factors should be such that they avoid discontinuous current mode in inductances. For example, the ripple factor of input inductance was set at 20%. The unfolding voltage factor was also 20%, while only 5% was set for the output LC-filter ripple factors. The output inductance ripple factor is 10%. The lower power causes significant current pulsations in the inductances, which is why it was decided to calculate passive elements under 1 kW. Moreover, the highest possible boost according to announced voltage range is 3.2. If the minimum input voltage equals 100 V, the maximum possible input power is 1 kW.

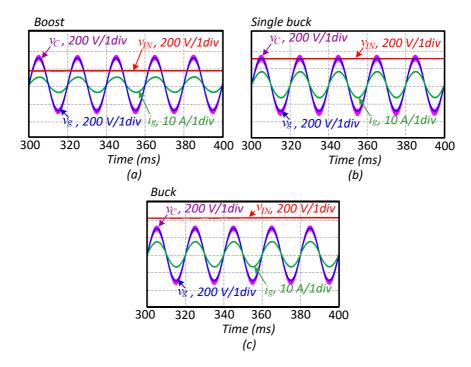

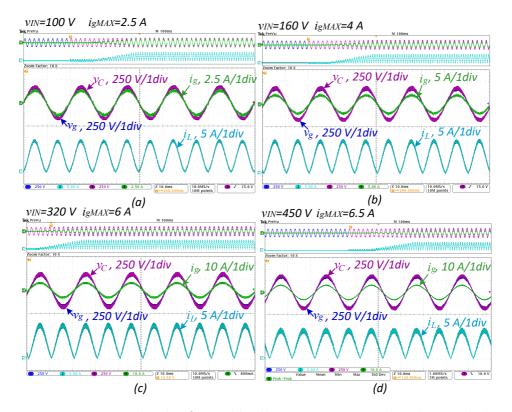

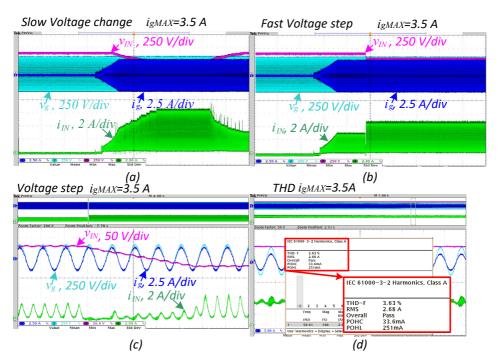

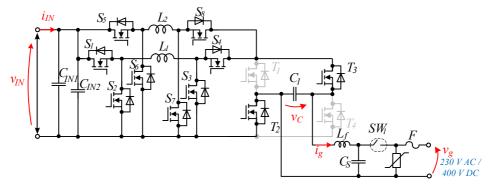

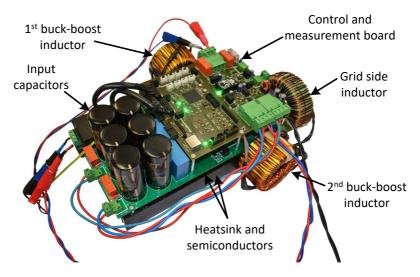

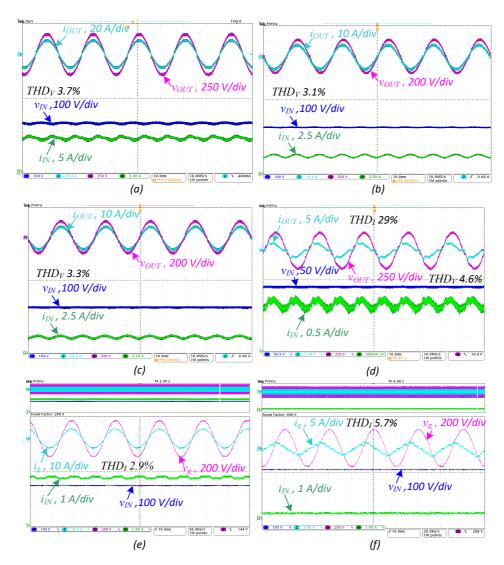

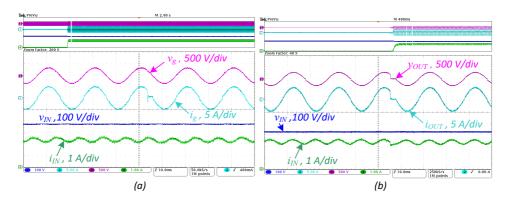

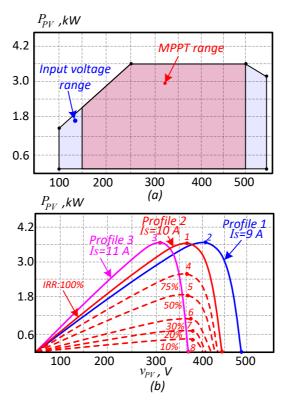

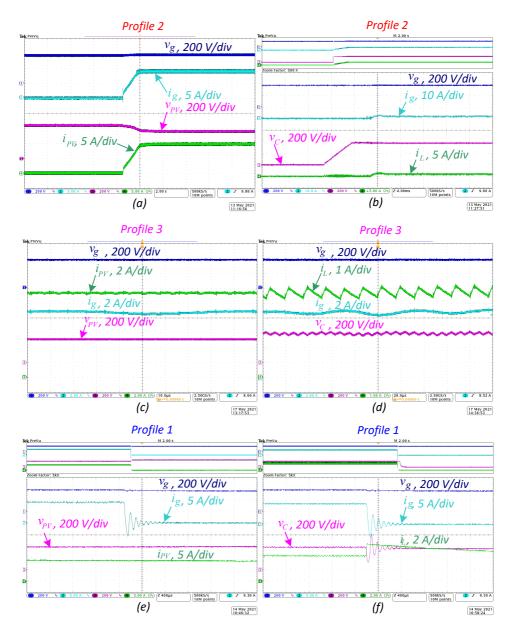

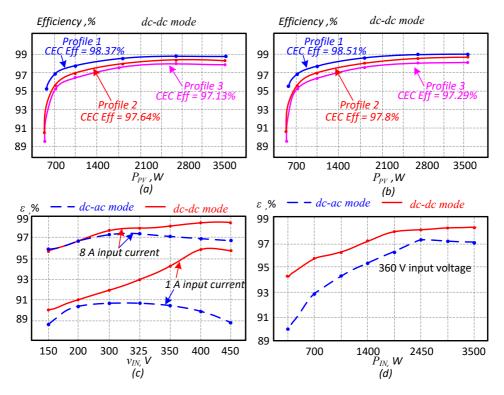

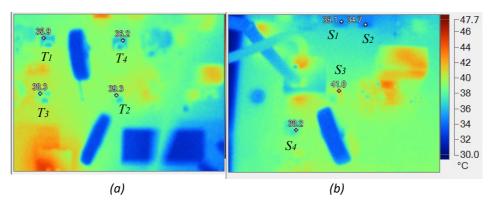

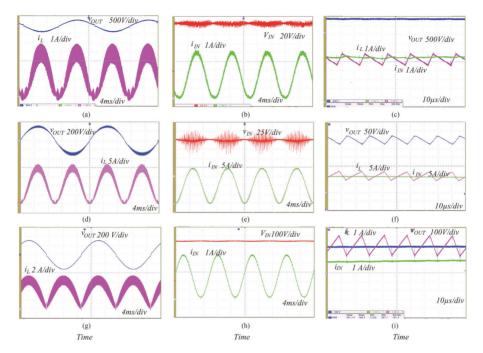

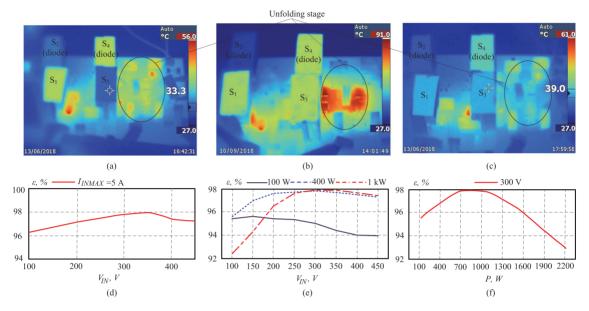

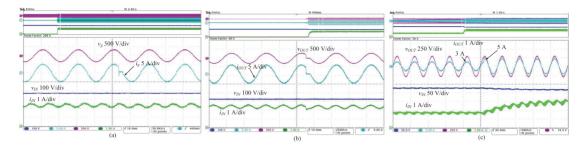

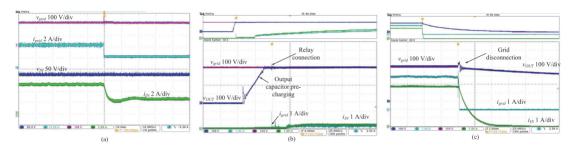

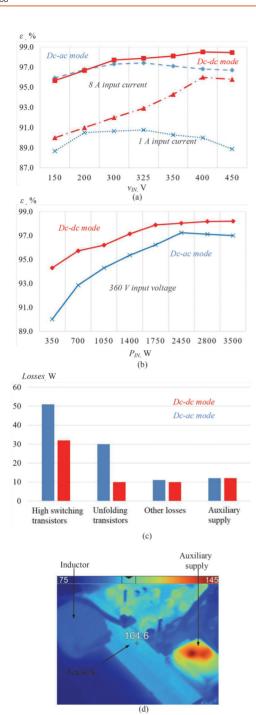

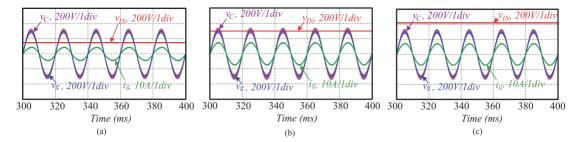

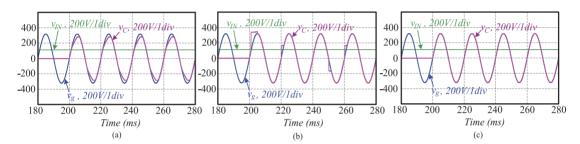

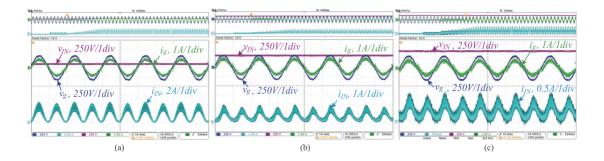

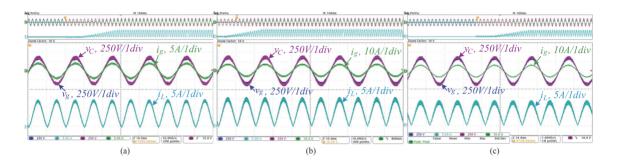

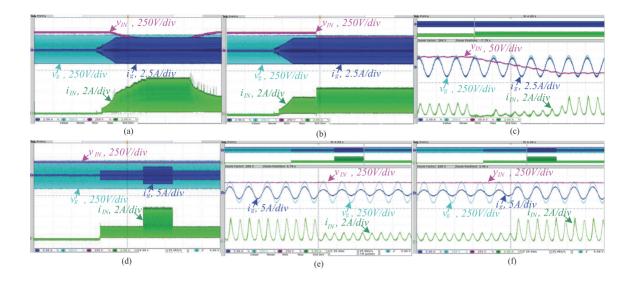

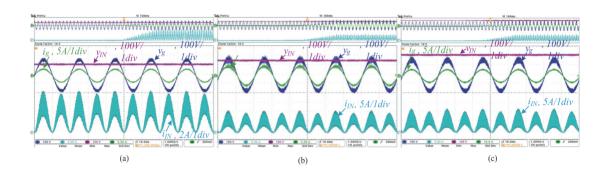

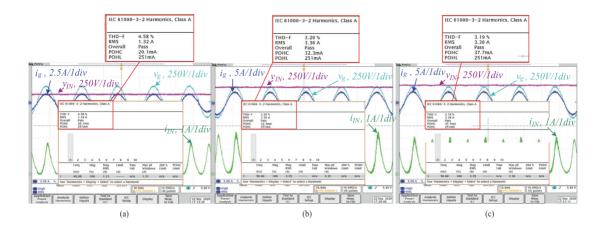

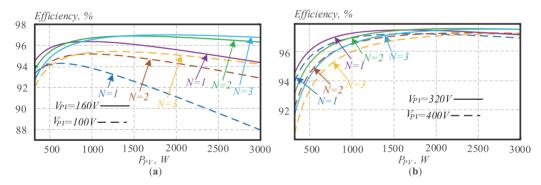

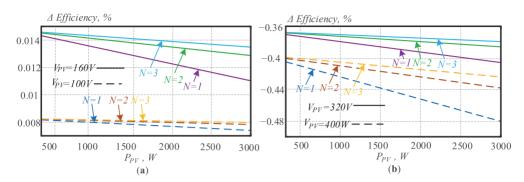

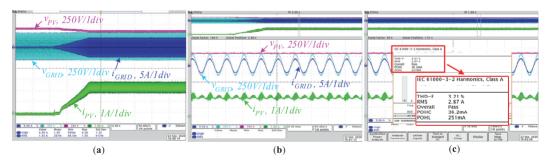

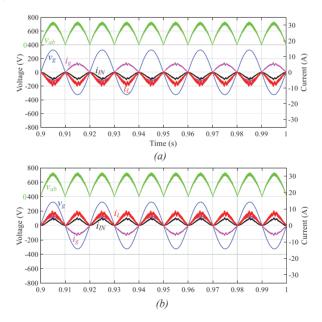

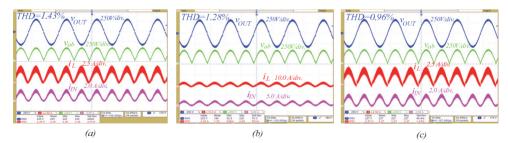

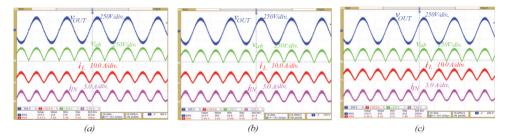

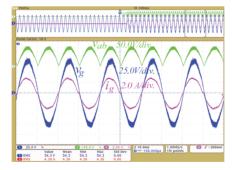

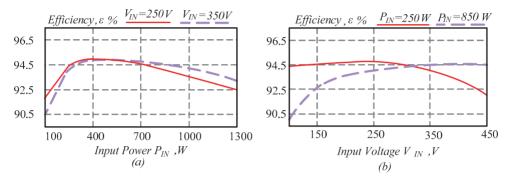

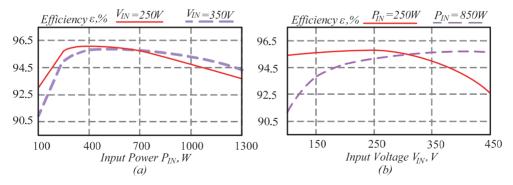

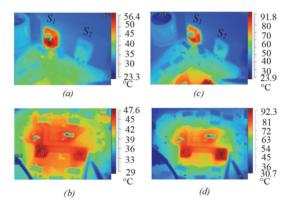

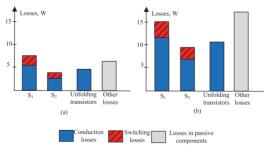

Figure 3.6 General operation illustration of the operation principle: boost and buck operations for conventional inverter with boost cell(a), phase-integrated solution based on buck-boost cell (b), dc-dc mode interleaved buck-boost cells (c).