#### **DOCTORAL THESIS**

# Area Efficient Design and Implementation of a Novel Divider Circuit Block

Udayan Sunil Patankar

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2025

# TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 29/2025

# Area Efficient Design and Implementation of a Novel Divider Circuit Block

**UDAYAN SUNIL PATANKAR**

TALLINN UNIVERSITY OF TECHNOLOGY

School of Information Technologies

Thomas Johann Seebeck Department of Electronics

This dissertation was accepted for the defense of the degree 25/04/2025

**Supervisor**: Dr. Ants Koel

Thomas Johann Seebeck Department of Electronics

Tallinn University of Technology

Tallinn, Estonia

**Co-supervisor**: Dr. Tamás Pardy

Thomas Johann Seebeck Department of Electronics

Tallinn University of Technology

Tallinn, Estonia

**Expert reviewer:** Prof. Emeritus Toomas Rang

Thomas Johann Seebeck Department of Electronics

Tallinn University of Technology

Tallinn, Estonia

**Opponents**: Prof. Dr. Serge Dos Santos, Associate Professor (Hab. Dir. Rech.)

INSA Centre Val de Loire, Blois Campus Department of Industrial Systems

signature

Inserm U1253 iBraiN- University of Tours

Tours, France

Prof. Dr. András Poppe

Department of Electron Devices

Budapest University of Technology and Economics (BME)

Budapest, Hungary

Defense of the thesis: 28/05/2025, Tallinn

#### **Declaration:**

Hereby, I declare that this doctoral thesis is my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for a doctoral or equivalent academic degree.

Udayan Sunil Patankar

Copyright: Udayan Sunil Patankar, 2025

ISSN 2585-6898 (publication)

ISBN 978-9916-80-297-7 (publication)

ISSN 2585-6901 (PDF)

ISBN 978-9916-80-298-4 (PDF)

DOI https://doi.org/10.23658/taltech.29/2025

Printed by Koopia Niini & Rauam

Patankar, U. S. (2025). *Area Efficient Design and Implementation of a Novel Divider Circuit Block* [TalTech Press]. https://doi.org/10.23658/taltech.29/2025

#### TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 29/2025

# **Uudne efektiivne jagamistehte riistvaraline** realisatsioon

**UDAYAN SUNIL PATANKAR**

#### **Contents**

| List of publications                                                                   | 7  |

|----------------------------------------------------------------------------------------|----|

| Author's contributions to the publications                                             | 8  |

| Abbreviations and terms                                                                | 9  |

| List of figures                                                                        | 12 |

| List of tables                                                                         | 13 |

| 1 Introduction                                                                         |    |

| 1.1 The scope and the organization of the thesis                                       |    |

| 1.2 Problem statement and research objectives                                          |    |

| 1.3 Thesis contribution                                                                | 18 |

| 2 Division circuit block – overview of division algorithms                             |    |

| 2.1 Importance of division circuit blocks                                              |    |

| 2.2 Division circuit block taxonomy                                                    |    |

| 2.2.1 Digit recurrence class (DRC)                                                     |    |

| 2.2.2 Very high radix digit recurrence class (VHRDRC)                                  |    |

| 2.2.3 Look-up table class (LTC)                                                        |    |

| 2.2.4 Functional iteration class (FIC)                                                 |    |

| 2.3 Hardware architectures                                                             |    |

| 2.4 Performance improvement techniques                                                 |    |

| 2.5 Summary of comparative analysis                                                    |    |

| 2.6 Chapter conclusion                                                                 |    |

| 3 Design methodology – objective, hypothesis, and algorithm for the proposed divide    | er |

| circuit block implementation                                                           |    |

| 3.1 Objective                                                                          | 31 |

| 3.2 Hypothesis                                                                         |    |

| 3.3 Introduction to the Vedic sutras                                                   |    |

| 3.3.1 Veshtanam sutra (by osculation)                                                  |    |

| 3.3.2 Lopana-Sthapanabhyam sutra (by elimination and retention)                        |    |

| 3.3.3 Aanurupyen sutra (proportionately or by suitable ratio)                          |    |

| 3.4 Introduction to the proposed novel OSP-Awadhoot divider circuit block              |    |

| 3.6 The Awadhoot matrix for iterative circuit elements of the processing circuit stage |    |

| 3.7 The working principle of the proposed novel USP-Awadhoot divider circuit block.    |    |

| 3.8 Summary of the proposed USP-Awadhoot divider realization                           |    |

| 3.9 Chapter conclusion                                                                 | 47 |

| 4 Complex division by Baudhayan-Pythagoras triplet method using a novel USP-           |    |

| Awadhoot divider                                                                       | 48 |

| 4.1 Complex division by Baudhayan-Pythagorean triplet method using the proposed        |    |

| USP-Awadhoot divider                                                                   |    |

| 4.2 Circuit illustration and state diagram                                             |    |

| 4.3 Summary                                                                            |    |

| 4.4 Chapter conclusion                                                                 |    |

| 5 Implementation and performance statistics                                            | 58 |

| 5.1 Implementation and performance analysis of the USP-Aw | adhoot divider circuit |

|-----------------------------------------------------------|------------------------|

| block                                                     | 60                     |

| 5.2 Waveform analysis                                     | 67                     |

| 5.3 Summary of comparative analysis                       | 69                     |

| 5.4 Chapter conclusion                                    | 75                     |

| Conclusion and future work prospects                      | 76                     |

| References                                                | 78                     |

| Acknowledgments                                           | 92                     |

| Abstract                                                  | 93                     |

| Lühikokkuvõte                                             | 95                     |

| Appendix 1                                                | 97                     |

| Appendix 2                                                | 135                    |

| Appendix 3                                                | 145                    |

| Appendix 4                                                | 149                    |

| Appendix 5                                                | 179                    |

| Appendix 6                                                | 189                    |

| Appendix 7                                                | 193                    |

| Curriculum Vitae                                          | 198                    |

| Elulookirjeldus                                           | 200                    |

#### **List of publications**

The list of the author's publications, upon which the thesis has been prepared:

- Patankar, Udayan.; Koel, Ants, "Review of Basic Classes of Dividers Based on Division Algorithm" in IEEE Access, Vol. 9, 23035–23069. DOI: 10.1109/ACCESS.2021. 3055735.

- II Patankar, Udayan; Koel, Ants; Patankar, Sunil; Flores, Miguel, "Area Efficient Hexadecimal Divider Circuit Implementation Based on USP-Awadhoot Division Algorithm" in 2021 IEEE International Conference on Engineering, Technology, and Innovation (ICE/ITMC), 2021, pp. 1–8. DOI: 10.1109/ICE/ITMC52061.2021.9570263.

- III Patankar, Udayan; Koel, Ants; Patankar, Sunil; Flores, Miguel, "Division Method And Circuit" in PTC the International Patent System, International Bureau of the World Intellectual Property Organization, application no.: PCT/IB 2021/054942, submission no.: 054942, Date: 06 June 2021; published on 15-12-2022, publication no WO2022259009. https://patentscope.wipo.int

- IV Patankar, Udayan; Koel, Ants; Patankar, Sunil; Flores, Miguel, "Novel Data Dependent Divider Circuit Block Implementation for Complex Division and Area Critical Applications," in NATURE Scientific Reports. Sci Rep 13, 3027 (2023). https://doi.org/10.1038/s41598-023-28343-3.

#### Author's contributions to the publications

The author's contributions to the papers in this thesis were:

- During the research, the author aimed to establish common study points for comparing the various possible division circuit implementations and application possibilities. After surveying existing solutions, the author analyzed and evaluated their conversion logic, critical procedures, constraints, and implementation statistics to determine the optimal option for a given application. In addition, he proposed a new division algorithm development goal to implement dynamic separate scaling operations for input operands to save space overhead and eliminate overlapping conversion logic sections. Furthermore, he drafted the entire manuscript with input and feedback from co-authors and supervisors.

- II The author proposed a hexadecimal number system for developing a divider circuit based on a novel USP Awadhoot digit recurrence division algorithm to improve the implementation area. He simulated the VHDL code for the proposed divider circuit using Xilix's VIVADO and Intel Quartus Prime Lite design tools. He also developed a table of all possible input combinations to validate its simulation and hardware implementation. Furthermore, he drafted the entire manuscript with co-authors' feedback, and published the article under the guidance of supervisors.

- III The author proposed a divider circuit implementation based on a novel USP-Awadhoot division algorithm. He designed the finite state machine steps for the proposed divider implementation and developed the Awadhoot matrix computation scheme, simulating the VHDL code for hardware implementation. He also drafted the complete manuscript with co-authors' feedback, and published the article under the guidance of supervisors.

- IV This article is the extended version of papers II and III. The author presented mathematical models for the proposed novel USP-Awadhoot digit recurrence division algorithm and Baudhayan-Pythagoras triplet algorithm. He proposed the 8-bit, 16-bit, 24-bit, and 31-bit implementations of the novel USP-Awadhoot digit recurrence division algorithm-based divider circuit. He conducted experiments to design, simulate, and verify the VHDL code for the proposed 8-bit, 16-bit, 24-bit, and 31-bit implementations. He designed the truth tables for verifying their performance and validated the results after simulations and hardware implementations. He also drafted the complete manuscript, with co-authors' feedback, and published the article under the guidance of supervisors.

#### **Abbreviations and terms**

| ALM                    | Arithmetic and Logical Module                          |

|------------------------|--------------------------------------------------------|

| Al                     | Artificial Intelligence                                |

| ASP                    | Analog Signal Processing                               |

| AGC                    | Automatic Gain Control                                 |

| $\overline{AQ}$        | Additional Quotient                                    |

| BN                     | Boron Nitride                                          |

|                        |                                                        |

| $C_D_d$                | Dividend complex number                                |

| $C_D_r$                | Divisor complex number                                 |

| cd_enable              | Complex enable                                         |

| $C_D_{d1}$             | USP-Awadhoot Dividend complex number                   |

| $C_D_{r_1}$            | USP-Awadhoot Divisor complex number                    |

| CLB                    | Configurable Logic Blocks                              |

| CLK                    | Clock signal                                           |

| CMOS                   | Complementary Metal Oxide Semiconductor                |

| CPI                    | Cycles per Instruction                                 |

| CPU                    | Central Processing Unit                                |

| $C_{-}Q$               | The final quotient complex number                      |

| $C_{-}Q_{i}$           | Imaginary number coefficient of USP-Awadhoot quotient  |

| $C_{-}Q_{r}$           | Real number coefficient of USP-Awadhoot quotient       |

| C_Rem                  | The final remainder complex number                     |

| $C\_Rem_i$             | Imaginary number coefficient of USP-Awadhoot remainder |

| $C\_Rem_r$             | The real number coefficient of USP-Awadhoot remainder  |

| $D_d$                  | The dividend                                           |

| $D_r$                  | The divisor                                            |

| DRC                    | Digit Recurrence Class                                 |

| DSP                    | Digital Signal Processing                              |

| Ec                     | Conduction band energy level                           |

| Ev                     | Valence band energy level                              |

| $e_r$                  | A small positive fractional value                      |

| FD                     | Flag Digit                                             |

| F <sub>d</sub> _enable | Enable signal for ASP Awadhoot Divider                 |

| FIC                    | Functional Iteration Class                             |

| FPGA                   | Field Programmable Gate Array                          |

| GaN                    | Gallium Nitride                                        |

| GaSe                   | Gallium Selenide                                       |

| GDA                    | Goldschmidt Division Algorithm                         |

| $GD_{dn}$              | Group Dividend                                         |

| GPU                    | Graphic Processing Unit                                |

| GQ                     | The final value of the group quotients                 |

|                        | Individual group quotient                              |

| $GQ_n$                 |                                                        |

| $GQ_{n-1}$             | Previous iteration group quotient                      |

| $G_rD_{dn}$            | Gross Dividend                                         |

| GSA                    | Generalized Svoboda algorithm                          |

| GSchA                  | Goldschmidt Algorithm                                  |

| GSEFIC      | Goldschmidt Series Expansion Type Functional Iteration Class     |

|-------------|------------------------------------------------------------------|

| HAC         | Hardware Architecture Class                                      |

| HT          | High Temperature                                                 |

| IC          | Integrated Circuit                                               |

| ICT         | Information and Communication Technologies                       |

| IoT         | Internet of Things                                               |

| I-V         | Current - Voltage                                                |

| LTC         | Look-Up Table Class                                              |

| Mat_Term1   | The first triplet matrix term                                    |

| Mat_Term2   | The second triplet matrix term                                   |

| $MD_r$      | Modified Divisor                                                 |

| MIC         | Many Integrated Cores                                            |

| MSB         | Most Significant Bit                                             |

| $ND_{dn}$   | Net Dividend                                                     |

| $ND_r$      | New Divisor                                                      |

| NRA         | Newton-Raphson Algorithm                                         |

| NRDRC       | Non-Restoring Type Digit Recurrence Class                        |

| NRFIC       | Newton–Raphson Type Functional Iteration Class                   |

| NSTA        | New Svoboda-Tung Algorithm                                       |

| NSTDRC      | New Svoboda-Tung Type Digit Recurrence Class                     |

| NZC         | Number of Zeros Cancelled                                        |

| OFDM        | Orthogonal Frequency Division Multiplexing                       |

| ρ           | Redundancy factor                                                |

| PLA         | Programmable Logic Array                                         |

| $PQ_n$      | Partial Quotient                                                 |

| Q           | The Quotient                                                     |

| $q_i$       | The quotient bit from the $j^{th}$ iteration                     |

| Q Result    | Quotient signal                                                  |

| QST         | Quotient Selection Look-up Table                                 |

| R           | Residue                                                          |

| $r_1$       | Complex number one is termed as $x_1 + y_1i$                     |

| $r_2$       | Complex number two is termed as $x_1 + y_1 i$                    |

|             | The remainder generated during the calculation of the additional |

| $R_{AQ}$    | quotient                                                         |

| RDRC        | Restoring Type Digit Recurrence Class                            |

| Rem Residue | Remainder signal                                                 |

| _           | The partial remainder of the $j^{th}$ iteration                  |

| $R_j$       | ·                                                                |

| RNG         | Random Number Generator Present Remainder                        |

| $R_n$       |                                                                  |

| $R_{n-1}$   | Previous Remainder                                               |

| RST         | Reset signal                                                     |

| SBD         | Signed binary digit                                              |

| SDRC        | Svoboda Type Digit Recurrence Class                              |

| SEA         | Series Expansion Algorithm                                       |

| Si          | Silicon                                                          |

| SiC         | Silicon Carbide                                                  |

| SOC       | System On Chip                                          |

|-----------|---------------------------------------------------------|

| SOI       | Silicon on Insulator                                    |

| SRT       | Sweeney-Robertson-Tocher                                |

| SRTDRC    | SRT Type Digit Recurrence Class                         |

| STA       | Svoboda-Tung Algorithm                                  |

| STDRC     | Svoboda-Tung Type Digit Recurrence Class                |

| SVD       | Singular value decomposition                            |

| T_Term    | The triplet term                                        |

| TP_Term1  | The first triplet product term                          |

| TP_Term2  | The second triplet product term                         |

| TP_Term3  | The third triplet product term                          |

| TP_Term4  | The fourth triplet product term                         |

| TSEA      | Taylor Series Algorithm                                 |

| TSEFIC    | Taylor Series Expansion Type Functional Iteration Class |

| $xD_d$    | Real number coefficient of Dividend complex number      |

| $xD_r$    | Real number coefficient of Divisor complex number       |

| $yD_d$    | Imaginary number coefficient of Dividend complex number |

| $yD_r$    | Imaginary number coefficient of Divisor complex number  |

| Valid_O/P | Computation Completion Acknowledgment                   |

| VHRDRC    | Very High Radix Digit Recurrence Class                  |

| VLC       | Variable Latency Class                                  |

| VLSI      | Very Large Scale Integration                            |

### List of figures

| Figure 1. Basic block diagram of the sensor package                              | 14     |

|----------------------------------------------------------------------------------|--------|

| Figure 2. The scope and the organization of the thesis                           | 16     |

| Figure 3. Division algorithm taxonomy                                            | 21     |

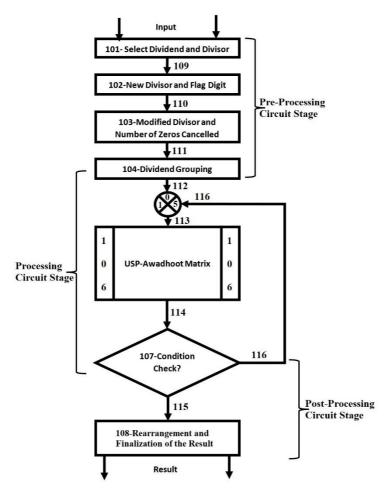

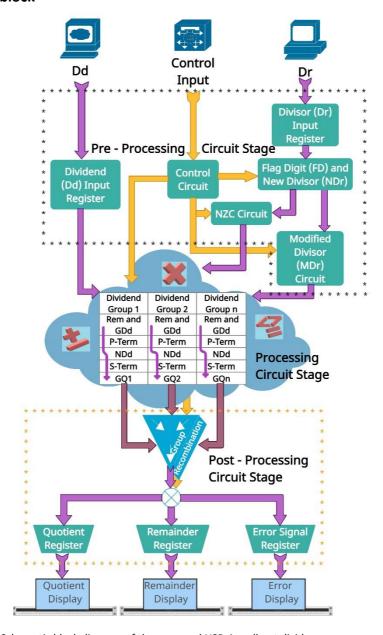

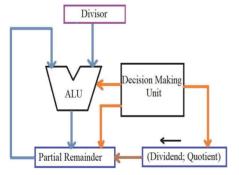

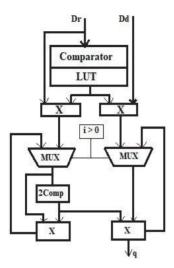

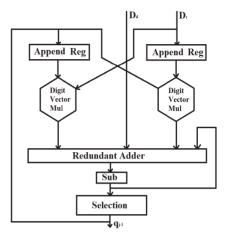

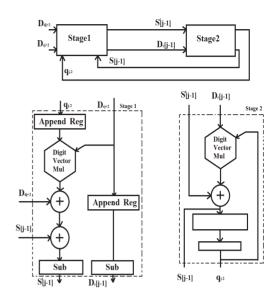

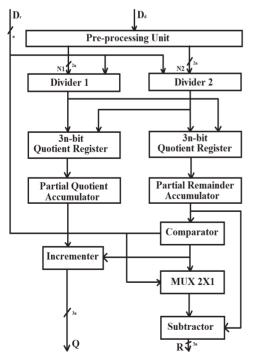

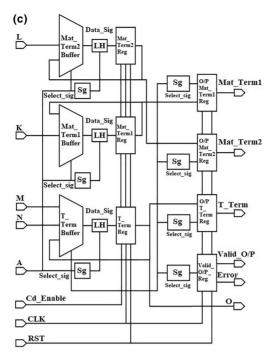

| Figure 4. Functional block diagram of the proposed novel USP-Awadhoot divider    | 34     |

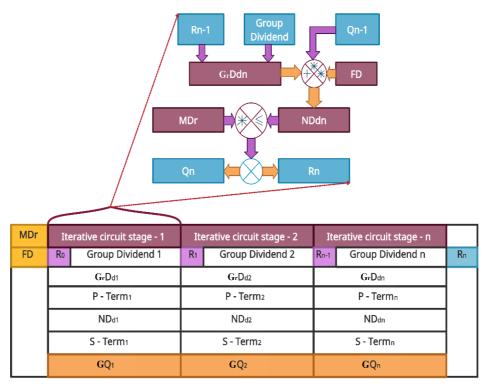

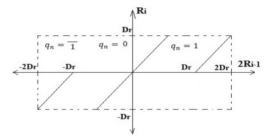

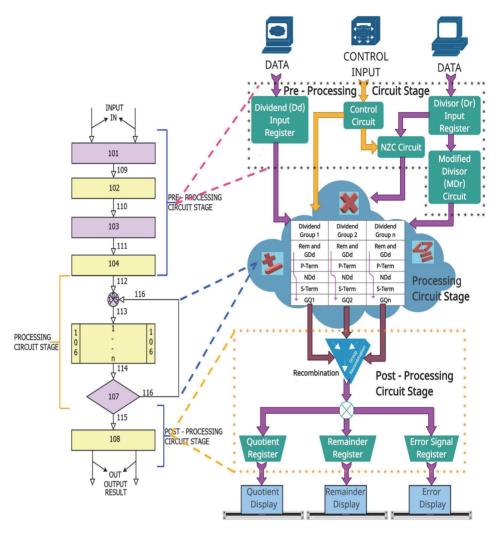

| Figure 5. The Awadhoot matrix                                                    | 37     |

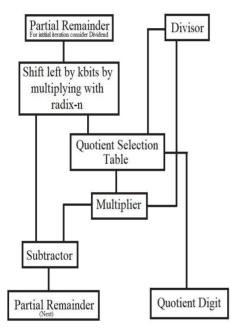

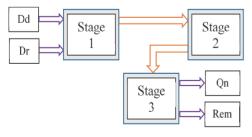

| Figure 6. Schematic block diagram of the proposed USP-Awadhoot divider           | 40     |

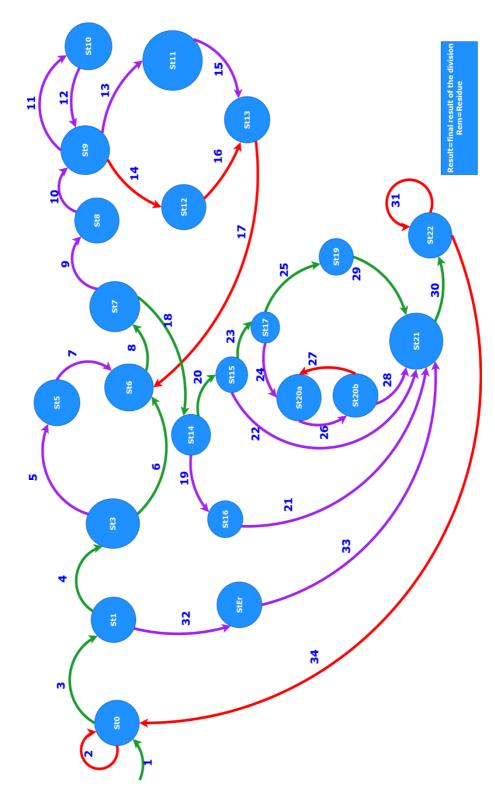

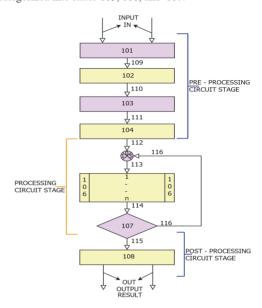

| Figure 7. The logic flow state diagram of the proposed USP-Awadhoot divider      | 44     |

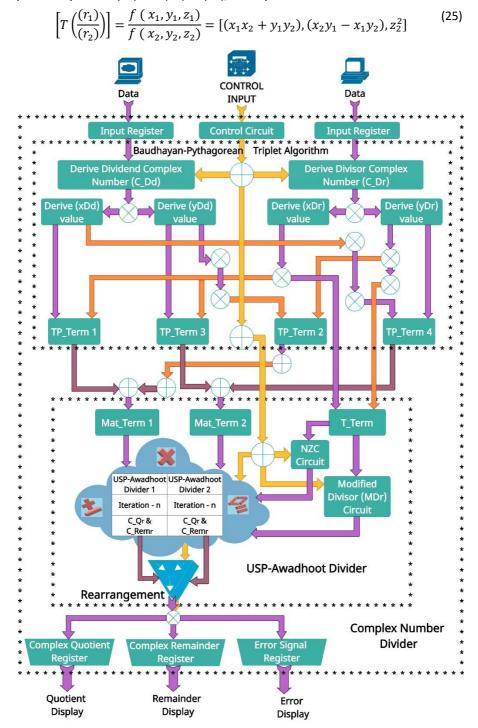

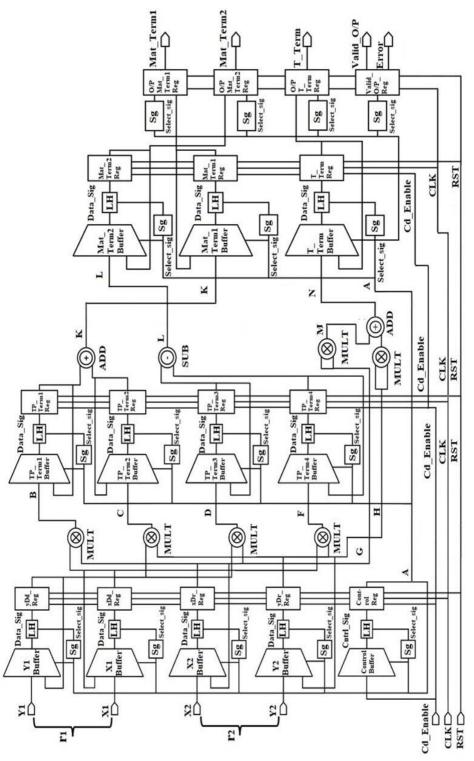

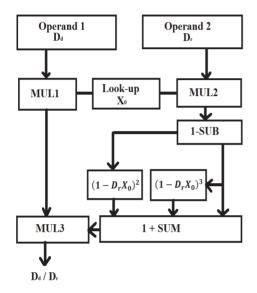

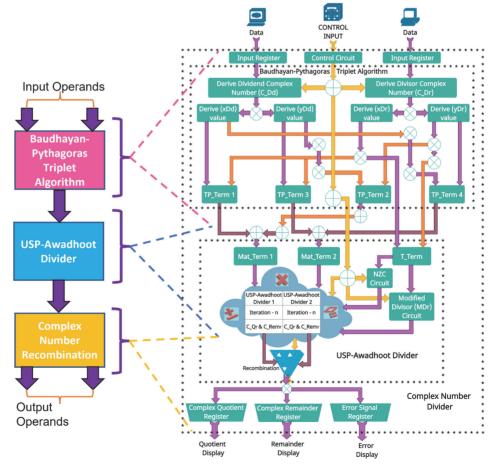

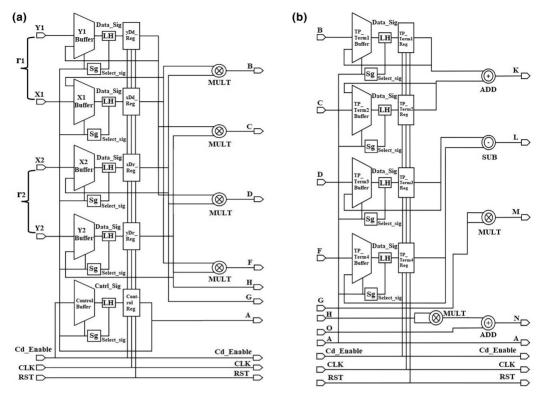

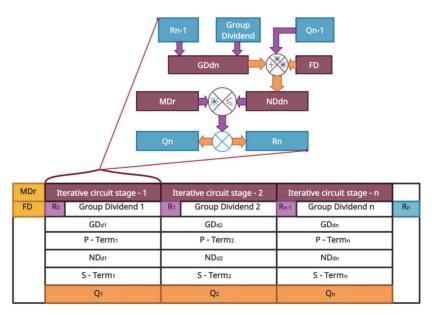

| Figure 8. Schematic block diagram of the complex divider                         | 50     |

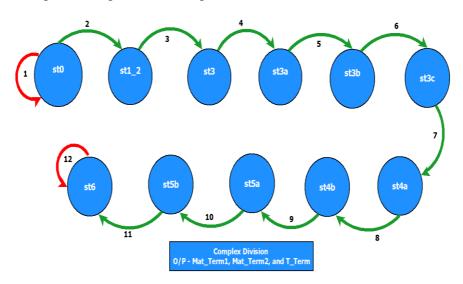

| Figure 9. State diagram of the proposed Baudhayan-Pythagorean Triplet algorithm  | 52     |

| Figure 10. Schematic diagram of the proposed Baudhayan-Pythagorean triplet sect  | ion of |

| the complex divider                                                              | 54     |

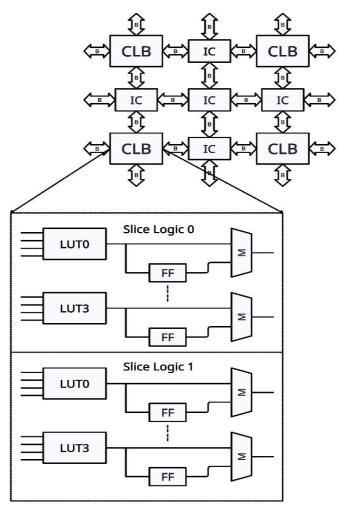

| Figure 11. Generalized architectural illustration of FPGA building blocks        | 59     |

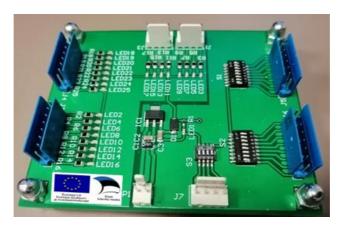

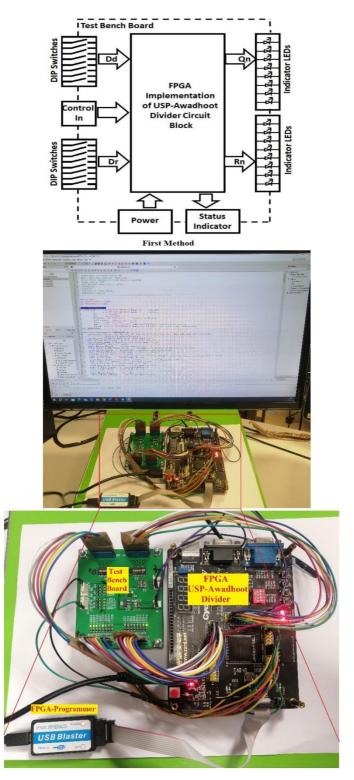

| Figure 12. Logic test bench board                                                |        |

| Figure 13. Test arrangements for the first method                                |        |

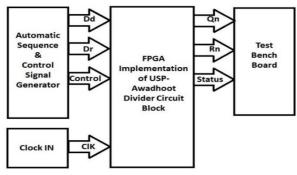

| Figure 14. Test arrangements for the second method                               | 62     |

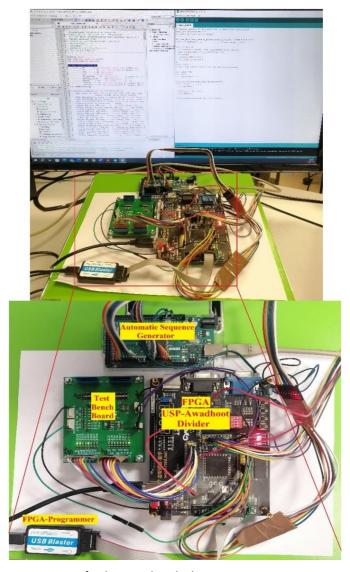

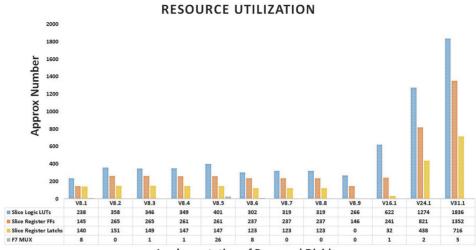

| Figure 15. Hardware resource utilization                                         | 64     |

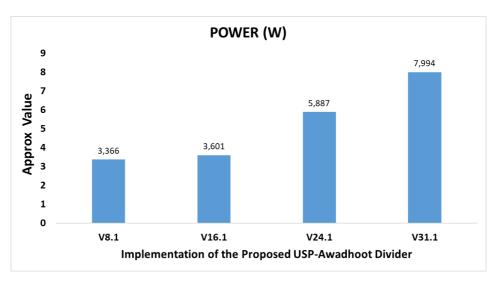

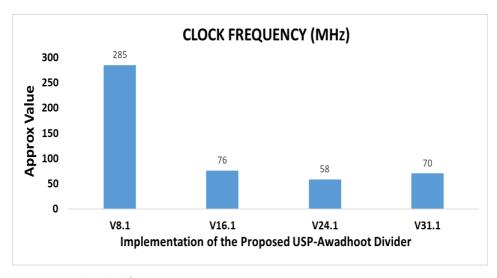

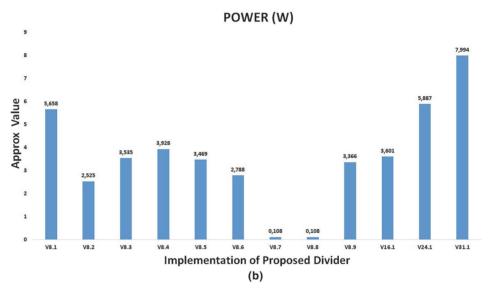

| Figure 16. Estimated power consumption                                           |        |

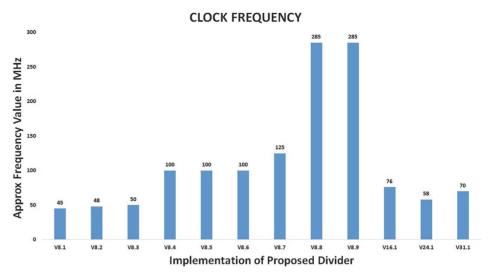

| Figure 17. Divider clock frequency                                               | 65     |

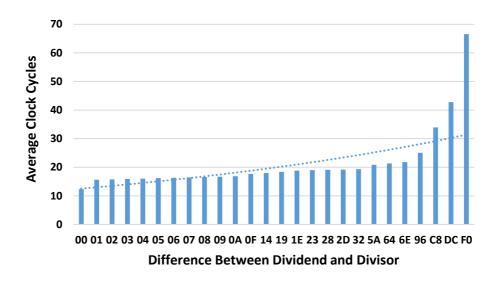

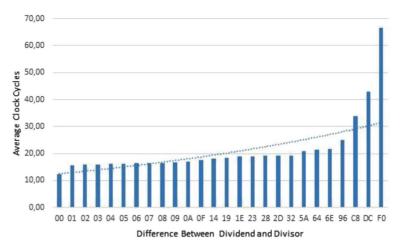

| Figure 18. Clock performance analysis based on the distance between the dividen  |        |

| the divisor                                                                      | 67     |

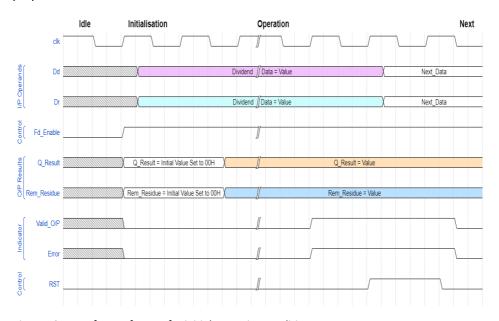

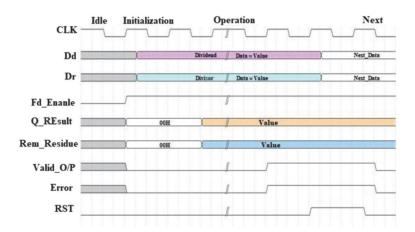

| Figure 19. Waveform reference for initial operating condition                    | 68     |

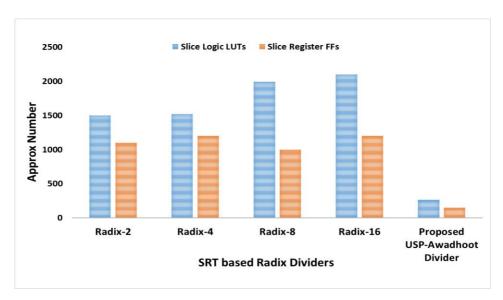

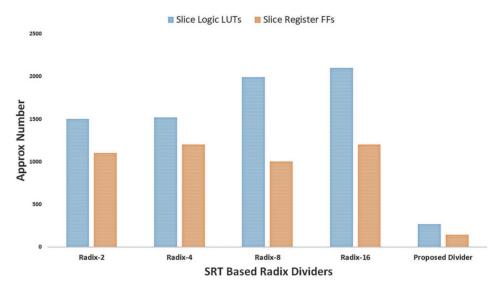

| Figure 20. Comparative analysis of the proposed USP-Awadhoot divider with the ra | adix-n |

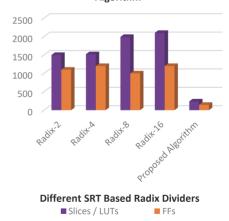

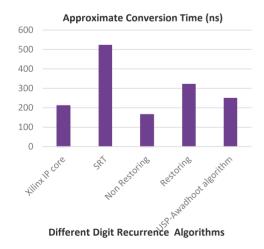

| based SRT divider                                                                | 70     |

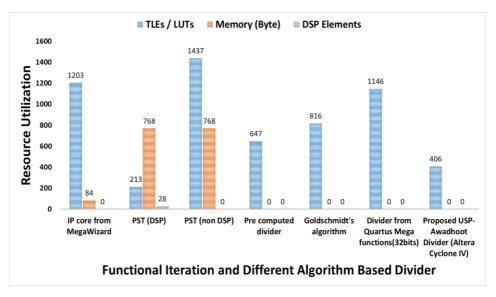

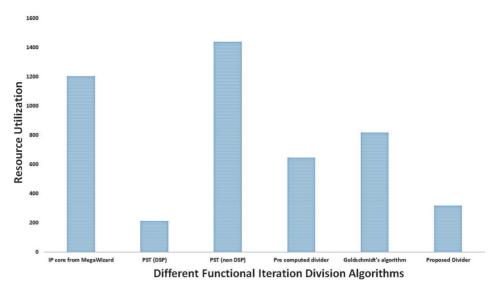

| Figure 21. Comparative analysis of the proposed novel USP-Awadhoot divider       | with   |

| different functional dividers                                                    | 71     |

#### **List of tables**

| Table 1. Publications containing the thesis' contributions                 | 18         |

|----------------------------------------------------------------------------|------------|

| Table 2. Summary of a comparative study of different dividers              | 25         |

| Table 3. Hexadecimal representation of addition                            | 39         |

| Table 4. Comparative analysis of the proposed USP-Awadhoot divider and     | the Xilinx |

| LogiCORE IP integer divider generator V4.0 (8-bit)                         | 72         |

| Table 5. Comparative analysis of the proposed USP-Awadhoot divider and     | the Xilinx |

| LogiCORE IP integer divider generator V4.0 (32-bit)                        | 72         |

| Table 6. Summary of the comparison between standalone divider implemental  | tions year |

| – 2019 [5]                                                                 | 74         |

| Table 7. Summary of the Taiga soft processor divider implementation compar | rison year |

| <b>–</b> 2019 [5]                                                          | 74         |

#### 1 Introduction

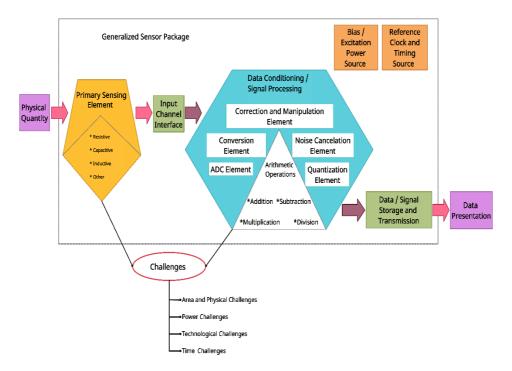

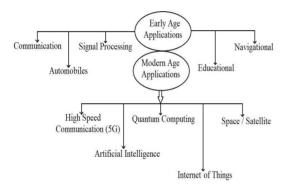

Enhancement in the semiconductor industry enables the development of new areas of work and studies in the fields of signal processing, statistical data analysis, computational processing, image processing, artificial intelligence, high-performance graphics rendering systems (such as graphic processing units (GPU)), complex systems on chips, central processing units, biomedical equipment, fuzzy control, and space engineering [1-14]. Signal and image processing environments utilize theoretical and applied mathematics for algorithms and hardware that transform preliminary signals from natural and artificial sources into constructive data, which is valuable for application-specific purposes. Figure 1 illustrates the generalized block view of a sensor package. The sensor package comprises a primary sensing element, input channel interface, data conditioning/signal processing, signal/data transmission, storage, reference clock, and power subsystem. The primary sensing element converts a physical quantity into an electrical signal, generating the required information/data component and noise. It requires further signal processing and noise cancellation to improve the quality of sensor signals and extract the relevant properties (such as amplitude, frequency or spectral content, phase, or timing information) from the varying electrical signals [14].

Figure 1. Basic block diagram of the sensor package.

Analog filters have several significant disadvantages that affect filter performance, such as component aging, temperature drift, and component tolerance, with a significant drawback in the inflexibility of the system response. On the contrary, digital signal processing (DSP) is adaptive and flexible, with a high tolerance for component aging and temperature drift. To achieve good results, the DSP system must implement all

mathematical operators in a thoroughly optimized way [1]. The evaluation of addition and multiplication implementations typically falls into the latency range of 1 to 10 clock cycles. The performance evaluation of division operation implementation typically falls into the latency range of 10 to 100 clock cycles [15-19], which is also referred to as 'execution time'. When executing division on *n*-bit operands, recursive subtraction is required for *n* iterations to get the *n*-bit quotient.

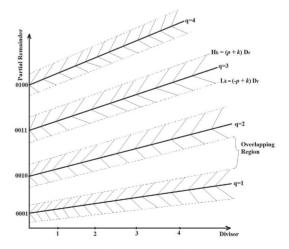

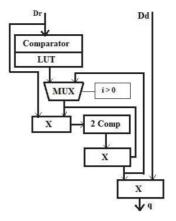

The division operation can be replaced by several methods using iterative approaches, such as sequential subtraction (numerical iteration applications) and multiplication (functional iteration applications). Execution time and implementation area are the two basic parameters of comparison. Existing Dividers can be classified into subtractive iteration or functional iteration dividers. Digit recurrence dividers were the first to use successive subtractions, beginning with the least significant bit to calculate the required quotient. For n-bit operands, the division requires n recursive subtraction iterations to produce the n-bit quotient. Digit recurrence dividers are easy to implement for larger bit size operands, due to subtractive iterations, but require extensive conversion time, chip implementation area, and a critical selection logic and overlapping region for quotient bit selection. The SRT (Sweeney-Robertson-Tocher) divider, named after the researchers, is one of the most implemented non-restoring digit recurrence type dividers. SRT divider, also known as the radix-n divider. The radix number (n) determines how many quotient bits are calculated in a single iteration. In SRT dividers, the radix size is typically kept small because increasing the radix not only increases the number of quotient bits generated per iteration but also significantly complicates the quotient bit selection logic. This complexity arises from the need to handle a larger set of quotient values and manage overlapping regions [15, 20-21]. High-radix division algorithms are implemented with different architectures (e.g., the array structure or cascading architecture) but require a comparatively higher chip implementation area [15]. Overflow, due to overcompensation, causes the selection of a quotient digit out of the range [22-25] and is one of the possible drawbacks of the Svoboda and Svoboda-Tung algorithm-based radix-n divider, that only requires a few Most Significant Bits (MSBs) of the partial remainder for the quotient selection logic.

Functional iterations compute the quotient bit based on the estimation or approximation of series expansion functions, such as the Newton-Rapson [26-27], Goldschmidt [11, 28-31], and Taylor series [11, 32-35]. These require the selection of a reciprocal value at the initial iteration of the conversion. It makes the quotient bit selection logic critical and complex. Nevertheless, the precision of the outcome and the possibility of error are contingent on the proximity of the initial reciprocal selection and rounding off the approximate solution values, rather than infinitely precise ones. The error depends on the accuracy of the initial estimation. Reducing the error requires introducing a trade-off between the additional chip area for the look-up table and the latency of the divider. The Goldschmidt algorithm is a second functional iterative divider that is only effective for floating-point division because it does not provide the remainder [31]. Taylor series expansion calculates an accurate anti-divisor (reciprocal) to reduce the error in the least significant bits of quotient precision with a parallel powering section, causing extra hardware overhead. The upcoming application areas of high-speed computation, embedded systems, artificial intelligence [3, 7-8, 36-37], complex SOC [9], vision systems [1, 5-6, 36-37], automotive control [9], telecommunications [36-37], the internet of things (IoT), cryptography [4, 36-37], and many others, offer the possibility and requirement of further improvements in division implementation.

However, a research gap exists for simultaneously utilizing multiple performance improvement techniques with individual input operands. This provides the possibility of developing a new technique or combination of a fast or moderate, less complex quotient selection logic and methods to reduce the chip implementation area. Reducing the implementation area of the divider block can enhance the overall resource utilization of the larger system in which it is integrated.

The work presented in this thesis contributes to the significant challenges of quotient selection logic criticality, the chip implementation area reduction of hardware, and circuit implementation for the divider, by proposing a novel division algorithm. The ultimate target of the research is to provide simple quotient selection logic, with dynamic separate scaling operations for the dividend and divisor, to reduce the possibility of devastating and costly problems (causing system failure) and reducing the implementation area for digit recurrence divider implementation. The proposed novel divider implementation includes a detailed step-by-step conceptualization, outlining the implementation requirements, and provides resource utilization statistics for further study and implementation with various applications.

#### 1.1 The scope and the organization of the thesis

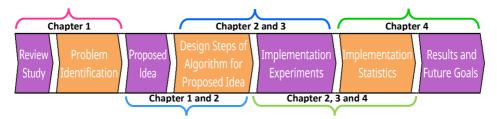

Figure 2. The scope and the organization of the thesis.

Figure 2 illustrates the progression of the concept of a new divider toward a physical implementation and evaluation through its various phases. The scope of the overall thesis is focused on the research required to provide simple quotient selection logic in order to reduce the possibility of devastating and costly problems, which could cause operation failure and reduce the implementation area for digit recurrence divider implementation.

Chapter 1 presents a detailed study of the major concepts, methods, techniques, and algorithms regarding divider implementation, including the working idea, requirements, and implementation statistics. This chapter provides a comprehensive overview of division operation and explains various ways of classifying division operation implementation with detailed information on specifications, advantages, and disadvantages.

Chapter 2 describes the definition and conceptualization of the proposed novel USP-Awadhoot divider implementation.

Chapter 3 presents a detailed description of the application of the novel USP-Awadhoot divider for complex number division using the Baudhayan-Pythagorean triplet algorithm.

Chapter 4 presents a detailed comparative analysis study of the implementation statistics for resource utilization of the proposed novel USP-Awadhoot divider. Waveform analysis explains the idle working state of each signal in the novel USP-Awadhoot divider.

It also describes the road map for future research activities to refine the implementation along with different applications.

Appendix 1 to Appendix 7 present publication details, examples of the proposed novel USP-Awadhoot divider, and functional waveforms.

#### 1.2 Problem statement and research objectives

Division is a derived operation, similar to multiplication. The division operation can be replaced by several methods using iterative approaches, such as sequential subtraction (numerical iteration applications) and multiplication (functional iteration applications). Multiplicative or functional iterative algorithms are faster than subtractive algorithms but require a larger area on a chip for implementation; whereas, subtractive algorithms require less area but have longer execution time. The overlapping region refers to a range of partial remainder values, where the selection of the next partial quotient is ambiguous due to the step size of a radix-n divider. It could cause a problem in selecting the true quotient value. Research and implementation have been carried out for alternative approaches to design a quotient selection logic, which requires only a few MSBs of the partial remainder. Because of this, the final remainder value cannot be calculated at the end of the division. Thus, such a divider is limited to the applications that do not require remainder data.

Many researchers have worked on various performance improvement techniques, such as pre-scaling operands, carry-save remainders, array implementations, truncations, cascading, and differential LUTs. However, these performance improvement techniques have yet to be fully explored to address the research gap of utilizing multiple performance improvement techniques simultaneously with individual input operands. This approach could potentially lead to the development of a new technique or a combination of fast or moderate methods to optimize conversion time and implementation area. Thus, the main objective of the present research is to provide a combination of multiple techniques that can be simultaneously utilized on the individual input operands to achieve an area-efficient solution for divider circuit implementation. This Ph.D. research focuses on the following research objectives (RO).

- RO1 Investigate the currently existing divider solutions to understand the different concepts of conversion logic, conceptualize the trade-off between area, speed, and power, and propose a suitable option or combination of options to develop an efficient divider.

- RO2 Develop the theory of conversion logic to implement dynamic separate scaling operations for input operands. Here, a separate scaling operation means simultaneously using different scaling operations for input operands. A partitioning operation is used for the dividend. An operation composed of "Veshtanam Sutra (by osculation) and Lopanasthabhyam sutra (by elimination and retention)" is used for the divisor. 'Dynamic' refers to the different values of "Flag Digit (FD) and Number of Zeros Cancelled (NZC)", used in Veshtanam Sutra (by osculation) and Lopanasthabhyam sutra (by elimination and retention), depending on the combination of input operands.

- RO3 Divider algorithm formulation to reduce the criticality of conversion logic by eliminating overlapping regions in quotient selection.

- RO4 Implement the divider based on the formulated algorithm, and improve the area requirements to compose the operand-dependent divider circuit design.

#### 1.3 Thesis contribution

The main objective of this doctoral dissertation is to explore the research gap in the simultaneous use of multiple performance enhancement techniques with individual input operands, aiming to design and implement a divider circuit block with reduced area. It also intends to provide a solution, based on the divisor and the dividend relationship, that improves the quotient bit calculation logic and avoids rounding-off errors. As stated before, this Ph.D. research work relate to the derivation of a new algorithm for reduced area implementation of the divider circuit block. The design is developed by simulating the proposed approach and cross-verifying it by performing regular sequential and pseudo-random performance analyses against standard result tables generated by simulations and the theoretical study of the proposed idea. Table 1 summarizes the thesis contributions, in relation to the research papers. The novelty and main contributions of the Ph.D. thesis are as follows:

- In association with RO1, RO2, RO3, and RO4, this thesis contributes to the

development of a novel algorithm for implementing a divider circuit block.

The innovative concept of dynamic separate scaling operations for the dividend and

divisor reduces resource requirements, resulting in a divider circuit block with a low

area footprint.

- In association with RO2, RO3, and RO4, I developed an easy Group Quotient  $(GQ_n)$  value selection logic in the proposed divider circuit block based on the unique relation derived between Dividend Groups  $(GD_d)$ , Modified Divisor  $(MD_r)$ , and Flag Digit (FD) without any critical overlapping.

- In association with RO2, RO3, and RO4, I developed a clear process for selecting the final quotient based on the Group Quotient  $(GQ_n)$ , Partial Quotient  $(PQ_n)$ , and Additional Quotient (AQ) values without critical overlapping regions.

- In association with RO2 and RO3, I implemented a complex divider based on the Baudhayan-Pythagorean triplet algorithm with the proposed USP-Awadhoot divider circuit block.

- The described steps reduce the criticality of the conversion logic by eliminating overlapping regions in the quotient bit selection logic.

Table 1. Publications containing the thesis' contributions.

| Contributions          | Publication<br>I | Publication<br>II | Publication<br>III | Publication<br>IV |

|------------------------|------------------|-------------------|--------------------|-------------------|

| RO1- Review            | ✓                | ✓                 |                    | ✓                 |

| RO2- Develop dynamic   |                  |                   |                    |                   |

| separate scaling       |                  | ✓                 | ✓                  | ✓                 |

| operations             |                  |                   |                    |                   |

| RO3- Divider Algorithm |                  |                   | ,                  | ,                 |

| formulation            |                  |                   | •                  | •                 |

| RO4- Divider           |                  |                   |                    |                   |

| Implementation and     |                  | ✓                 | ✓                  | ✓                 |

| Improvements           |                  |                   |                    |                   |

#### 2 Division circuit block – overview of division algorithms

This chapter is based on publications I, II, and IV. In the past, limited communication and transportation made it difficult to establish uniform mathematical standards worldwide. Hindu-Arabic numerals, which comprise the ten symbols -1, 2, 3, 4, 5, 6, 7, 8, 9, and 0, are based on India's decimal number system. They were mentioned in Aryabhata's 'Aryabhatiya' and Brahmagupta's 'Brahmasphuta Siddhanta' in the  $6^{th}$  and  $7^{th}$  centuries, and, according to al-Qifti, they were introduced to the Arab world in the late  $7^{th}$  century. Later, in the  $12^{th}$  century, these were transmitted to Europe via the chronologies of the scholars, particularly al-Khwarizmi, al-Kindi, and the Italian mathematician Leonardo Pisano (also known as Fibonacci) [38-41].

Although new concepts, operations, logic, and relations have been developed in mathematics, 'addition', 'subtraction', 'multiplication', and 'division' are still the firm foundations of applied mathematics [1, 10]. Due to the commutative and associative properties of addition and multiplication, operands can be rearranged flexibly without affecting the result [42-43]. The division operation is a derived operation in the same way that multiplication is also but, instead of successive addition, it is derived by successive subtraction, along with some controlling conditions. Similar to subtraction, division also lacks commutative and associative properties, making its implementation in electronic circuitry critical and challenging. Thus, it is essential to understand the importance of the critical parameter requirements and problems associated with the implementation of a division circuit block.

#### 2.1 Importance of division circuit blocks

A Field Programmable Gate Array (FPGA) is an advanced technological feature. It provides hardware re-programmability, which reduces implementation time and hardware costs. It gives the flexibility to implement a system on a chip for different purposes. The Arithmetic and Logical Modules (ALMs) of FPGAs are essential building blocks for implementing desired logic [44]. FPGA applications are more critical for automotive control, online data processing, and a wide range of computational tasks, which could be solved by implementing a small, complex system (such as a computer system) on a single chip. In general-purpose applications, central processing units (CPU/processor) perform division with several iterations, even for a few bits. This problem becomes critical, along with an increasing bit count [10]. Such issues are even more severe in the graphics processing unit (GPU) and Intel's many integrated core (MIC) architecture, which provides parallel architecture [45]. The CPU's working frequency has increased to 3 GHz over time; however, this has also led to higher power dissipation [12].

Complex division used in various applications in essential engineering works, such as earth fault distance protection, acoustic pulse reflectometry, astronomy, non-linear radio frequency measurements [46,53], and control theory applications (e.g. investigating root locus, Nyquist plot, Nichol's plot, and microwave system frequency response) [47]. It is also required in digital signal processing and numerical computation applications, such as Vertical Bell Laboratories layered space-time detection (V-Blast), orthogonal frequency division multiplexing, and channel equalization of the MIMO system [48]. Earlier, the lack of a dedicated divider (due to its low usage and high chip area requirements) resulted in an emphasis on division operations performed by software [6, 18, 49-51]. Designers also have to consider the implementation technology for the

algorithm as it is directly related to the area and time concerns of divider circuit implementation [51-52].

As per the studies presented in [15-19] and [51-52], the typical latency for addition and multiplication ranges from 2 to 8 clock cycles. In contrast, division latency ranges from 8 to 80 clock cycles [53]. The division could be performed using adders and multipliers, instead of creating separate hardware for the divider. Such an arrangement to perform a division operation comes with a significant risk of extended overhead and possible error in the final result due to rounding off. The algorithms and architectures studied in [52, 54] show that the focus was placed on improving adders and multipliers rather than developing a dedicated divider circuit. However, solely prioritizing these improvements can lead to undesirable behavior, including numerical vulnerabilities and a higher risk of overflow. [51, 52, 54].

Even if it were possible to build a multiplier to compute in a single cycle, finding a matching adder would be difficult. Fast-operating multipliers, such as array multipliers, can have low cycles to execute at the cost of significant area overhead, which would not be a cost-effective area solution for implementing division operation [51, 52]. This indicates that the area distribution among the adder, multiplier, and divider circuits should be proportionally balanced to have an efficient and optimized system. As per the study presented in [51, 52], iterative algorithms are preferred over pure combinational algorithms, for implementing division circuit blocks to achieve a low area footprint system. The study also suggested that neglecting improvements in division operation implementation is a key factor contributing to performance loss in embedded systems, digital systems, digital circuits, computer systems, and integrated circuits. Thus, it is necessary to focus on low-area footprint divider circuit implementation, as the implementation area introduces critical delays and timing issues in its standard execution. Also, the increase in the application demand and development of new application areas encourage the development of area-efficient divider circuit blocks.

#### 2.2 Division circuit block taxonomy

A study conducted by [55] demonstrated that the installation of division circuit blocks influences the performance of a complicated system. In addition, even the slightest change, such as a 1% improvement in the performance of the division circuit block, might affect the system's performance by up to 20%. Division operations were performed based on sequential, linear operations and digital circuitry in the applications with low computation requirements, to express logic functions with high accuracy on account of the large area and latency [56-58]. Implementation area, computation time, and power consumption are the three main topics of interest from a system implementation point of view. The applications developed at this stage required area reduction for the division because their current implementations lack area and latency efficiency [59-61]. Area efficiency refers to the percentage of the available hardware resources utilized to implement the divider. An algorithm can be specified as a computer program or a hardware circuit design with specifications that describe the computational procedure to be followed during implementation [62]. Thus, many methods or algorithms have been researched, designed, and implemented over time, with the common goal of an efficient divider circuit implementation for an efficient system.

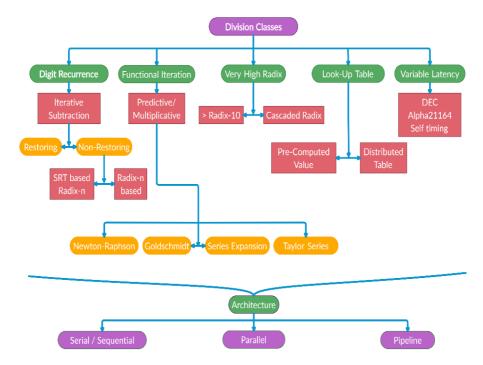

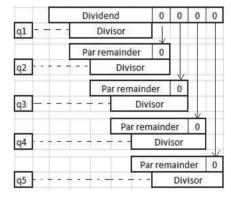

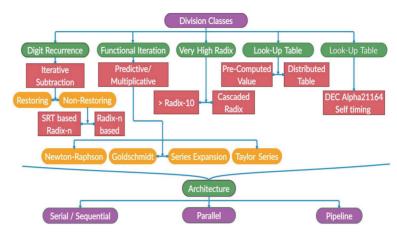

Figure 3. Division algorithm taxonomy.

In the studies described in [7, 15, 31, 63-65, 71-73], numerous mathematical algorithms were devised and analyzed over several decades. Many algorithms are difficult to distinguish precisely, but they may be divided into two categories: digit recursion and functional iteration [65]. Still, depending on the quotient conversion logic, they can be broadly summarised into multiple divider classes. The study presented in [15] showed that division algorithms can be categorized into five distinctive classes. The hierarchical distribution of various classes of division algorithms is expressed as division algorithm taxonomy in Figure 3 and described based on the four factors representing conversion logic, hardware architecture, performance, and execution type [6, 15, 66-67]. There are five broad categories of division algorithms: digit recurrence, functional iteration, very high radix, look-up table, and variable latency. Based on the hardware architecture and access techniques, they can be further classified as serial, sequential, parallel, pipeline, slow, fast, iterative, and predictive.

#### 2.2.1 Digit recurrence class (DRC)

The digit recurrence class (DRC) of the division algorithm is the earliest and most pioneering class among all division algorithms [15, 20]. The quotient is calculated using a series of successive subtraction operations, beginning with the least significant bit [1-3, 15, 20, 66-70]. The digit recurrence class of algorithm-based dividers is categorized into two types of dividers, commonly known as 'restoring' and 'non-restoring' algorithm-based dividers.

Many processors such as Intel Pentium, HP PA 8000, and Sun UltraSPARC [70] initially implemented a restoring type DRC algorithm-based long division divider concept. Thus, the remainder and quotient values remain either positive or zero [1, 3, 20, 61, 68, 71-73]. The SRT algorithm is one of the most popular non-restoring digit recurrence

division algorithms to implement. Furthermore, many attempts [74-105] have been orchestrated to develop, investigate, and discuss the original concept of the SRT algorithm, in order to improve it. The trade-off between the components of the choices to be made is mainly the radix, quotient, and partial remainder representation [15, 50, 97-98], resulting in diverse application selections ranging from less critical to crucial, which impacts time-cost requirements. A rise in radix value increases the size of the quotient selection logic table, beyond the practical limits of the implementation. It is evident that Intel has lost millions of dollars due to the Pentium processor's flaw in the overlapping region of the floating-point divider [92, 104]. In 1963, Svoboda devised another digit recurrence division algorithm based on the partial remainder alone. It considers quotient digit selection logic based on the remainder's MSBs [8, 22-25, 119-122]. Tung [22-24, 119, 121] investigated the potential of implementing the Svoboda algorithm using a signed digit number system.

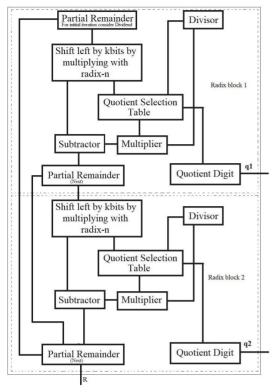

#### 2.2.2 Very high radix digit recurrence class (VHRDRC)

Unlike SRT and other radix-n divides, these very high radix algorithms have different hardware and circuitry for quotient selection and partial remainder generation. The high radix algorithm proposed by Wong and Flynn [123] requires at least one look-up table, comprising  $(2^{(m-1)} \times m)$  bits. The high radix algorithm proposed by Lang and Nannarelli [124] shows the construction of a radix- $2^k$  divider to implement a radix-10 divider whose quotient digit is partitioned into two sections, one in radix-5 and the other in radix-2.

The Cyrix 83D87 arithmetic co-processor utilizes a short reciprocal algorithm similar to the accurate quotient approximation method, to obtain a radix- $2^{17}$  divider [15]. The possible methods, which are applicable to high radix dividers, include the use of: different look-up tables for quotient digit selection logic [23, 93, 125], pre-scaling operands [126-131], Fourier division [132-133], alternative digit codes (like BCD digits instead of decimal and basic binary digits [105]), cascading multiple stages of lower radix dividers [45], overlapping two or more phases of low radix [85, 94], a truncated schema of exact cell binary shifted adder array [100, 134-135], on-line serial and pipelined operand division [136], the parallel implementation of low radix dividers [137], and array implementation [4].

#### 2.2.3 Look-up table class (LTC)

Look-up tables can hold the pre-computed values, standard values and exact values of the approximation of the reciprocal for the quotient bit finalizing technique. The latest development described in [138] pertains to the bipartite reciprocal table, which can be utilized for reciprocal approximation in dividers. It uses two separate look-up tables for positive and negative values. The look-up table class is a hybrid class of dividers, as look-up tables are used to improve dividers from different classes.

#### 2.2.4 Functional iteration class (FIC)

This division method uses successive multiplications instead of subtractions. It is possible to get multiple quotient digits in a single iteration but at the cost of accuracy, due to the rounding off of solution values and implementation area [139]. The Newton-Raphson method is used in IBM 360/91 and Astronautics ZS-1 [26-27]. Taylor Series Expansion is used in IBM RS/6000 and AMD K7 processors [33, 35]. Later, J. Liu et al. [33] presented a hybrid algorithm that combined prescaling, series expansion, and Taylor series expansion for the implementation of a divider.

#### 2.2.5 Variable latency class (VLC)

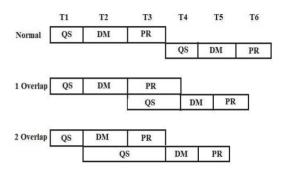

The DEC Alpha 21164 is one of the best examples of a variable latency class algorithm implementation based on the basic normalizing non-restoring division algorithm [15, 50, 145]. Sometimes, multiple stages are cascaded together with a self-timing partial remainder in the self-timing technique [118, 146]. The Hal SPARC V9 processor and Sparc64 are examples of practical implementations of the variable latency self-timing division algorithm [15, 50]. Richardson [147] described a mechanism for caching results that can be used with the divider to accelerate calculations in applications involving repeating operands. In [89], Cortadella mentioned implementing the SRT divider with variable latency, detecting a variable number of quotient bits at each iteration.

#### 2.3 Hardware architectures

The three primary classifications of hardware architecture are: sequential or serial, parallel or concurrent, and pipelined or hybrid. The serial hardware architecture consists of the sequential implementation and processing of the components required for algorithm implementation and is primarily used for general purposes. Subtractive iteration-based digit recurrence division algorithms are the best examples of serial dividers [20, 36, 136, 148]. The parallel hardware architecture consists of multiple hardware units implemented and processed concurrently to get the desired result with fewer iterations. This approach is mainly used for graphical processing units (GPUs) and in Intel's many integrated core (MIC) processors [6, 10, 13, 149-150]. A parallel divider, based on the Jebelean exact division algorithm [149-151], is another example of a parallel hardware architecture class divider. The third approach provides parallel processing by executing the instruction level overlapping of a computational approach [4, 9, 20, 91, 136]. This architecture allows the simultaneous performance of several instructions of the computation process to achieve some degree of parallelism. Pipeline work structure can be achieved by designing a computational logic that provides functional overlap in the execution stage and arranging pipelined hardware, like a fully pipelined array structure [4, 9].

#### 2.4 Performance improvement techniques

Performance-improvement techniques, like simple staging, overlapping/pipelined execution, overlapping quotient selection, overlapping partial remainder computation, range reduction, operand scaling, and circuit family effects are significant in divider implementation. HP PA-7100 [15, 106] and AMD 29050 [15, 107] microprocessors are examples of two radix-4, clocking faster than the system clock to perform radix-16 work in every machine cycle [15, 108]. The AMD 29050 microprocessor also exhibited the same logic of achieving higher radix. The study presented in [85, 109] showed that many circuit-level implementations of the SRT algorithm yield different performances, depending on the choice of circuit family. In the overlapping/pipelined execution, the partial remainder-dependent pipelined form of execution is performed when a redundant format represents the partial remainder. In contrast, the quotient selection execution-dependent pipeline is suitable when a non-redundant format represents the partial remainder [110].

The technique of reducing the divisor by a fixed factor, to bring it as close as possible to one, is known as 'divisor pre-scaling' [15, 111]. The basic concept of the pre-scaling divisor and dividend, by common pre-scaling factor, is explained in [112-113]. A similar concept was explained in [102] and it was suggested that the user uses six digits of the

redundant partial remainder to generate quotient bit selection logic in implementing the Radix-4 divider. Performance improvement techniques can also be considered for other classes of division algorithms depending on the particular requirements of individual algorithm class-based dividers [83, 102, 109-118]. However, no single performance improvement technique can concurrently address all performance factors, and one has to decide what type of option to select based on the particular application.

#### 2.5 Summary of comparative analysis

An efficient divider is required for an effective and efficient computation system. Table 2 summarizes a comparative study of the different division algorithm-based dividers. The initial distribution gives digit recurrence, functional iteration, very high radix, a look-up table, variable latency, serial/sequential, parallel, and pipelined classes of a divider [6, 15, 23, 50, 68]. Digit recurrence is the most trusted, implemented, researched, and commercially used division class amongst all divider implementation classes. The restoring, and some non-restoring, algorithms implement simple conversion logic but require a long time and a large area. Functional iterative class dividers compute the quotient bits by estimating or approximating series expansion functions such as, Newton-Rapson [26-27], Goldschmidt [11, 28-31], and Taylor series [11, 33-35], where an approximated reciprocal multiplies the dividend to converge toward the required quotient. They use multiplication instead of subtraction, which decreases the number of iterations and provides several quotient digits with minimal latency in a single iteration.

However, multipliers require a larger footprint than adders or subtractors. Multiplication makes functional iteration dividers more complicated than basic digit recurrence dividers. This divider has the significant drawback of the quotient bit's inaccuracy because of direct rounding off of the approximate solution values, rather than infinitely precise ones. In the Newton-Raphson iteration, which is limited to two multiplications and must proceed in series, a significant error is generated. The generated error depends on the accuracy of the initial estimation. Reducing the error requires introducing a trade-off between the additional chip area for the look-up table and the latency of the divider.

Unlike the Newton-Rapson method, which only multiplies the dividend, the Goldschmidt algorithm multiplies the dividend and the divisor by the anti-divisor. It is only useful for floating-point division because it does not offer the remainder [31]. Another drawback is that 1's complement can avoid carry propagation delay but it adds a new approximation error in each iteration. In Taylor series dividers, series expansion computes an accurate anti-divisor (reciprocal) to reduce the error in the least significant bits of quotient precision, with a parallel powering section that calculates high-order terms, increasing the hardware overhead. Variable latency class [89, 124, 145, 147] dividers are uncommon due to their complexity and large area. High radix [124] reduces the latency but requires a large capacity look-up table, which is impractical for implementation. The look-up table class [67, 138] involves storage like ROM, which increases the area requirements for implementation. Dividers can be implemented using one of three distinct hardware architectures.

The serial hardware architecture [20, 36, 136, 148] necessitates increased latency and conversion time, making it unsuitable for mission-critical applications. In contrast to serial architecture, parallel hardware architecture [6, 10, 13, 149-150] requires the concurrent operation of multiple cores, precise synchronization, and a significant implementation area, resulting in a higher implementation cost.

Table 2. Summary of a comparative study of different dividers.

| Sr. | Algorithm            | Equations                                                    | Important Points                                                                |

|-----|----------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------|

| No. |                      |                                                              |                                                                                 |

| 1   | Restoring            | For J <sup>th</sup> iteration                                | It is similar to the long-division algorithm.                                   |

|     | Divider              | $q_j = 0$ if $R'_j < 0$                                      | Simple logic for implementation.                                                |

|     | [1-3, 15, 20,        |                                                              | No requirement for a look-up table.                                             |

|     | 61, 66-73].          | $q_j = 1$ if $R'_j \ge 0$                                    | Iterative subtraction is performed.                                             |

|     |                      | $R_j = 2R_{j-1}  \text{if } q_j = 0$                         | The non-redundant number system is used                                         |

|     |                      | $K_j = 2K_{j-1}  \text{if } q_j = 0$                         | to write a quotient.                                                            |

|     |                      | $R_i = R'_i \text{ if } q_i = 1$                             | If the partial remainder value not positive or                                  |

|     |                      |                                                              | zero, then the divisor is restored by the                                       |

|     |                      | $R'_j = 2R_{j-1} - D_r$                                      | subtraction result performed in that                                            |

|     |                      |                                                              | iteration.                                                                      |

|     |                      |                                                              | It requires a full-width comparator in each                                     |

|     |                      |                                                              | iteration, and the subtractor, shift register,                                  |

|     |                      |                                                              | and multiplier give the approximate area                                        |

|     |                      |                                                              | requirement for algorithm implementation.                                       |

|     |                      |                                                              | Possible loss of most significant bit (MSB)                                     |

|     |                      |                                                              | and checks for overflow are required.                                           |

|     |                      |                                                              | Requires full-width comparison in every                                         |

|     |                      |                                                              | iteration to get one bit of quotient.                                           |

|     |                      |                                                              | The quotient needed to be rearranged to                                         |

|     | Non                  | For ith transition                                           | get the actual quotient.                                                        |

| 2   | Non-                 | For $J^{th}$ iteration $q_j = -1  \text{if} \ \ R_{j-1} < 0$ | Like the restoring algorithm, it does not                                       |

|     | Restoring<br>Divider | qj 1 11 N <sub>J</sub> -1 0                                  | require the restoring of the partial remainder if subtraction becomes negative. |

|     | [1-3, 15, 20,        | $q_j = 1  \text{if}  R_{j-1} \ge 0$                          | No requirement for a look-up table.                                             |

|     | 61, 66-73,           |                                                              | Based on the previous iteration sign value of                                   |

|     | 174].                | $R_j = 2R_{j-1} + D_r \text{ if } q_j = -1$                  | the partial remainder, only one addition or                                     |

|     |                      | $R_{i} = 2R_{i-1} - D_{r} \text{ if } q_{i} = +1$            | subtraction can be performed in each                                            |

|     |                      | $K_j - 2K_{j-1} - D_r \Pi q_j - +1$                          | iteration.                                                                      |

|     |                      |                                                              | Partial remainder kept between -Dr to +Dr                                       |

|     |                      |                                                              | and quotient digit is -1 or 1.                                                  |

|     |                      |                                                              | It requires a sign bit to decide whether to                                     |

|     |                      |                                                              | perform addition or subtraction; the adder,                                     |

|     |                      |                                                              | subtractor, and shift register give the                                         |

|     |                      |                                                              | approximate area requirement for                                                |

|     |                      |                                                              | algorithm implementation.                                                       |

|     |                      |                                                              | Requires an extra bit to be added with the                                      |

|     |                      |                                                              | partial remainder, to have a track on a sign.                                   |

|     |                      |                                                              | It requires a separate adder and subtractor                                     |

|     |                      |                                                              | in each iteration.                                                              |

|     |                      |                                                              | Area utilization of implementation is                                           |

|     |                      |                                                              | approximately equal to the area required to                                     |

|     |                      |                                                              | implement an adder, subtractor, and shift                                       |

|     | 1                    |                                                              | register.                                                                       |

| 2 | CDT         | For J <sup>th</sup> iteration                                    | It is a non-rostoring algorithm based on             |

|---|-------------|------------------------------------------------------------------|------------------------------------------------------|

| 3 | SRT         | For J <sup>**</sup> Iteration                                    | It is a non-restoring algorithm based on             |

|   | Divider     | <del>-</del>                                                     | radix-n.                                             |

|   | [15, 50, 66 | $q_j = \overline{1}  if  2R_{j-1} < -D_r$                        | Named after Dura W. Sweeney [74], James              |

|   | 74-105]     | 0 16 0 100 10                                                    | E. Robertson [75], and Keith D. Tocher [7].          |

|   |             | $q_j = 0  if  -D_r \le 2R_{j-1} \le D_r$                         | For x bits, integer division requires $k=x/b$        |

|   |             |                                                                  | iterations, b is the number of bits detected         |

|   |             | $q_j = 1  if  2R_{j-1} \ge D_r$                                  | in each iteration.                                   |

|   |             |                                                                  |                                                      |

|   |             | Has one of the values -m, -m+11,                                 | n decides how many quotient bits are                 |

|   |             | 0, +1 m-1, m, where m is an                                      | detected in each iteration; if <i>n</i> =2, then one |

|   |             | integer comprising k digits of radix-                            | quotient bit is detected per iteration. Radix–       |

|   |             | n as                                                             | n is typically selected as a power of base 2.        |

|   |             | $\frac{1}{2}(n-1) \leq m \leq n-1$                               | Each quotient digit has a value from {-m, -          |

|   |             | $\frac{1}{2}(n-1) \le m \le n-1$ $n = 2^b  and  k = \frac{x}{b}$ | m+1,, -1, 0, 1,, m-1, m}.                            |

|   |             | n=2 and $k=/b$                                                   | The algorithm implements 2's complement              |

|   |             | $Q = \sum_{i=1}^k q_i  n^{-i}$                                   |                                                      |

|   |             | $Q = \sum_{i=1}^{q} q_i n$                                       | value of $D_r$ instead of $D_r$ , which provides     |

|   |             | Quotient $q$ is generated as a                                   | shifting over zeros to eliminate extra adders        |

|   |             | dividend division by a divisor of $x$                            | and subtractors.                                     |

|   |             | •                                                                | It needs an extra subtractor to find out the         |

|   |             | most significant bits retiring b bits                            | next partial remainder.                              |

|   |             | of the quotient in each iteration. It                            | Error results due to few MSBs being used to          |

|   |             | is called a 'radix-n performing k                                | predict quotient bits as in low radix, which         |

|   |             | iterations' to get the desired                                   | decreases with the increase of radix.                |

|   |             | quotient.                                                        | Quotient select table plus carry-save adder          |

|   |             |                                                                  | · · · ·                                              |

|   |             |                                                                  | (CSA) gives the approximate area                     |

|   |             |                                                                  | requirement for algorithm implementation.            |

|   |             |                                                                  | It shows the iteration time of accessing the         |

|   |             |                                                                  | select quotient table plus multiple forms and        |

|   |             |                                                                  | subtraction. It requires a quotient selection        |

|   |             |                                                                  | look-up table.                                       |

|   |             |                                                                  | Selecting higher quotient bits causes                |

|   |             |                                                                  | complexity in quotient selection logic, and          |

|   |             |                                                                  | higher radix implementation is complex due           |

|   |             |                                                                  | to impractical multiples of the divisor.             |

|   |             |                                                                  |                                                      |

|   |             |                                                                  | It needs to convert the last remainder to            |

|   |             |                                                                  | conventional representation to find the sign         |

|   |             |                                                                  | bit, and the quotient correction stage               |

|   |             |                                                                  | selection depends on the sign bit.                   |

| 4 | Very high   | *****                                                            | It retires more than ten quotient bits in one        |

|   | radix       |                                                                  | iteration and requires a large look-up table         |

|   | [4, 15, 23, |                                                                  | with a bigger capacity for quotient selection        |

|   | 85, 93-94,  |                                                                  | logic. A lookup table is required for obtaining      |

|   | 100,        |                                                                  | an initial approximation to reciprocal and           |

|   | 123-137]    |                                                                  | quotient digit selection logic.                      |

|   | 123-13/]    |                                                                  |                                                      |

|   |             |                                                                  | It uses multiplication to form divisor               |

|   |             |                                                                  | multiples.                                           |

|   |             |                                                                  | It differs from the regular radix-n divider          |

|   |             |                                                                  | regarding the number and type of                     |

|   |             |                                                                  | operations used in each iteration and                |

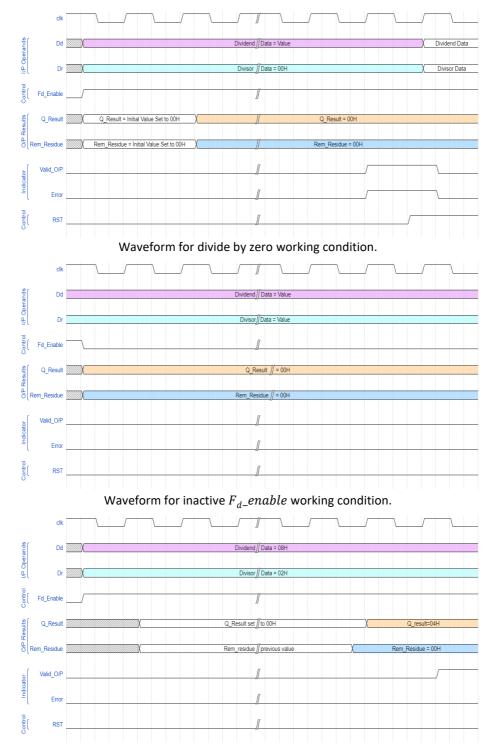

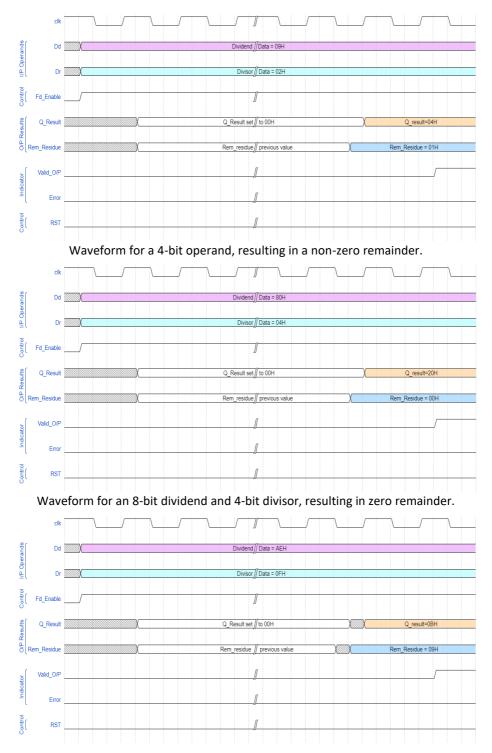

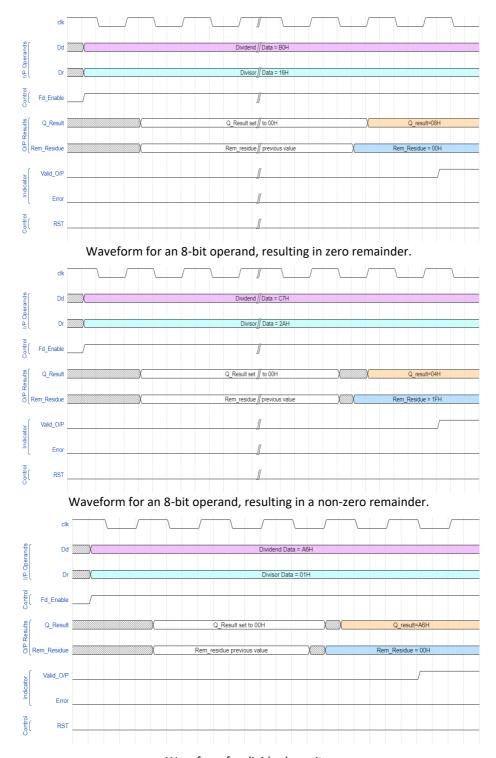

|   |             |                                                                  | quotient digit selection logic.                      |