# DEPARTMENT OF ELECTRICAL POWER ENGINEERING AND MECHATRONICS

# PRODUCT QUALITY IMPROVEMENT THROUGH TESTING PROCEDURES

# TESTIMISPROTSEDUURIDE ABIL TOOTEKVALITEEDI PARANDAMINE

# MASTER THESIS

| Student:<br>Student code: | Monika<br>194534MAHM                                      |

|---------------------------|-----------------------------------------------------------|

| Supervisor:               | Even Sekhri, Tallinn University of<br>Technology          |

| Consultant:               | Salvador Gonzalez Perez, Manager of<br>Test Data Analysis |

(On the reverse side of title page)

#### **AUTHOR'S DECLARATION**

Hereby I declare, that I have written this thesis independently.

No academic degree has been applied for based on this material. All works, major viewpoints and data of the other authors used in this thesis have been referenced.

"21" December, 2022

Author: Monika /signature /

Thesis is in accordance with terms and requirements

Supervisor: ...../signature/

Accepted for defence

Chairman of theses defence commission: .....

/name and signature/

# Non-exclusive Licence for Publication and Reproduction of Graduation Thesis<sup>1</sup>

I, Monika hereby

grant Tallinn University of Technology (TalTech) a non-exclusive license for my thesis Study the test steps to increase the Production Quality, supervised by Even Sekhri,

- 1.1 to be reproduced for the purposes of preservation and electronic publication, incl. to be entered in the digital collection of TalTech library until expiry of the term of copyright.

- 1.2 to be published via the web of TalTech, incl. to be entered in the digital collection of TalTech library until expiry of the term of copyright.

- 1.3 I am aware that the author also retains the rights specified in clause 1 of this license.

- 2. I confirm that granting the non-exclusive license does not infringe third persons' intellectual property rights, the rights arising from the Personal Data Protection Act or rights arising from other legislation.

21, December 2022.

<sup>&</sup>lt;sup>1</sup> The non-exclusive licence is not valid during the validity of access restriction indicated in the student's application for restriction on access to the graduation thesis that has been signed by the school's dean, except in case of the university's right to reproduce the thesis for preservation purposes only. If a graduation thesis is based on the joint creative activity of two or more persons and the co-author(s) has/have not granted, by the set deadline, the student defending his/her graduation thesis consent to reproduce and publish the graduation thesis in compliance with clauses 1.1 and 1.2 of the non-exclusive licence, the non-exclusive license shall not be valid for the period.

# ABSTRACT

Author: Monika

*Type of the work:* Master Thesis

Title: Product Quality Improvement Through Testing Procedures

Date: 21.12.2022

73 pages (the number of thesis pages including appendices)

University: Tallinn University of Technology

School: School of Engineering

Department: Department of Electrical Power Engineering and Mechatronics

Supervisor(s) of the thesis: Even Sekhri

Consultant(s): Salvador Gonzalez Perez

Abstract:

The purpose of the thesis is to research cases that can help to improve overall product quality in the manufacturing field. This research is a study based, where information is collected on historically available data, and based on that researcher has provided the available options for further implementation to improve the available processes in the manufacturing field. In this thesis, the author has used the six-sigma approach which is a study on defining; measuring; analysing; improving; controlling cases while handling process improvement management and project management skills. The conclusion of the study has been written in the thesis with the available options in the market. The improvements described in the thesis can be used by any of the manufacturing companies for future implementation to make improvements in their products. Obviously, improvements/processes can be modified according to the manufacturing company.

*Keywords:* Quality, Improvements, Master Thesis, PCB, Programming, Gage R&R.

# LÕPUTÖÖ LÜHIKOKKUVÕTE

Autor: MonikaLõputöö liik: MagistritööTöö pealkiri: Toote kvaliteedi tõstmine läbi testkatsete uuringuKuupäev:73 lk (lõputöö lehekülgede arv koos lisadega)

21.12.2022

Ülikool: Tallinna Tehnikaülikool

Teaduskond: Inseneriteaduskond

Instituut: Elektroenergeetika ja mehhatroonika instituut

*Töö juhendaja(d):* Even Sekhri

Töö konsultant (konsultandid): Salvador Gonzalez Perez

Sisu kirjeldus:

Lõputöö eesmärk on uurida juhtumeid, mis võivad aidata parandada üldist tootekvaliteeti. See uuring on uuring, mille käigus kogutakse teavet ajalooliselt kättesaadavatel andmetel ja selle põhjal on teadlane pakkunud olemasolevaid võimalusi edasiseks rakendamiseks tootmisvaldkonna olemasolevate protsesside täiustamiseks. Käesolevas lõputöös on autor kasutanud kuue sigma lähenemist, mis on defineerimise uurimus; mõõtmine; analüüsimine; parandamine; ja juhtumite kontrollimine protsesside täiustamise juhtimise ja projektijuhtimise oskustega. Uuringu järeldus on lõputöös kirjas turul saadaolevate võimalustega. Lõputöös kirjeldatud täiustusi saavad kasutada kõik tootmisettevõtted edaspidiseks rakendamiseks oma toodete täiustamiseks. Ilmselgelt saab täiustusi/protsesse muuta vastavalt tootmisettevõttele.

Märksõnad: Kvaliteet, täiustused, magistritöö, PCB, programmeerimine, Gage R&R.

## **THESIS TASK**

| Product Quality Improvement Through Testing        |

|----------------------------------------------------|

| Procedures                                         |

| Toote kvaliteedi tõstmine läbi testkatsete uuringu |

| Monika, 194534MAHM                                 |

| Department of Electrical Power Engineering and     |

| Mechatronics                                       |

| Master Thesis                                      |

| Even Sekhri                                        |

| Salvador Gonzalez Perez, Manager of Test Data      |

| Analyses                                           |

| 4 to 6 months                                      |

| 2022/2023 2022/2023 Autumn                         |

| 21.12.2022                                         |

|                                                    |

|                                                    |

|                                                    |

Supervisor (signature) Student (signature) Head of programme (signature)

Co-supervisor (signature)

#### 1. Reasons for choosing the topic

Author selected this topic \*Improvements in product quality\* to research because our company's main target is to provide quality products to our customers. Compromising the quality means compromising the growth of the company. Our Products have specified criteria and requirements for testing [1]. Usually, companies have different ways to check quality Like Functional checks by equipment, tests by creating a field environment, Inspections by an external inspector in the factory, final inspections on a platform, piece-by-piece inspections in the factory, training & auditing internal inspector in the factory

The author's main contribution to this task is to study/research different cases that are part and linked somehow with testing the products.

#### 2. Thesis objective

The thesis objective is to have researched existing techniques and documents for improving product quality using different approaches along the manufacturing cycle as introducing Product Control Board (PCB) level into the flow; preprograming at the component level to check on the final test only; checking how formal verification can help in quality; stressing the product under different ground/usability condition as high/low temperature and stressing the product in Stress TEST HW and SW solution for automating looping without forgetting improvements a right Not Fault Found (NFF) process and Gage R&R techniques[2]. This research is a compendium study to understand how important these are and to be aware of what could happen if they are not implemented and the cost related to it. To do it, readers have the luxury opportunity to check on a real supply innovative site in Estonia. Because some information is sensitive for the company some real values only have only available for internal company-related persons, and this is the reason that some references are not public.

#### 3. List of sub-questions

Test Steps that will be part of the Thesis:

- Chip/component quality test

- Programming at chip/component level

- Formal verification of SW

- PCB level test

- No-fault found (NFF)

- Gage R&R

- Stressing the product under different temperature

- Stress the product in looping to secure the stability of the test system

#### 4. Basic data

The author will use data analytics, test analytical, process improvement management, and project management skills to write the thesis and make research on the cases such as NFF, Gage R&R, PCB level test, stressing products under different environmental conditions, Pre-programming electronics components, and stressing test HW and SW solution in order to improve product quality. The author will get the data from the manufacturing companies and follow the generic processes. The data source will be existing data sources in companies and the google search engine. The company sources are not available for external references, even those are not accessible.

#### 5. Research methods

To finalize the thesis author will use the DMAIC process– A Six Sigma Process Improvement Methodology. DMAIC steps are DEFINE, MEASURE, ANALYZE, IMPROVE and CONTROL. Here researcher has used the DMAIC process in the sense that the author will write the definition/introduction, measurements, analysis, and improvements for the specific case written as per the study performed[3]. Different tasks will be done like; problem statement specifically on the test step, goal statement, project scope, team and responsibilities, time plan, estimated project benefits, etc. MINITAB, companies database will be used.

#### 6. Graphical material

Drawings, tables, and graphs will be part of the main work and will be presented once data will be analyzed.

#### 7. Thesis structure

Some chapter names are mentioned below, and sub-items will be added during thesis writing.

- Preface

- List of abbreviations and symbols

- Introduction

- List of figures

- Introduction

- Chip/component quality test

- Programming at chip/component level

- Formal verification of SW

- PCB level test

- Test based on no-fault found (NFF)

- Gage R&R

- Stressing the product under different temperature

- Stress the product in looping to secure the stability of the test system

- Summary

- List of references

• Appendix

#### 8. References

Companies' references are difficult to share, the author will use study sources from the companies, and because of confidentiality, it is not allowed to share. However, the author has added some external references related to product quality improvements. All the references are at the last of the thesis, I am using references in order to support processes written in the thesis. Some of the references are not my work.

#### 9. Thesis consultants

NA.

#### **10. Work stages and schedule**

| No. | Task                                            | Time plan  |

|-----|-------------------------------------------------|------------|

| 1.  | Collecting basic data                           | Wk45, 2022 |

|     |                                                 |            |

| 2.  | Verification and validate the product and the   | Wk46, 2022 |

|     | test quality system before its execution        |            |

| 3.  | Verification and validation of the test quality | Wk48, 2022 |

|     | result after execution                          |            |

| 4.  | Completing the first version of the work        | Wk50, 2022 |

| 5.  | Writing theoretical part                        | Wk50, 2022 |

| 6.  | Compiling a summary                             | Wk51, 2022 |

| 7.  | Sending to the supervisor (first reading)       | Wk52, 2022 |

| 8.  | Final submission                                | Wk02, 2023 |

| 9.  | Finalize presentation                           | 17.01.2023 |

# CONTENTS

| ABSTRACT                                                      |    |

|---------------------------------------------------------------|----|

| LÕPUTÖÖ LÜHIKOKKUVÕTE                                         |    |

| THESIS TASK                                                   |    |

| TABLE OF FIGURES                                              | 12 |

| TABLE of TABLES                                               | 13 |

| PREFACE                                                       | 14 |

| LIST OF ABBREVIATIONS AND SYMBOLS                             | 15 |

| INTRODUCTION                                                  | 17 |

| Overview                                                      | 17 |

| Background                                                    |    |

| Problem Statement                                             | 19 |

| Different techniques to be discussed                          | 21 |

| 1.CHIP/COMPONENT QUALITY TEST                                 | 22 |

| 1.1 Introduction                                              | 22 |

| 1.2 Advantages to implement chip level test                   | 22 |

| 1.3 Observations and suggestions                              | 22 |

| 1.3.1 Check components at the supplier end                    | 22 |

| 1.3.2 Test and verify components just before assembly         | 23 |

| 1.4 Overall conclusion                                        | 24 |

| 2. PROGRAMMING AT CHIP/COMPONENT LEVEL                        | 26 |

| 2.1 Introduction                                              | 26 |

| 2.2 Analysis and options                                      | 26 |

| 2.2.1 Program components at vendor end                        | 26 |

| 2.2.2 Programming system in at the final factory              | 27 |

| 2.3 Conclusion                                                | 30 |

| 3. FORMAL VERIFICATION OF SW                                  | 31 |

| 3.1 Introductions                                             | 31 |

| 3.1.1 Performed verification on Output power for Tx test case | 31 |

| 3.1.2 Performed verification on Delay for Rx test case        | 33 |

| 3.2 Conclusion                                                | 34 |

| 4. PCB LEVEL TEST                                             | 35 |

| 4.1 Introduction                                              | 35 |

| 4.2 Advantages                                                | 35 |

| 4.3 Facts and risks                                           |    |

| 4.3 Option                                                    | 36 |

| 4.4 Conclusion                                                                      |

|-------------------------------------------------------------------------------------|

| 5.TEST BASED ON NO-FAULT FOUND(NFF)                                                 |

| 5.1 Introduction                                                                    |

| 5.2 Author contribution to NFF investigation                                        |

| 5.3 Proposal on the NFF process40                                                   |

| 5.3.1 Information Flow43                                                            |

| 5.3.2 NFF impacting with solution flow44                                            |

| 5.3.3 Project Updates46                                                             |

| 5.4 Conclusion46                                                                    |

| 6. GAGE R&R                                                                         |

| 6.1 Introduction                                                                    |

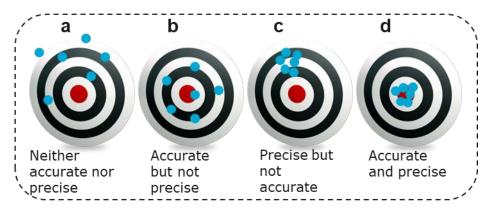

| 6.1.1 Measurement system and its terms49                                            |

| 6.1.2 Analysis done by the author based on historical data                          |

| 6.1.3 Analysis performed with help of technical engineers on Gage R&R53             |

| 6.2 Conclusion54                                                                    |

| 7.STRESSING THE PRODUCT UNDER DIFFERENT TEMPERATURE                                 |

| 7.1 Introduction55                                                                  |

| 7.1.1 Reliability introduction55                                                    |

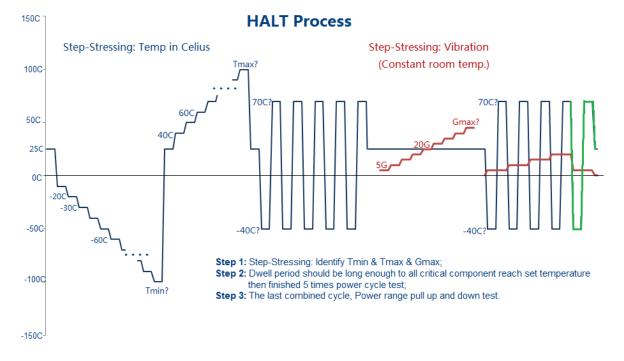

| 7.2 HALT                                                                            |

| 7.2.1 HALT; Stimulation vs. Simulation57                                            |

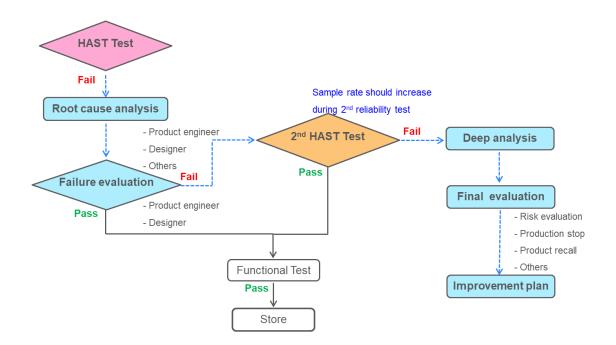

| 7.3 HAST58                                                                          |

| 7.4 Motivation to have HAST and HALT59                                              |

| 7.5 Measurements for the thermal chamber59                                          |

| 7.6 Conclusion60                                                                    |

| 8.STRESSING TEST BY LOOPING PRODUCT TO SECURE STABILITY OF THE TEST                 |

| SYSTEM61                                                                            |

| 8.1 Introduction61                                                                  |

| 8.1.1 How STRESS TEST HW and SW solution works                                      |

| 8.1.2 Tactic with Stress test HW and SW solution/clock-loop62                       |

| 8.1.3 Advantages for stressing test HW/SW solution in tester inside test SW release |

| 62                                                                                  |

| 8.2 Problem addressed63                                                             |

| 8.3 Process for Clock-test loop64                                                   |

| 8.3 Conclusion65                                                                    |

| SUMMARY66                                                                           |

| LIST OF REFERENCES                                                                  |

| APPENDICES                                                                          |

# **TABLE OF FIGURES**

| Figure 0 Generic process with the cases which will be discussed       | 19 |

|-----------------------------------------------------------------------|----|

| Figure 2.2.2(a) BPM 4910 Automatic Production Programming System      | 28 |

| Figure 2.2.2(b) BPM 3928 Automatic Production Programming System      | 29 |

| Figure 4.1 Yield process                                              | 35 |

| Figure 4.3(a) Columbia PCB test tester                                | 37 |

| Figure 4.3(b) Columbia PCB test palette                               | 37 |

| Figure 5.3(a) Draft version of wanted NFF process                     | 41 |

| Figure 5.3(b) Complex structure of NFF process                        | 42 |

| Figure 5.3.1 Draft version of wanted information flow for the week    | 43 |

| Figure 5.3.2(a) Detailed version of NFF process with responsibilities | 45 |

| Figure 5.3.2(b) FRAG readiness                                        | 45 |

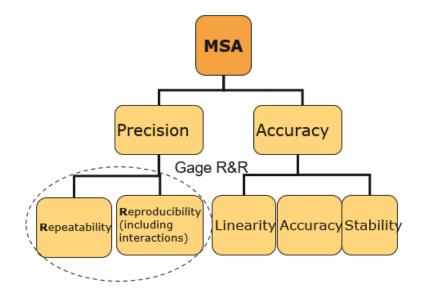

| Figure 6.1 Gage R&R measurements                                      | 49 |

| Figure 6.1.1 Types of Gage R&R measurement system                     | 49 |

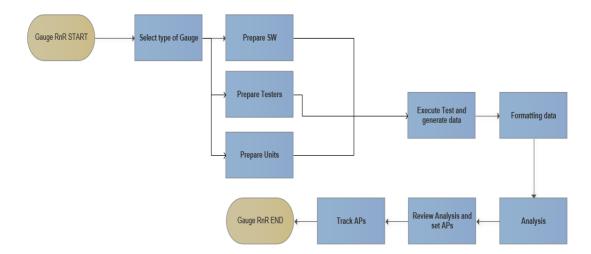

| Figure 6.1.2(a) Author's wanted process for Gage R&R                  | 51 |

| Figure 6.1.2(b) Gage R&R process with detailed responsibilities       | 52 |

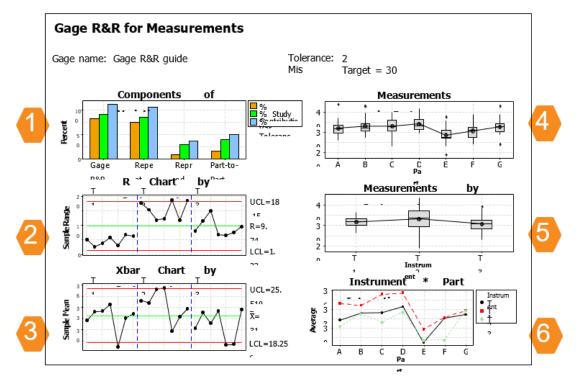

| Figure 6.1.3 Measured values for Gage R&R                             | 53 |

| Figure 7.1.1 Reliability introduction                                 | 56 |

| Figure 7.2 HALT process                                               | 57 |

| Figure 7.3 HAST process                                               | 58 |

| Figure 7.5 Thermal chamber                                            | 59 |

| Figure 8.1.3(a) Process of stressing test HW/SW solution              | 62 |

| Figure 8.1.3(b) Process of Clock Loop with detailed responsibilities  | 63 |

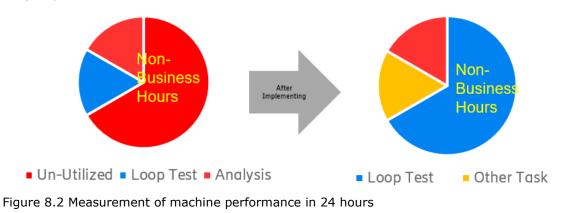

| Figure 8.2 Measurement of machine performance in 24 hours             | 64 |

| Figure 8.3 CL analysis user flow                                      | 64 |

# TABLE of TABLES

| Table 1 Measurement for TX output power on mid, high, and low power    | 32 |

|------------------------------------------------------------------------|----|

| Table 2 Measurement for output power for Rx with delay and delay phase | 33 |

| Table 3 Gauge R&R study                                                | 50 |

| Table 4 General criteria                                               | 50 |

| Table 5 Cost/Expense                                                   | 60 |

## PREFACE

The idea of this thesis is to study the test steps to improve production quality using different techniques. Quality improvement topic is a general topic in each and every organization and company. The author analysed that quality is the best key to make our customers happy. In that sense, the author thought to perform the investigation using different references and databases and identify the existing areas where some improvement and implementation can be made in the manufacturing companies.

In this topic, the author researched the gage R&R technique, the no-fault found process, the STRESS TEST HW and SW solution process where companies can improve the quality by stressing the product in loops, the technique to stress product in different environmental conditions, finding the way how to pre-program electronics component in respect to programming when assembled, and how to test the product at PCB level, etc. Different techniques are used, and different proposals are provided to the team for further study and implementation.

The author would like to express his gratitude to the supervisor of the thesis, Even Sekhri from Tallinn University of Technology, and Salvador Gonzalez Perez, the line manager of Test Data Analyses working for a telecom company in Estonia for assisting and supporting me in finalizing my thesis.

## LIST OF ABBREVIATIONS AND SYMBOLS

- BW Bandwidth

- CL Clock Loop

- DA Data Analyst

- DA Data analyst

- DFM Design for manufacturing

- DT Development team

- DU Design unit

- FNF Fault not found

- FRAG Fault rate analysis group

- HALT Highly accelerated life test

- HAST Highly accelerated stress test HAST

- HS Hansoft

- HW Hardware

- LA Line manager

- LT Leaders team

- MP Measurement point

- mPjM Maintenance project manager

- NFF No fault found

- NOK Not Ok

- PCB Printed circuit board

- PM Program manager

- PTDT product test development team

- PVT Production verification test

- QE Quality engineer

- R&R Repeatability + Reproducibility

- RCA Root Cause analysis

- Re-HALT Retest of Highly accelerated life test

- RF Radio frequency

- RM Resource management

- RTC Rapid thermal cycling

- SW Software

- TDE Test development engineers

- TDT Test development team

- TE Technical engineers

- TOR Transmission observation receiver

- TX Transmitter

- YWoR Yield without repair

# INTRODUCTION

## Overview

In this competitive environment, every company/field would like to provide their products with better quality to their customer to maintain the standard in the market. To beat the competitors, the key is delivering the best quality of products. In the existing telecommunication field, the companies those are competing are Intel, Taiwan semiconductors, Qualcomm, Micron, Ericsson Broadcom, and AMT, etc. Compromising with the quality means compromising the growth of the company. Every company is interested in maintaining the standards and values of its brands. Cost-efficiency and quality are the main factors and biggest challenges for a company to be achieved. However, to stay in this competition it should be maintained. In leading industrialized countries, a high-quality degree is necessary to remain competitive. For production, checking the quality of each product is challenging.

Human handling can cause defects in the products which could be at any stage during the production of the product. It does not matter which kind of product, but the quality check is important for every product, Software, or Hardware. Testing is the main factor to check the quality of the system. Testing is to determine whether the product meets the expected requirements or not. The main motive to test the product is to find errors, issues, bugs, and if the products match with the actual requirements or not, etc before sending the product to the customer. If in the case of the bug, an issue is found during the testing then it is easier to fix the issue in the early phase. It helps to save money if the bug or issue is reported during the testing then the products are found faulty at the customer end. It increases the return or claim rate. Testing helps to secure our internal information which can go out if having any bugs in the product. Checking the quality during production gives the best satisfaction of the customer which is the main objective of the company.

The quality function deployment method is an effective method of managing product quality and reliability improvement[4]. The main failure modes and causes can be obtained from the quality guarantee data statistical analysis and translated into customer requirements. The purpose of the thesis is to Study the different test steps which will be added to the existing generic processes to minimize the quality issues and improve yield. The study will be based on different failures and test steps.

## Background

The processes are already existing in our manufacturing companies however this research is based on the improvement of the existing processes [5]. Products have specified criteria and requirements for testing. Usually, companies have different ways to do quality checks like Functional checks by equipment, tests by creating a field environment, inspections by an external inspector in the factory, final inspections on a platform, piece-by-piece inspections in the factory, and training & auditing internal inspectors in the factory, etc.

Here the target is mainly on the test systems which help to provide better quality, and in that sense, testing will contribute to the overall projects differently. As the researcher has selected quality so here test is the area where to prove the quality of the products, in this study the techniques are to research.

- Chip/component quality test

- Introducing pre-programming chips.

- Formal verification of SW

- PCB level test

- No-fault found (NFF)

- Gage R&R,

- Stressing product under environmental conditions,

- STRESS Test HW and SW solution

The idea to perform or make a setup for Testing is to identify failures/defects, reduce the bugs/flaws in the system/product, and improve the overall quality. Improvement of quality plays the biggest role in capacity calculation as well. Testing makes sure the product is reliable to use and works perfectly at the customer end[6].

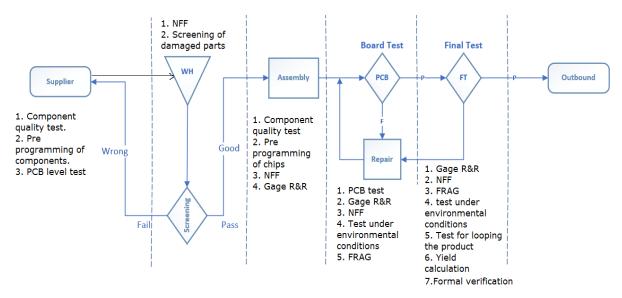

The generic process for producing a product is in figure 1, the author has explained his proposal for the process flow by marking the cases which he will introduce later in the thesis. This flow shows the manufacturing steps where cases for the quality check can be performed, this is prepared by the author by generalizing available data in manufacturing companies.

Figure 0 Generic process with the cases which will be discussed

## **Problem Statement**

Test setup already exists in the company to check the quality of products. In every step/field, humans are involved, and the defect can occur due to human errors and HW/SW issues which affect the quality of the product. It sometimes effects the capacity of the production because the production capacity is based on the quality and availability of test equipments[7].

To make sure 100% qualified products, companies need to add some more steps in the testing or inspection. However, every company always looks to have more qualified products to make our customers satisfied. Companies main target is to have a zero-return rate and zero claim rate. In one of the research projects, it is mentioned that for quality and testing inspection overall cost for new product development is <sup>2</sup>5000 to 50000 Euros. To have qualified products, companies need extra manpower, techniques, time to spend, and cost to focus only on quality to reach a 100% level of the quality.

The test flow usually in manufacturing companies are well stable to check the functionality of the product according to specific requirements however companies still have some failures which are found at the functional test and some of them are reported with the claim and return products. The issues which are found at functional test increase the disassembly and assemble time of the product and the quality issue

<sup>&</sup>lt;sup>2</sup> The values mentioned are just for analysis, values are valid for generic products for inspection of quality and for new product development. There is no connection between these numbers to any company relevant data or product

reported by the claim or return product increases the overall cost to the company[8]. In one of the research projects, it is mentioned that only 2:1 revenue will be acceptable for the manufacturing companies by the of the product is acceptable. Usually, zero is the ideal failure rate however it is not possible because of invisible bugs the acceptable return rate is <sup>3</sup>0% to 15% for the manufacturers[9].

$<sup>^{3}</sup>$  Return rate percentage is calculated on a generic level for research purposes.

## Different techniques to be discussed

**Chip/component quality test:** Introduction; Advantages to implement chip level test; Observations and suggestions, Check components at supplier end, Test and verify components just before assembly; and Overall conclusion.

**Programming at chip/component level:** Introduction; Analysis and options, Program components at vendor end, Programming system in factory; and Conclusion.

**Formal verification of SW:** Introductions, Performed verification on Output power for Tx test case, Performed verification on Delay for Rx test case; and Conclusion.

**PCB level test:** Introduction; Advantages; Facts and risks; Option; and Conclusion.

**No-fault found (NFF):** Introduction; Author contribution to NFF investigation; Proposal on the NFF process, Information Flow, NFF impacting with solution flow, Project Updates; and Conclusion.

Gage R&R: Introduction; and Conclusion.

**Stressing product under environmental conditions:** Introduction; HALT; HAST; Measurements for the thermal chamber; and Conclusion.

**STRESS Test HW and SW solution:** Introduction; Problem addressed; Process for Clock-test loop; and Conclusion.

## **1. CHIP/COMPONENT QUALITY TEST**

## **1.1 Introduction**

Chip/component test can be used to check the standalone electronics components at the beginning before assembly to any final product. Some of the electronic components are very expensive and some electronic components can not repair once install in a printed circuit board(PCB)[10]. Because of not having to repair properties for those electronic components it ends up in scrapping the whole printed circuit board. So in this research author is looking for an option to test electronic components in advance before assembly to minimize repair and scrap tasks. In research of chip/component level testers, the author will analyze what testers can improve the quality of the final product with help of checking to unassemble electronic components where the issues can be detected in advance. The author has gone through difficult conversations and situations as one of the most difficult tasks was to figure out what components to consider for the analysis. In the final, he decided to choose the components which are difficult to repair after assembling like BGA components (like Snowridge, Wolverine, and Grand Ridge, etc), and the components that can be received faulty batches from the supplier[11].

## 1.2 Advantages to implement chip level test

- Save disassemble time if chip issue can be detected in the early phase.

- Fewer products will go to scrap.

- Save manpower for repairing and assemble.

- Electronics components can be sent back to the supplier if found faulty batch.

- Check defective electronic chips in advance.

## 1.3 Observations and suggestions

#### 1.3.1 Check components at the supplier end

The author of the research analyzed that some expensive components can be tested and verified at the supplier's end just after the production of electronics components which is possible at the supplier's house. During the research[12], the author has been in the contact with the supplier to investigate how to move forward. During the conversations with the supplier Author's observations/risks

- Mode of conversation: Online meetings, Emails, etc.

- Who will own the cost of development and implementation (Supplier or factory)?

- At the supplier end, what will be the frequency level to test the components (100% or less)?

- How components will be isolated for tested and untested components if not tested at 100% level?

- How tested/not tested components will be identified if failed after assembly at the final production?

- Difficult to convince the supplier that their components are faulty.

- Difficult to make an agreement with the supplier as it is an extra step for them to implement in their production.

With the discussions/investigation with the supplier, the researcher has concluded that it is ok to make the development of such testers that can test at the component level at the supplier end. However, it will be only for components that have more failures. The cost of development and implementation can be discussed and depending on the factory it can be decided. One good thing one of the suppliers shared a possible board (Lake board tester) tester can be developed to verify their components. If the supplier agrees to make this development at their end it will help to improve <sup>4</sup>2 to 6 % of yield rate which is basically cost saving of retesting and repairing a product by approximately <sup>5</sup>10 to 70 euros. It is not finally decided how to isolate the tested and untested components however there are a few suggestions like the tested components can have an extra level with the mark but it is not easy to implement. The discussions are still ongoing to finalize component verification at the supplier end. Here new investigation will come into the picture to find the solution to segregate the tested and untested electronic components, Author will not talk about that here.

#### 1.3.2 Test and verify components just before assembly

During the analysis of chip-level testing, the author of the research analyzed the existing option where the author can verify electronic components just before assembly at final production house[13]. For this investigation, the author has been in referring the

<sup>&</sup>lt;sup>4</sup> Values are calculated based on generic processes, the percentage has not any linked with any specific company.

<sup>&</sup>lt;sup>5</sup> This value is calculated by plotting different companies costs for repairing and repairing per product. The number can vary depending on the products and processes of the manufacturing company.

available data for the manufacturing companies to analyze the current situation. During the conversations with the internal stakeholders author's observations and open questions

- Mode of conversations: Online meetings, Emails, and offline discussions, etc.

- Who will be developing such tester (HW+SW)?

- Same chips/components will be used in different products, how to segregate?

- What will be the frequency level to test the components (100% or less)?

- How components will be segregated between tested and untested components?

- How components will be identified if failed after assembly at final production?

- What will be done with the component if tested component failed at final assembly test? Etc.

During theinternal discussion, the researcher has lots of open questions the biggest one is thatthe components company received for further use are produced by the supplier so theresponsibility for the quality of the component should also be of the supplier. Whichis a valid point. However, the Author analyzed that company might need atester/fixture which can be developed by one of the suppliers(Lake board tester) foranalysis purposes in the troubleshooting area or repair area.

#### **1.4 Overall conclusion**

The author has analyzed that both the given options to verify electronics components as per the requirement before they assemble to any PCB are for now NOK means conditionally acceptable where the conditions are already written in the above clauses. The author's next task will be to resolve the open question so that the development of electronic components can be started quickly. Overall for chip level quality check, it is under discussion to finalize it[14]. The conclusion for the research on chip-level tests is that the author has made a study as an electronics/technical engineer to minimize failures because of BGA components and improve the overall yield at the production. With overall calculation, the Authors receive the pre-qualified and verified electronics components for the assembly on PCB, which will save the cost of <sup>6</sup>10 to 120 USD per

<sup>&</sup>lt;sup>6</sup> The cost mentioned is calculated for the general technique used to test electronic components for quality, it is calculated by plotting different processes at manufacturers.

product which is basically a saving of 2% to 7% of yield improvement. The future trend to have testers for electronics components will obviously rise based on investigations.

## 2. PROGRAMMING AT CHIP/COMPONENT LEVEL

## 2.1 Introduction

During the research to improve the overall quality of the production, the researcher found that programming of electronics programmable component level is another option to save the overall test time and improve quality with the precheck. The idea came into the picture when the researcher analyzed that overall test time is high and one part of the final test is the programming of electronics components. Usually, programming takes 3-6 mins on the electronics components depending on what components are to be programmed. With this level, companies can have the chance to secure preprogrammed chips/components for the final assembly and testing[15]. Preprogram is to configure chips used in the products in advance and then assemble them on the specific product/PCB to reduce the over testing time and check in advance if the chip has some programming issue.

Overall test time with programmed chips can be reduced at the final functional test because at the functional test then no need to perform programming of the components which is approx from 3 to 6 mins. On the other hand, preprogrammed chips will help in improving quality by checking the functional chips in advance.

#### Advantages

- Reduce overall testing time at the final level

- Less products will go to scrap by verifying the programming issue.

#### Disadvantages

• Without some electronics around is not possible to pre-program

## 2.2 Analysis and options

#### 2.2.1 Program components at vendor end

The researcher has analyzed that it would be good if the author can have discussions with the supplier who supplies the programmable components. The author's idea behind having conversations with the supplier is to get preprogrammed components from the supplier itself to minimize extra handling time in final product production[16]. During the conversations with the vendor researcher observations/risks

- Mode of conversations: Online meetings, emails, etc.

- Who will own the cost of development and implementation of the programming tester/system?

- How components/chips will be segregated if programmed/calibrated/data or not programmed?

- Difficult to convince the supplier to make them agree to implement programming system at their production.

- How to track which chips are delivered for which product with what programming?

With the discussions with vendors, the researcher has concluded that it is ok to make the development/implementation of such a programming system which can provide preprogrammed to save overall testing time at the final stage. However, it will be difficult to segregate the programmed and not programmed chips as the vendor delivers the components in batches with not any marks and it would be difficult to isolate them. The components are recognized by their specific number or name so all particular chips will have specific product numbers. The author is keeping this topic for further investigation to finalize programming at the supplier end. This is difficult at the component vendor end as well as it is an additional requirement from manufacturing companies.

#### 2.2.2 Programming system in at the final factory

During the analysis of pre-programmable system implementation, the author of the research analyzed that usually companies have an option where they can implement/develop a programming system of programmable components before assembly in-house as well[17]. For system implementation in-house, the researcher has gone through discussions with the internal stakeholders to analyze the existing situations and risks. Author's conversation and analyzed risks with internal stakeholders

- Mode of conversations: Online meetings, emails, and offline discussions, etc.

- The biggest considerable risk that mixing chips/components with the different SW which will be used in different products.

- What will be done with the component if having a programming issue before the final assembly? etc.

The researcher has summarised the overall discussion with the internal stakeholders. Usually, programmable chips can be used in different products with a different configurations. if the author agrees to do programming at our factory, it seems that it will lose the flexibility to use programmable chips. In-house companies usually have a high chance to mix up the programmed chips which can lead to more scraps of the final products because the same programmable chips can be used in different products which means that those chips will have the same Product number. The researcher analyzed that in generic when the same component is usable in different products it is hard to decide what programming has been added to the particular component [18]. However, the author investigated the available testers/systems in the market which can be used for the in-house programming of chips. Below are the two options for automatic production programming systems which are investigated by the author.

BPM 4910 Automatic Production Programming System

- Faster and Easier

- Up to 1,708 Devices per Hour

- Component Handling Range: 0402 to 240-pin QF

- Architecture: 9TH Gen Concurrent Programming System with Vector Engine Co-Processor

Figure 2.2.2(a) BPM 4910 Automatic Production Programming System

BPM 4910 Proposed Configuration

- FP4910 Programming System (1 to 12 Pgm/site, 1-4 sockets/site, 48 sockets)

- 3 x X900 Auto Programming Site, (1 to 4 sockets/site, 12 sockets) [18]

- Assembly, monitor arm, auto

- 1-Tray Assembly

- FSW49 BP4900 Software Support

- FSWAPI49 API Software Feature 49x0

- TM-50 Tape output Loader

- Safety door, 4xside

- Xstream tape input & take up 4x

- Xstream series tape FDR 16mm

- Xstream series tape FDR 12mm

- Standard spare parts kit, 4910

- Installation & Education, 3 days onsite or web-based

- Proposed BPM 4910 System Price: € 335,000.00

BPM 3928 Programming System:

- Award-winning BPW TM Software

- Handler Throughput: Up to 1,432 Devices per Hour

- Component Handling Range: 0402 to 240-pin QFP

- 9TH Gen Concurrent Programming System with Vector Engine coprocessor

Figure 2.2.2(b) BPM 3928 Automatic Production Programming System

## 2.3 Conclusion

The researcher concluded from the overall investigation that both the options programming at factories or programming at the vendor end are fittable. However, for further research, the author will find the solution to open question the one is how to segregate the programmed and unprogrammed components to make an accurate final assembly. To implement a programming system author need to set up effortless sorting of programmed chips according to their configuration where the author can decide with some label or automatic which configured chip has which program and to which product it will assemble. Both options available for programming systems BPM 4910 and BPM 3928 are acceptable depending on in-house requirements. With this implementation, overall <sup>7</sup>3 to 7 mins and 1 to 2% of yield will improve on functional tests at the manufacturing site.

<sup>&</sup>lt;sup>7</sup> This data is for research purposes only and it is calculated based on common processes and available options, there is no direct link of this data to any of the companies.

## **3. FORMAL VERIFICATION OF SW**

## **3.1 Introductions**

The researcher has studied that companies formal verification of SW s done to verify if the prepared SW for the product is according to the test requirement of the product and fittable for the produced product[19]. This verification will check if the SW is correct or not, if the procedure or steps of the SW are correct, if is it according to the product specifications or not, if the SW is stable or not, etc. This procedure of verifying each and every step of the test case of SW is done by the SWverify tool. Once the complete SW is ready and 100% implemented according to the test requirement of the product, the author analyzed few weeks are needed to verify each and every step of the SW. Once formal verification is done for the SW, the product can be produced for customer orders. If the product gives deviation in the result, the information with isolation values will be sent to the design unit(DU)[20] or to the test SW development team(TDT) to check the test requirement again and align it according to the deviation values. The author has approached responsible stakeholders to understand and study how to perform formal verification of SW, which will be explained in 3.1.1.

#### 3.1.1 Performed verification on Output power for Tx test case

For the research, the author has chosen a simulated case for experimenting with TX output power on mid-power, high power, and low power. The experiment consists of a circuit with a power amplifier with which TOR will be calculated. In this experiment, some power is injected and then output power will be calculated. The verification process consists of 10 samples on different BW on 32 test points. This data is just for experiment purposes, nothing related to the real product, and try to find what is the deviation with help of the transmission observation receiver(TOR). For the below measurements, there is an approximately <sup>8</sup>0.4 - 0.5 dB difference between production results for the verification setup corresponds with general distribution from the database tool with verification product results in production being the outliers. Data from the verification setup also corresponds with data from the same product, when measurements were performed on Station X.

<sup>&</sup>lt;sup>8</sup> This value is calculated based on values measured and generic values available for the output power for the TX test, it is an estimation, not a real value.

The conclusion for the below measurements is that the result is passed because in measurements, there is an approximately 0.4 - 0.5 dB difference between product results for the verification unit and the peak values, obtained on verification setup. The difference in the expected value is only with marginal value and it will be investigated further to see why this happens. A few experimental measurements are mentioned below.

|              |                                                | TC 1 Test   | TC 1 Test   |         | Measure |           |       |       |       |       |       |       |       |       |       |       |       |       |

|--------------|------------------------------------------------|-------------|-------------|---------|---------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Test Point   |                                                | Point Limit | Point Limit |         | d       | Standard  |       |       |       |       |       |       |       |       |       |       |       |       |

| Code         | Test Point Name                                | Low         | High        | #Sample | Average | Deviation | Min   | Max   | TC 1  | TC 2  | TC 3  | TC 4  | TC 5  | TC 6  | TC 7  | TC 8  | TC 9  | TC 10 |

| 1.11.10.0.0  | TX Output Power_mid Pwr: [0] dB branch D (A)   | -0.30       | 0.30        | 10.00   | -0.11   | 0.01      | -0.12 | -0.09 | -0.09 | -0.10 | -0.11 | -0.11 | -0.11 | -0.09 | -0.09 | -0.10 | -0.11 | -0.11 |

| 1.11.10.0.1  | TX Output Power_mid Pwr: [0] dB branch C (B)   | -0.30       | 0.30        | 10.00   | -0.12   | 0.01      | -0.14 | -0.10 | -0.11 | -0.11 | -0.12 | -0.13 | -0.11 | -0.11 | -0.10 | -0.11 | -0.13 | -0.12 |

| 1.11.10.0.2  | TX Output Power_mid Pwr: [0] dB branch B (C)   | -0.30       | 0.30        | 10.00   | -0.13   | 0.02      | -0.15 | -0.10 | -0.11 | -0.12 | -0.13 | -0.15 | -0.13 | -0.10 | -0.11 | -0.13 | -0.14 | -0.14 |

| 1.11.10.0.3  | TX Output Power_high Pwr: [-3] dB branch D (A) | -0.30       | 0.30        | 10.00   | -0.08   | 0.01      | -0.09 | -0.05 | -0.08 | -0.08 | -0.08 | -0.09 | -0.08 | -0.05 | -0.05 | -0.09 | -0.09 | -0.09 |

| 1.11.10.0.4  | TX Output Power_high Pwr: [-3] dB branch C (B) | -0.30       | 0.30        | 10.00   | -0.08   | 0.01      | -0.09 | -0.05 | -0.08 | -0.08 | -0.08 | -0.09 | -0.09 | -0.05 | -0.06 | -0.08 | -0.09 | -0.09 |

| 1.11.10.0.5  | TX Output Power_high Pwr: [-3] dB branch B (C) | -0.30       | 0.30        | 10.00   | -0.08   | 0.02      | -0.10 | -0.04 | -0.08 | -0.08 | -0.09 | -0.10 | -0.10 | -0.04 | -0.06 | -0.08 | -0.09 | -0.09 |

| 1.11.10.0.6  | TX Output Power_low Pwr: [-3] dB branch D (A)  | -0.30       | 0.30        | 10.00   | -0.05   | 0.02      | -0.07 | 0.00  | -0.04 | -0.03 | -0.05 | -0.06 | -0.05 | 0.00  | -0.02 | -0.05 | -0.04 | -0.06 |

| 1.11.10.0.7  | TX Output Power_low Pwr: [-3] dB branch C (B)  | -0.30       | 0.30        | 10.00   | -0.06   | 0.02      | -0.08 | -0.02 | -0.05 | -0.05 | -0.06 | -0.07 | -0.07 | -0.02 | -0.04 | -0.06 | -0.05 | -0.07 |

| 1.11.10.0.8  | TX Output Power_low Pwr: [-3] dB branch B (C)  | -0.30       | 0.30        | 10.00   | -0.06   | 0.02      | -0.09 | -0.02 | -0.06 | -0.06 | -0.07 | -0.07 | -0.07 | -0.02 | -0.04 | -0.06 | -0.05 | -0.07 |

| 1.11.10.0.9  | TX Output Power_mid Pwr: [-3] dB branch D (A)  | -0.30       | 0.30        | 10.00   | -0.09   | 0.01      | -0.10 | -0.06 | -0.09 | -0.09 | -0.09 | -0.10 | -0.09 | -0.06 | -0.07 | -0.09 | -0.09 | -0.10 |

| 1.11.10.0.10 | TX Output Power_mid Pwr: [-3] dB branch C (B)  | -0.30       | 0.30        | 10.00   | -0.09   | 0.01      | -0.10 | -0.06 | -0.09 | -0.09 | -0.09 | -0.10 | -0.09 | -0.06 | -0.08 | -0.09 | -0.09 | -0.10 |

| 1.11.10.0.11 | TX Output Power_mid Pwr: [-3] dB branch B (C)  | -0.30       | 0.30        | 10.00   | -0.10   | 0.02      | -0.12 | -0.05 | -0.10 | -0.11 | -0.11 | -0.11 | -0.11 | -0.05 | -0.08 | -0.09 | -0.10 | -0.11 |

| 1.11.10.0.12 | TX Output Power_high Pwr: [0] dB branch E (E)  | -0.70       | 0.30        | 10.00   | -0.10   | 0.02      | -0.12 | -0.06 | -0.10 | -0.11 | -0.09 | -0.09 | -0.09 | -0.06 | -0.10 | -0.09 | -0.10 | -0.12 |

| 1.11.10.0.13 | TX Output Power_high Pwr: [0] dB branch F (F)  | -0.70       | 0.30        | 10.00   | -0.08   | 0.01      | -0.10 | -0.06 | -0.08 | -0.09 | -0.07 | -0.07 | -0.06 | -0.06 | -0.08 | -0.07 | -0.08 | -0.09 |

| 1.11.10.0.14 | TX Output Power_high Pwr: [0] dB branch G (G)  | -0.70       | 0.30        | 10.00   | -0.10   | 0.01      | -0.11 | -0.07 | -0.10 | -0.10 | -0.09 | -0.09 | -0.08 | -0.07 | -0.10 | -0.09 | -0.11 | -0.11 |

| 1.11.10.0.15 | TX Output Power_low Pwr: [0] dB branch E (E)   | -0.70       | 0.30        | 10.00   | -0.08   | 0.01      | -0.10 | -0.05 | -0.08 | -0.09 | -0.09 | -0.09 | -0.08 | -0.05 | -0.08 | -0.07 | -0.09 | -0.10 |

| 1.11.10.0.16 | TX Output Power_low Pwr: [0] dB branch F (F)   | -0.70       | 0.30        | 10.00   | -0.07   | 0.01      | -0.08 | -0.05 | -0.07 | -0.07 | -0.07 | -0.08 | -0.06 | -0.05 | -0.07 | -0.06 | -0.08 | -0.08 |

| 1.11.10.0.17 | TX Output Power low Pwr: [0] dB branch G (G)   | -0.70       | 0.30        | 10.00   | -0.07   | 0.01      | -0.08 | -0.05 | -0.06 | -0.07 | -0.07 | -0.08 | -0.06 | -0.05 | -0.07 | -0.05 | -0.08 | -0.07 |

Table 1 Measurement for TX output power on mid, high, and low power

Explanation on terms used in the experiment

- Test point code: It is the code to identify what test point has what number.

- Test point name: It is the name of the test performed.

- TC 1, Test Point Limit Low: Test case 1 measurement for low limit

- TC 1, Test Point Limit high: Test case 1 measurement for high limit

- #Sample: The samples on what measurements have taken.

- Measured Average: Average measured values

- Standard Deviation: Deviation calculated on measured values

- Min: Minimum measured values at production.

- Max: Maximum measured values at production

- TC1 to TC10 is the measurement value for test cases 1 to 10 with 10 units.

<sup>&</sup>lt;sup>9</sup> The measured values are just for experiment, no relation of these values with any real measurements.

#### 3.1.2 Performed verification on Delay for Rx test case

For further studies of formal verification of SW, the author has chosen another parameter for an experiment which is output power for Rx with delay. This is an experiment on a product that differs from the real implementation. The author has chosen a simulated case for experimenting with TX output power on mid-power, high power, and low power for one of our products. The author has taken verified the case with 1 sample on different BW on 32 test points, this data is just for the experiment nothing related to the real product. For this verification the sample rate is 1 product of different BW, this data is just for experiment purposes with this data nothing to do with the real product. According to the test requirement, the pass criteria are defined for Rx AGC phase delay and Rx delay frequency response.

Explanation on terms used in the experiment

- Test point code: It is the code to identify what test point has what number.

- Test point name: It is the name of the test performed.

- TC 1, Test Point Limit Low: Test case 1 measurement for low limit

- TC 1, Test Point Limit high: Test case 1 measurement for high limit

- #Sample: The samples on what measurements has taken.

- Measured Average: Average measured values

- Measurement done: Value for measurements done

- diff PROD-performed: Is the difference in production and values measured

|           |                            |           |           | ay unu  | uciuy   | Jiluse  |           |

|-----------|----------------------------|-----------|-----------|---------|---------|---------|-----------|

|           |                            |           | TC 1 Test |         |         |         |           |

| Test      |                            | TC 1 Test | Point     |         | Measure | Measure | diff PROD |

| Point     |                            | Point     | Limit     |         | d       | ments   | Performe  |

| Code      | Test Point Name            | Limit Low | High      | #Sample | Average | done    | d         |

| 1.11.1.00 | RX_AGC_DELAY agc Port: 0   | -10.00    | -1.00     | 1.00    | -6.09   | -8.03   | 1.94      |

| 1.11.1.01 | RX_AGC_DELAY agc Port: 1   | -10.00    | -1.00     | 1.00    | -5.35   | -8.5    | 3.15      |

| 1.11.1.02 | RX_AGC_DELAY agc Port: 2   | -10.00    | -1.00     | 1.00    | -7.36   | -8.54   | 1.18      |

| 1.11.1.03 | RX_AGC_DELAY agc Port: 3   | -10.00    | -1.00     | 1.00    | -5.87   | -8.81   | 2.94      |

| 1.11.1.04 | RX_AGC_DELAY agc Port: 4   | -10.00    | -1.00     | 1.00    | -6.99   | -8.84   | 1.85      |

| 1.11.1.05 | RX_AGC_DELAY delay port: 0 | 600.00    | 700.00    | 1.00    | 634.00  | 659.84  | -25.84    |

| 1.11.1.06 | RX_AGC_DELAY delay port: 1 | 600.00    | 700.00    | 1.00    | 661.00  | 653.61  | 7.39      |

| 1.11.1.07 | RX_AGC_DELAY delay port: 2 | 600.00    | 700.00    | 1.00    | 614.00  | 653.96  | -39.96    |

| 1.11.1.08 | RX_AGC_DELAY delay port: 3 | 600.00    | 700.00    | 1.00    | 632.00  | 661.08  | -29.08    |

| 1.11.1.09 | RX_AGC_DELAY delay port: 4 | 600.00    | 700.00    | 1.00    | 645.00  | 662.64  | -17.64    |

| 1.11.1.10 | RX_AGC_DELAY delay3port: 0 | 525.00    | 625.00    | 1.00    | 581.00  | 572.13  | 8.87      |

| 1.11.1.11 | RX_AGC_DELAY delay3port: 1 | 525.00    | 625.00    | 1.00    | 579.00  | 566.27  | 12.73     |

| 1.11.1.12 | RX_AGC_DELAY delay3port: 2 | 525.00    | 625.00    | 1.00    | 580.00  | 567.96  | 12.04     |

| 1.11.1.13 | RX_AGC_DELAY delay3port: 3 | 525.00    | 625.00    | 1.00    | 567.00  | 570.14  | -3.14     |

| 1.11.1.14 | RX_AGC_DELAY delay3port: 4 | 525.00    | 625.00    | 1.00    | 568.00  | 570.65  | -2.65     |

| 1.11.1.15 | RX_AGC_DELAY phase port: 0 | -3.00     | 6.00      | 1.00    | -1.10   | 4.27    | -5.37     |

| 1.11.1.16 | RX_AGC_DELAY phase port: 1 | -3.00     | 6.00      | 1.00    | -0.10   | 4.99    | -5.09     |

| 1.11.1.17 | RX_AGC_DELAY phase port: 2 | -3.00     | 6.00      | 1.00    | 0.40    | 4.77    | -4.37     |

| 1.11.1.18 | RX_AGC_DELAY phase port: 3 | -3.00     | 6.00      | 1.00    | 0.40    | 4.22    | -3.82     |

| 1.11.1.19 | RX_AGC_DELAY phase port: 4 | -3.00     | 6.00      | 1.00    | 0.10    | 3.82    | -3.72     |

#### Table 2 Measurement for output power for Rx with delay and delay phase

<sup>&</sup>lt;sup>10</sup> The measured values are just for experiment, no relation of these values with any real measurements.

In the above snip, the Author has reported only a few values. Here researcher has some reverse values which are not according to the test requirements. The Delay limit is lying between D 600 to 700,  $\Phi$ diff, 0->1: -4~7,  $\Phi$ diff, 1->9: -11~1. However, delay limits are different which the author will not mention as per the confidentiality of the test requirement. One example from the above snip: {"value": 653.65, "unit": "ns", "limType": 3, "lim1": 600.00, "lim2": 700.00}. The above logs used for experimenting have been taken from the log file of the test, and it clearly shows that due to the wrong limits defined in the test requirement it failed. These all values are for experimental purpose only, it has no any relation with the real life products.

## 3.2 Conclusion

With the above performances, the Author concluded that verification of SW with the verified products should be necessary for the quality. For formal verification of SW, a 100% verified, tested and calibrated product should be used to get accurate results. Values which was measured will be considered reference value and can be used in the future for tester verification[21]. Another point is that the same product can be used as a reference product to measure with other faulty products to match product quality and to find issues in the faulty products. The first experiment result for verification on Output power for the Tx test case is passed and it is as per the test requirement. Another test performed for verification on output power for the Rx test case failed and it has reverse values and the result is not according to the test requirement defined by the design unit(DU). The instruction can be shared with the design unit for updating the test requirement and software package for further verifications. If the product does not pass this formal verification of SW, that means that the product does not match the actual values of the hardware and the requirement which shows that the hardware product has some issues. The efforts made to make this experiement takes usually <sup>11</sup>1-2 days and the cost for performing one experiment will be approximately 100 to 250 USD.

<sup>&</sup>lt;sup>11</sup> Estimations are based on calculations for the generic process.

# 4. PCB LEVEL TEST 4.1 Introduction

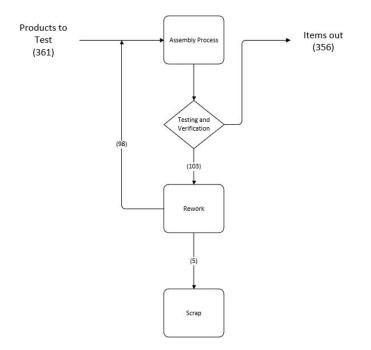

During the research to improve product quality, the idea of testing the PCB board came into the picture. The researcher has observed a test can be performed after the assembly of all the electronic components. So basically with some investigation, the author has found that through stressing PCB board testing can be performed before mechanical parts assembly to the printed circuit board. With PCB testing, the issues on the electronic components can be detected in advance. As PCB level test will help to improve the overall testing yield, which is usually measured by the software which measures first pass and overall yield [22]. Yield is measured by the proportion of correct/passed products in comparison to the overall products you put in. Please refer below image(In this case yield will be: 356/361 = 0.98%)

Figure 4.1 Yield process

## 4.2 Advantages

- Avoid to mount faulty PCBs in final products.

- PCB level tester could be cheaper than the final functional test after assembly.

- Saves disassembly and re-assembly time for faulty products.

- Overall Testing yield = PCB-level yield \* functional-level yield

- PCB level tester might help to reduce testing time at the functional level as some of the test steps can be skipped from the final functional test which is also passed at the PCB level.

- According to the investigated results it will help to improve functional level yield.

## 4.3 Facts and risks

If test all mass products on the PCB level with an automatic PCB tester

- At the PCB level tester, it has a high chance to damage the components, as the PCB board has all the electronics open components without any mechanical protection which will be easily damaged and will lead to more scrapping cost [23]

- If the author makes an agreement, it should be aligned with all production sites, as well as author's opinion is to pay more for the equipments.

If test all volumes on the PCB level with a manual PCB tester

- With manual tester it has even more chances to damage the components because the tester will be handled manually, and still open components will exist which will take to more scrap cost.

- Suggestion to have only on premature builds or in early phase builds to verify product requirements.

- More manual work however, companies are moving towards automation.

- Need experts to work on Mass production testing, difficult to be handled by production operators.

## 4.3 Option

During the investigation, the researcher found a company named Columbia a Swedish brand, those works on electronics fixtures including HW and SW. Columbia gives the chance to the customers to get customized fixtures according to customers requirements. The researcher also found an available fixture that can be customized according to the requirement of the product [24]. Below is the picture of Columbia's existing tester which can be modified in different sizes and requirements based on the product. For this option, the companies can provide the product specifications to make modifications to the existing testers [25]. To find

Figure 4.3(a) Columbia PCB test tester

Figure 4.3(b) Columbia PCB test palette

## 4.4 Conclusion

In the study of the PCB level testing, the author analyzed that author needs to ask Columbia to customize the PCB fixture according to companies products with different sizes and functions. On the other way, such testers can be developed at the production factories as usually NPI sites have HW and SW development teams that can develop such testers as well. The research is made only on the existing product which is open on the search engines and can be purchased by anyone according to the requirement. It is good that Columbia provides the full package including hardware and software so for customers, it is easy to just implement. With the PCB tester for the research data, it is calculated that approximately <sup>12</sup>50 to 450 USD cost can be saved only by saving disassembly and assembly time. Yield without repair can be improved by  $^{13}1\%$  to 6% on the overall yield. will On the other side, scrapping costs might increase with <sup>14</sup>1 to 4% of overall scraps, Columbia company has also its products specification on its website as well so can be followed easily. Overall PCB level testing will help to find the issues of assembling electronic components on a printed circuit board. However, in the investigation, it has been noted that the PCB fixture will be complex HW as high-quality requirements of the products towards handling PCB board and overall automation strategy will make it more complex.

<sup>&</sup>lt;sup>12</sup> Estimated disassembly and assembly time is calculated based on product assembly time including handling time with respect to products available globally in telecom industries, this value is not based on real product.

<sup>&</sup>lt;sup>13</sup> Yield without repair is calculated by plotting different data from already research done.

<sup>&</sup>lt;sup>14</sup> Estimated scrapping cost is measurement done based on the research data, no link to real data.

# **5. TEST BASED ON NO-FAULT FOUND(NFF)**

# 5.1 Introduction

NFF is introduced as no-fault found. This is considered when the author has a fault but can not decide the cause of the fault in the product. The cause in NFF can be anything, product issue, test HW issue, test SW issue, component issue, stability issue, and environmental issues, etc. When it is difficult to know the reason for the fault, it is hard to implement the improvement or diagnose the fault. During the research to improve product quality, the researcher summarized that if author can reduce the NFF level that will ensure yield improvement or product quality in any of the production factories. [26]. In a generic way, NFF depends on different conditions like SW, HW instability, shift change, the person with more experience, etc. As we discussed in the previous chapter that first pass yield and yield without repair(YwoR) are two different measurement terms, which is another way to introduce that NFF exists.

# 5.2 Author contribution to NFF investigation

- The NFF process must be implemented when the product is ready for customer delivery and finished its NPI phase and moved to the maintenance phase. However, in some cases, NPI phase can also have NFF.

- NFF investigations start when it is highlighted by the Quality engineer during development activities or monitoring activities.

- At the first, test data analysis must discover fluctuations in test results and precategorize the root cause. After that the Quality department performs the sorting and initial evaluation of test cases of NFF impact, then the Fault analysis group will decide to discuss the impact and cause with different functions of the product development.

- Apply the NFF process during the new product development (NPD) phase is complicated because the product itself is not mature and usually the main focus of production in the NPI phase of the product is on making product with important quality issues. Another issue in the manufacturing field is that the quality of the resources needed to perform RCA and time to volume made it difficult for companies to deal with it from priorities and cost points of view besides new products development.

**Proposal** on resource requirements: The author just proposed only one new process, however, for NFF there can be different proposals one of them is explained in detail: NFF Coordinator: The NFF coordinator should be responsible to care about the needed processes to solve NFF and increase the stability of Hardware/Software.

NFF Coordinator: will participate actively in the meetings to advise regarding resource estimation and assignment according to the priority of the test case which has NFF. This role will be almost like a project manager who will consider a single NFF as a project by aligning resources, priorities, risks, effects, timeframe, etc.

Technical Resources/Engineers: The technical resources will be working on a test case which will be shared by the NFF coordinator to find the cause of the NFF. Technical resources will be responsible to obtain the technical solution for each NFF. Technical resources should give the ideas to resolve the NFF that occurred on the products to make it stable including HW and SW. NFFs are usually complex in nature and only experienced engineers who have a deep understanding of product systems, test systems, internal processes, and knowledge of historical issues should handle the NFFs.

Other active roles: A quality Engineer (QE) can be appointed as a quality inspector to perform inspection virtually and onsite to evaluate the NFF impact, and impact on product quality, and production capacity and to check what products are affected. QE will be the person who will create the backlog and continuously monitor the solutions.

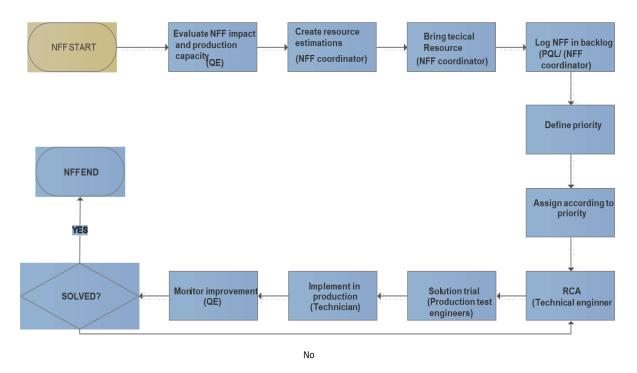

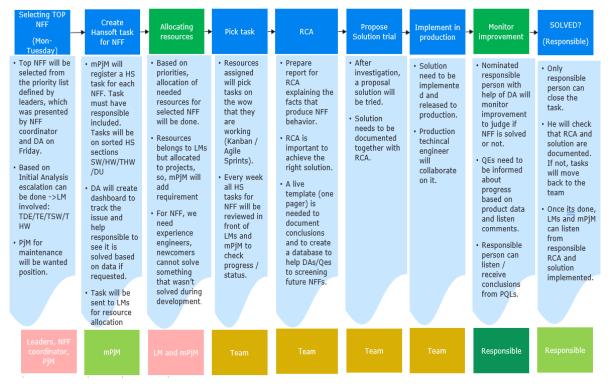

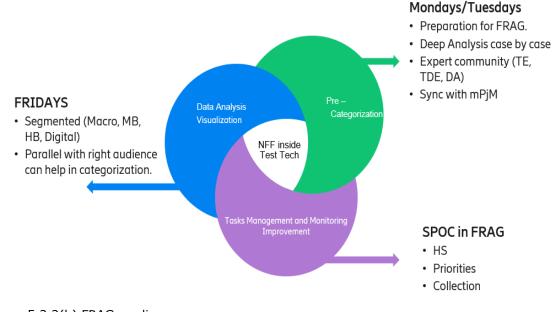

# 5.3 Proposal on the NFF process

Companies usually have existing processes to resolve NFFs however in some generic existing processes this is the proposal from author's side. The researcher has studied an NFF process to implement in production to track and work on NFF cases that occurred in the production site. The process will start by evaluating the NFF impact and production capacity of the quality engineer and information will be sent to the NFF coordinator to create resource estimation and bring the responsible technical resources into the picture. Then NFF coordinator will create the priority of the task and schedule a discussion to discuss the NFF with the technical engineer and accordingly assign the task to the responsible engineer. Technical engineers will create a Root cause analysis (RCA). Once TEs find the root cause they will implement the solution and send the

solution to production for trial and monitoring[27]. The QE will be monitoring and tracking the results of implemented solution on the case.

If QE will notice that issue has been resolved and no further issues have occurred, then the particular NFF case will be closed. If during the monitoring phase, QE finds that the NFF percentage for the case is decreased or no positive result then he should inform it back again to technical engineers to work again on the case. Below is the drafted process.

Figure 5.3(a) Draft version of wanted NFF process

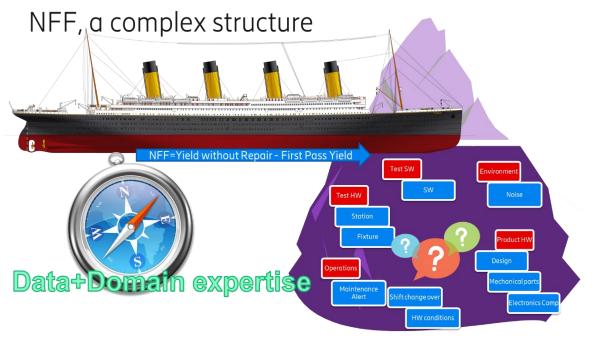

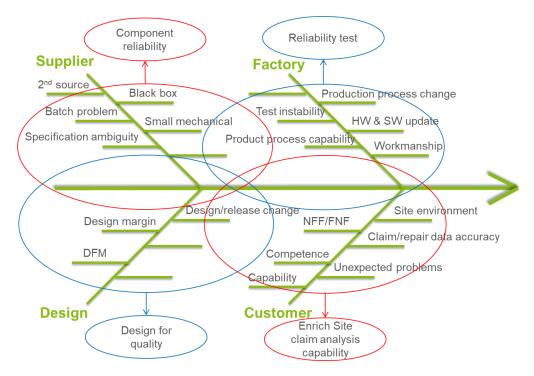

The author has put NFF's difficult situation in a process or complex structure below. The researcher has considered that in production sites, not only product and test sites are responsible for disasters to produce NFFs. Other factors like HW stability, noise, design, and shift change are also responsible to decrease overall production yield[28].

Figure 5.3(b) Complex structure of NFF process

Existing challenges to implementing the NFF process which need to be solved

- Researcher noticed that a responsible driver should be assigned.

- Dedicated team should be appointed.

- NFF case causes are hard to find.

- Difficult to track progress or implementing solutions.

- Need good collaboration with QE and NFF coordinator and use the same source data and angle of visualization.

- It is hard to provide the solution by the technical team as the reason behind failure is not defined.

- Challenge on Categorization NFF, Hard to do without expertise in the discussions.

- Challenge to assign tasks and define priorities.

- Author observed that the NFF rate must be on the scorecard.

- Setting up good visualization Per project, Program, Shift, and Testers. The team should use a systematic approach

- Evaluate the possibility to receive subscription DF dashboards.

- Evaluating the new criteria for analysis that if the product failed once should consider it into account for quality checking.

- Evaluating process to add tester's info with classification per segment, yield, test time, and including a ranking formula to help technical engineers and the NFF coordinator.

#### 5.3.1 Information Flow

- NFF issues are not related specifically for a week, however, the process in detail is prepared by the author to report weekly.

- NFF coordinator will be suggested according to the program for each NFF. A responsible NFF coordinator should be appointed to delegate, follow up and implement the solution.

- Resource management (RM) is only on a needed basis: To participate in weekly NFF business reports, supporting the priorities, and Allocation of resources.

- Test data analyses (DA) should be responsible to facilitate and automate complex reports from different angles into simpler reports. Keeper of "NFF scorecards", "NFF improvement monitor" dashboard, and "On radar" dashboards.

- Product Quality engineers (QE) will check with the responsible NFF coordinator the status of the NFF solution proposed and implemented based on technical engineers (TE).

- Plan to have a tracking tool for checking the progress for NFF solutions with transparency.

| Finalizing unit<br>having issue<br>(Monday)                                                                                                                                                                                                          | Preparation for<br>FRAG<br>(Tuesday)                                                                                                                                                                                                                                                                                                                                                                                                          | FRAG<br>discussions<br>(Wednesday)                                                                                                                                                                                                                                                                                                                                                                          | Preparing NFF<br>score cards<br>(Thursday)                                                                                                                                         | Internal review<br>NFF scorecards &<br>APs<br>(Friday)                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|