TALLINN UNIVERSITY OF TECHNOLOGY

School of Information Technologies

Tolulope Emmanuel Ademilua 184584 IASM

# OPTIMIZATION OF TEST DATA GENERATION FOR SOFTWARE-BASED SELF-TEST PROCESSORS

Master's thesis

Supervisor:Professor, Raimund-Johanness UbarCo. Supervisor:Stephen Adeboye Oyeniran, M.Sc

Tallinn 2020

# Author's declaration of originality

I hereby certify that I am the sole author of this thesis. All the used materials, references to the literature and the work of others have been referred to. This thesis has not been presented for examination anywhere else.

Author: Tolulope Emmanuel Ademilua

11.05.2020

## Abstract

This paper develops a new paradigm for generating and optimizing test data for softwarebased tests of processors. The work aims to find the optimal amount of test data for testing processors with RISC architecture, which would ensure wide coverage of high- and lowlevel faults. The quality of software-based tests on processors depends on the test program, but the quality of the test program depends on the test data. The new concept is based on the separate generation of tests for the control and data processing parts of the processor modules, which are defined by a set of certain processor functions. The generation of test data is based on the division of the set of functions to be tested into groups, where a high-level decision diagram model is used to find the optimal distribution. The optimization criterion is to ensure maximum fault coverage with a minimum amount of test data at the minimum time required to generate tests.

An innovative approach has been developed to minimize the amount of memory required to store tests by minimizing test data. The novelty of the work is expressed in two aspects: (1) the savings of memory required for storing the test by minimizing the test data, and (2) the wider coverage of high- and low-level fault classes achieved by generating highquality test data.

Experimental studies have been performed with a miniMIPS microprocessor. The experiments were able to demonstrate that the developed method provides high fault coverage at both high and low levels, but with fewer test data than the previous method. The result ensures high reliability and dependability of the processors.

### Annotatsioon

# Testandmete optimeerimine protsessorite tarkvarapõhistele testidele

Käesolevas töös arendatakse uut paradigmat testandmete genereerimiseks ja optimeerimiseks protsessorite tarkvarapõhistele testidele. Töö eesmärgiks on leida optimaalne testandmete hulk RISC-arhitektuuriga protsessorite testimiseks, mis tagaksid laia kõrg- ja madalatasandi rikete katte. Protsessorite tarkvarapõhiste testide kvaliteet sõltub testprogrammist, aga testprogrammi kvaliteet sõltub omakorda testandmetest. Uus kontseptsioon põhineb testide eraldi genereerimisel protsessori moodulite juht- ja andmetöötlusosadele, mis on defineeritud teatavate protsessori funktsioonide hulgaga. Testandmete genereerimine põhineb testitava funktsioonide hulga jaotamisel gruppideks, kus optimaalse jaotuse leidmiseks kasutatakse kõrgtaseme otsustusdiagrammide mudelit. Optimeerimiskriteeriumiks on tagada maksimaalne rikete kate minimaalse testandmete hulgaga minimaalse testide genereerimiseks kuluva aja juures.

Töös on arendatud uudne lähenemine testide salvestamiseks vajaliku mälumahu minimeerimiseks testandmete kokku pakkimise teel. Töö uudsus väljendub kahes aspektis: (1) testandmete minimeerimise teel saavutatav testi salvestamiseks vajaliku mälumahu kokkuhoid, ja (2) kõrge kvaliteediga testandmete genereerimisel saavutatav laiem kõrg- ja madalataseme rikete klassi kate.

Eksperimentaaluuringud on töös läbiviidud mikroprotsessoriga MiniMIPS. Eksperimentidega õnnestus demonstreerida, et väljatöötatud meetod tagab kõrge rikete katte nii kõrg- kui ka madalal tasandil, kuid seejuures väiksema testandmete hulgaga, kui senise meetodi puhul. Saadud tulemusega on tagatud protsessorite kõrge usaldusväärsus ja töökindlus.

# List of abbreviations and terms

| ATG    | Automated Test Generation                         |

|--------|---------------------------------------------------|

| ATPG   | Automated Test Pattern Generation                 |

| SBST   | Software-Based Self-Test                          |

| MP     | Microprocessor                                    |

| SAF    | Stuck at Fault                                    |

| BDD    | Binary Decision Diagram                           |

| SSBDDs | Structurally Synthesized Binary Decision Diagrams |

| ROBDD  | Reduced Ordered Binary Decision Diagram           |

| HLDD   | High Level Decision Diagram                       |

| CUT    | Circuit Under Test                                |

| SLL    | Shift Word Left Logical                           |

| SRL    | Shift Word Right Logical                          |

| SRA    | Shift Word Right Arithmetic                       |

| SLLV   | Shift Word Left Logical Variable                  |

| MFHI   | Move from HI Register                             |

| MFLO   | Move from LO Register                             |

| HDL    | Hardware Description Language                     |

| ATPG   | Automated Test Pattern Generator                  |

| ISA    | Instruction Set Architecture                      |

| MUT    | Modules Under Test                                |

| HL     | High Level                                        |

| S-A-0  | Stuck-At-0                                        |

| S-A-1  | Stuck-At-1                                        |

| RISC   | Reduced Instruction Set Computer                  |

| RAM    | Random Access Memory                              |

| MSF    | Multiple Stuck-At Fault                           |

| CPU    | Central Processing Unit                           |

|        |                                                   |

| FRF | Fanout-Free Region |  |  |

|-----|--------------------|--|--|

| SOC | System-On-Chip     |  |  |

# Table of contents

| Author's declaration of originality                                              | 3    |

|----------------------------------------------------------------------------------|------|

| Abstract                                                                         | 4    |

| Annotatsioon Testandmete optimeerimine protsessorite tarkvarapõhistele testidele | 5    |

| List of abbreviations and terms                                                  | 6    |

| Table of contents                                                                | 8    |

| List of figures                                                                  | . 10 |

| List of tables                                                                   | . 11 |

| 1 Introduction                                                                   | . 12 |

| 1.1 Background and problem of SBST                                               | . 12 |

| 1.2 Objectives                                                                   | . 14 |

| 1.3 Thesis organization                                                          | . 14 |

| 1.4 Overview of work                                                             | . 15 |

| 2 Processor                                                                      | . 17 |

| 2.1 Digital System                                                               | . 18 |

| 2.1.1 Development life cycle of a digital system                                 | . 18 |

| 2.2 Digital System Testing                                                       | . 19 |

| 2.3 Faults                                                                       | . 19 |

| 2.3.1 Defects, Error, Failure                                                    | . 19 |

| 2.3.2 Classification of faults                                                   | . 21 |

| 2.4 Fault models                                                                 | . 22 |

| 2.4.1 Stuck-at-faults                                                            | . 22 |

| 2.5 Fault simulation                                                             | . 23 |

| 2.6 Levels of Abstraction in Digital System Testing                              | . 23 |

| 2.7 Importance of Digital System Testing                                         | . 25 |

| 3 State-of-the-Art for testing processor                                         | . 26 |

| 3.1 Summary of state-of-the-art                                                  | . 29 |

| 4 High Level Decision Diagrams                                                   | . 31 |

| 4.1 Overview of Decision Diagrams                                                |      |

| 4.1.1 History of Decision Diagram                                                | . 32 |

| 4.2 HLDD                                                                         | . 33 |

| 4.2.1 List of Faults affecting the Operation of MP            | 35 |

|---------------------------------------------------------------|----|

| 4.2.2 High-Level Fault Modelling for MP with HLDDs            | 35 |

| 4.2.3 Complexity and Accuracy in Fault Model                  | 36 |

| 4.3 MiniMIPS ISA                                              | 37 |

| 4.4 HLDD Generation for MP                                    | 39 |

| 4.5 The Relationship of SSBDDs and HLDDs                      | 43 |

| 4.6 Benefit of HLDDs to generate test for MP                  | 44 |

| 4.7 Synthesis of HLDDs                                        | 45 |

| 4.8 HLDD Conclusions                                          | 47 |

| 5 Test generation for microprocessor                          | 48 |

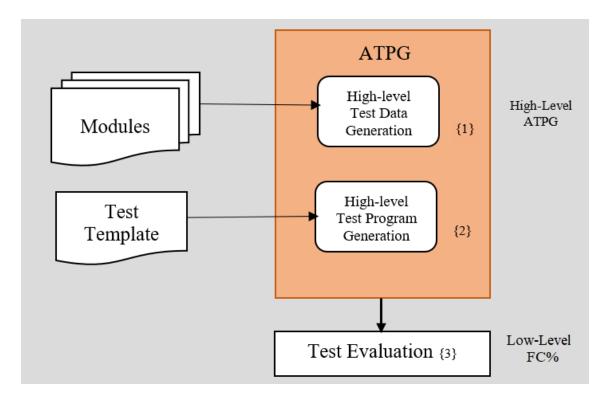

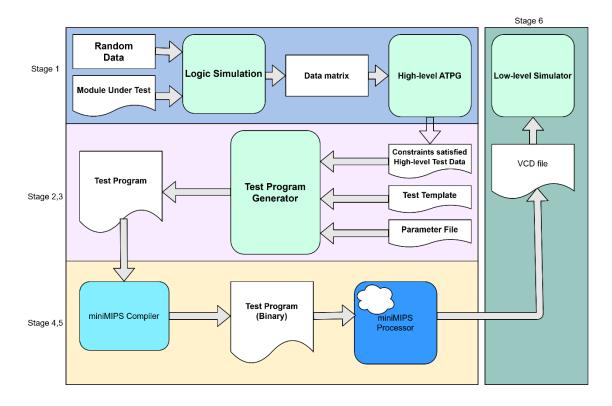

| 5.1 Test data generation concept                              | 48 |

| 5.2 The roles of HLDDs in test generation for microprocessors | 52 |

| 5.2.1 Conformity Test for processor                           | 53 |

| 5.3 Test program generation                                   | 55 |

| 5.4 Using HLDDs for instruction set partitioning              | 57 |

| 5.5 Conclusion                                                | 63 |

| 6 Experimental part of the thesis                             | 64 |

| 6.1 SBST and Experimental Contributions                       | 64 |

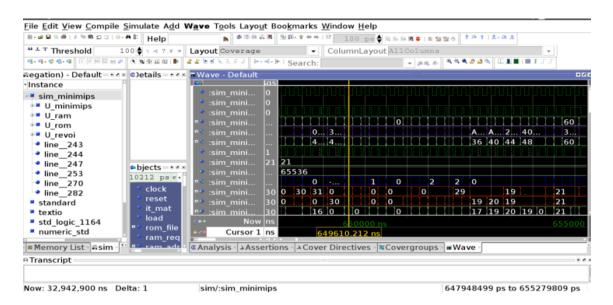

| 6.2 Research environment                                      | 66 |

| 6.3 Experimental research on test generation for MiniMIPS     | 67 |

| 6.3.1 High-Level structural test generation with HLDDs        | 68 |

| 6.3.2 High-Level functional test generation with HLDDs        | 70 |

| 7 Conclusion                                                  | 73 |

| 8 References                                                  | 75 |

| Appendix 1 – Program Description and Manual                   | 80 |

| Appendix 2 – Structure of the miniMIPS Processor              | 84 |

| Appendix 3 – CPU Specification for the experiments            | 85 |

| hldd.py                                                       | 86 |

| merge.py                                                      | 88 |

| simulate.py                                                   | 89 |

| random.py                                                     | 90 |

# List of figures

| Figure 1. RISC Register Window 17                                                       |

|-----------------------------------------------------------------------------------------|

| Figure 2: Process of Testing Digital System 19                                          |

| Figure 3: A NAND Gate with one input shorted to ground 20                               |

| Figure 4: Comparison of Fault free and Redundant Faulty gate                            |

| Figure 5: classification of faults                                                      |

| Figure 6: Level of Abstraction [29]                                                     |

| Figure 7: Behavioural Level Structure of the Microprocessor [4] 40                      |

| Figure 8:Generated HLDD for a subset of instructions of MP with 19 decision nodes. 41   |

| Figure 9. Digital system as a network of components and a flowchart of its behaviour.45 |

| Figure 10. Illustration of Unit under Test 49                                           |

| Figure 11: Mapping between the instruction formats and the HLDD functional variable.    |

|                                                                                         |

| Figure 12:Algorithm for conformity test                                                 |

| Figure 13: Structure of Conformity test 55                                              |

| Figure 14. Architecture of the test program [74] 56                                     |

| Figure 15: The tasks of SBST generation flow in this thesis                             |

| Figure 16: Tool framework for test generation                                           |

| Figure 17: High-Level tool framework in action for test generation                      |

| Figure 18: Structures notated as G=1 and G =3                                           |

| Figure 19: Set of HLDDs G8 70                                                           |

| Figure 20: Test Program generator response from Linux terminal                          |

| Figure 21: Generating dump file for fault coverage evaluation                           |

# List of tables

| Table 1: Difference between a defect and a fault   |                               |

|----------------------------------------------------|-------------------------------|

| Table 2: Proposed submitted method Compared w      | with other methods [33] 30    |

| Table 3: Full miniMIPS instruction set [69] [14].  |                               |

| Table 4: Instructions selected for Experiment      |                               |

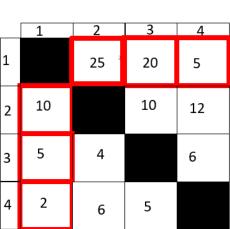

| Table 5: Sample of Matrix table for partitioning 4 | instructions 59               |

| Table 6. Shows how weights are assigned to patte   | erns 59                       |

| Table 7. Expansion of Table 6                      |                               |

| Table 8: Shows the list of patterns and weights ba | sed on relationship 61        |

| Table 9: Selection case 1                          | Table 10. Selection case 2 61 |

| Table 11. Selection case 3                         | Table 12. Selection case 4 61 |

| Table 13. Node-Based Test Generation fault cove    | rage result69                 |

| Table 14. Partitioned-based approach fault covera  | ge result71                   |

## **1** Introduction

This thesis addresses how to generate an efficient test data for testing processor. The main emphasis is that the quality of test data determines the quality of the test program used by SBST in testing the processor. Hence, the level of fault coverage in the processor depends on the quality of the test program used. Based on this fact, we developed an optimal method to optimize test data generation by an algorithmic partitioning of the instruction set architecture of the processor under test. A good ordering of instructions set for test data generation is presented. A novel concept of HLDD synthesis was used to generate the test program.

This introductory chapter presents the background and problems of SBST leading to this research, followed by a more detailed objective. Finally, an overview of the thesis structure is provided.

# 1.1 Background and problem of SBST

The realization of SBST started in 1980 after the semiconductor industry was challenged to develop a novel testing method that can be integrated into MP test flow, due to the increase in technology advances [1]. Today even more technology advances in digital systems with massively parallel computing now exists, which open gaps into more way of reasoning how systems could be tested correctly without delays in system release to the market. The main subject in the SBST methodology is the test program generation, which must comply with the high-quality fault coverage standards imposed by the industry [2] [3]. The major problem of SBST when considering high-level faults is the difficulty of proving that the model covers all the low-level detectable faults [4]. The SBST approach is based on software programs that are designed to test the functionality of the processor cores [5]. The key idea of SBST is to make full use of on-chip programmable resources to run normal programs that test the processor itself [6]. RISC processor is a system with a judicious restriction to a small set of often used instructions with an architecture tailored to fast execution of all the instructions in this set [7]. The use of SBST techniques for testing of a modern processor cannot be underestimated because of the ease of synthesis using functional approaches, coverage for difficult to test faults, non-intrusive nature, low hardware overhead [8]. However, the test synthesis time required by SBST is high and it is a problem that relates to the test program used. The test program is an assembly program devised to extract information that reveals the correctness or valid operation of the machine that executes it, rather than calculating a function or performing a task. Test programs may be used to validate the correctness of a processor design or to check the correct functionality of a device after production [9]. The complexity of the present digital systems has rendered gate-level test generation impractical. However, functional testing has been developed as an alternative by researchers [10].

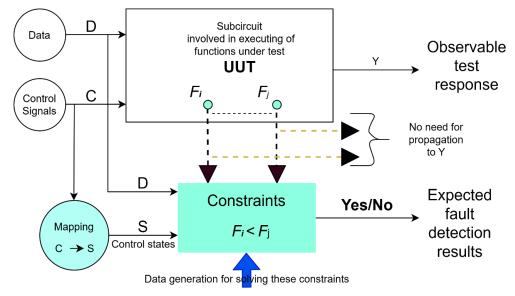

The quality of the SBST is mainly affected by the test data used in test programs [4]. In [11], divide and conquer approaches were considered for modules under test to generate high-quality test data by ATPG. However, the difficulties of this method set from the fact that functional constraints are needed to guide the ATPGs in order to produce functionally feasible test patterns. As stated in [12], the random test patterns are an alternative way to generate test data for MUTs. Researchers in [13] proposed two constraints in generating test data for detecting control faults based on partitioning the instructions of MP on an HLDD. These constraints are control constraints to activate the desired working modes of the processor and the data constraints to test if the selected working modes were correctly selected [13] [14]. This thesis will also make use of the two constraints to generate the test with HLDD. However, we have optimized the process of partitioning the instructions of the MP on HLDD with an automated program that generates the HLDD, which is opposed to the previous ways of manually generating the HLDD. We will further elaborate on the automation of the HLDD generation under the contribution section in this thesis. In [15], the synthesized test program proposed for  $\mu$ GP techniques could not realize a gate-level fault coverage more than 90% because it could not detect the hard-to-detect faults. The inadequate fault coverage gave rise to greedy based evolutionary approaches by Suriasarma which detects 40% of the hard-to-detect faults but the synthesis time is longer [16]. This brought researcher in [4] [14] into the limelight that testing MP at a high level of abstraction using HLDD to generate the test program improves the test program quality and it ensures a better fault coverage that covers the gate level faults inclusively. Raimund et al. emphasized in [17] that fault model for digital circuits have been developed for a different type of failure mechanisms like signal line bridges, transistor stuck-opens or failures due to increasing circuit delays. However, the oldest general fault modelling mechanisms that can effectively analyse arbitrary fault types is called the D-Calculus [18]. In [13], a novel method for implementationindependent test generation

for modules of RISC type microprocessors was proposed. According to the method it covers a larger class of faults than the traditional single SAF. This implementation independence of tests was achieved by testing separately the control and data path of the module explicitly.

In summary, we conclude that the challenges of SBST are the compacted test program generation which depends on the quality of the test data, since the test program is the determinant of the quality of the fault coverage.

According to [14] the proper testing of the MP after manufacturing process guaranteed and enhanced the reliability of the MP during the operational stage. This test remains crucial for the safety purpose of the safety-critical systems like MP.

This leads to the goal of this thesis.

# **1.2 Objectives**

The objective of this thesis is to optimize the test data generation for MP in order to achieve high fault coverages both at high and low-level. Thus, different experiments have been carried out by automated transforming the given instruction set of the MP into different HLDDs. The goal of this thesis is divided into three phases each with a goal of optimizing test data for testing processor. Hence, this thesis presents the following goals:

- I. To develop a mathematical model for partitioning the set of instructions under test.

- II. To optimize the test data generation for testing of the MP at high-level.

- III. To prove that the high-level faults model covers all the low-level detectable (non-redundant) faults.

# **1.3 Thesis organization**

The thesis is consists of 7 chapters.

Chapter 1 introduces the thesis, which includes the background and problem of SBST, and objectives.

Chapter 2 presents the background information about the processor, digital systems, defect, faults, fault model and level of abstraction in developing digital systems.

Chapter 3 outlines the state of the art for testing of the processor. It covers in-depth ongoing research for testing of the processor. It also contains some literature review of related work of this topic. The summary of the state-of-the-art is then presented.

Chapter 4 describes the methodology flow for generating a fault model. First, the correlation between the DDs is studied, followed by the High-level decision diagram used for grouping functions together for a simulation-based test. Furthermore. It also contains the literature review of the related works of this topic.

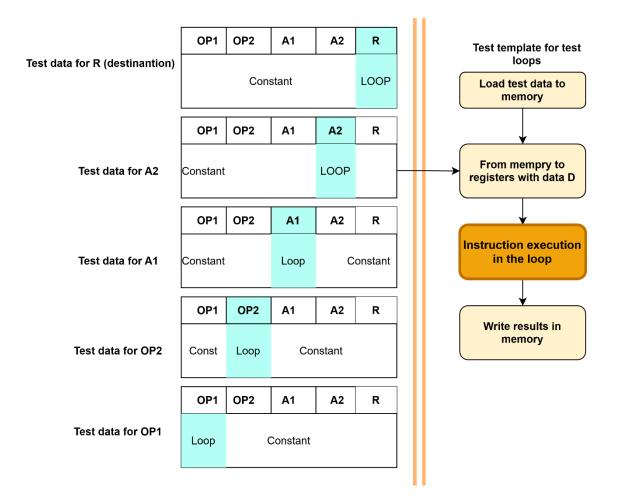

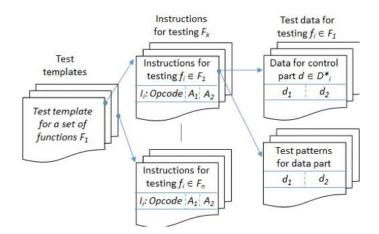

Chapter 5 presents the test generation approaches; it covers the test data generation and test program generation, and it presents the algorithm proposed for HLDD generation in this thesis.

Chapter 6 describes the research environment for the SBST, and the experimental results are presented.

Chapter 7 summarizes the conclusion and presents the future research direction.

### **1.4 Overview of work**

A novel approach is proposed for generating test data for SBST at high-level with regards to the followings. The approach is based on automating the partitioning set of instruction on HLDDs. An optimal test-data is then generated from the partitioned set of instructions. The HLDD is synthesized to generate the test program for testing the processor. The algorithmic partitioned approach of instruction set improves the test program quality, reduces memory size usage and ensures a better fault coverage as it considered the needed patterns for a certain test based on the test data generation constraints. Our approach on test generation for the processor using high-level decision diagram is to represent the functional behaviour of the instruction set of the processor in a way that it is easy to observe and traverse its paths in the HLDD to the terminal node. The processor is then tested at high-level and the test covers the gate-level faults inclusively. There are two approaches in testing at high-level, thus, in this thesis, the functional approach is used. The functional approaches use instruction set architecture, whereas the structural approaches are based on test generation using information from the lower level of design (gate-level or RTL-level description) of the processor under test [11, 19] [20, 9]. Due to the increasing complexity of digital circuits that has renders classical gate-level test generation impractical, high-level fault models are used widely in the field of SBST [11, 9].

The good way through which the instruction sets can be partitioned to generate highquality test data for the test program is presented.

The processor is tested at high-level without resorting to its implementation details. The results for the experiments cover both high-level and gate-level inclusively.

The method for achieving an optimum test data generation is based on the algorithmic partitioning of the instruction set on HLDD, which reduces the memory size usage of the MP for storing the test program and ensure high fault coverage for both high-level(functional) and gate-level (lower-level) faults.

### 2 Processor

In this chapter, I present briefly the fundamental concepts of RISC processor design and its subcomponents used for designing the processor before diving into the state-of-the-art of testing the processor. Special emphasis is placed on testing of the processor, which is the main goal of this thesis. The modern technology advances are imposing new challenges on processor testing with billions of transistors which can operate at gigahertz frequencies [4]. The first RISC was developed with a high volume of software with hardware support for only the most time-consuming events [7]. The reason then was based on the limited transistors that can be integrated onto a single chip [7]. The transistor is the central component of the processor's circuitry [21] However, the reliability of the transistor is becoming enervated since its geometry dimension approaches further down the nanometre dimension [22]. According to Moore's law in every 18 months the number of transistors on integrated circuits doubles [23], [14]. The development in semiconductor technology and nanotechnology are strengthening the existence of this law. Nowadays advances in VLSI technology make it possible to realize the minicomputers of before on a single chip of silicon [7]. Hence, testing at the gate level is becoming more difficult. Most of the RISC instructions are "register-to-register" and take place entirely inside the chip and the data memory is restricted to the LOAD and STORE instructions [7]. The overhead of an MP is reduced with banks of registers equipped during architectural design of the MP, this simplifies the process of procedure call by changing a hardware pointer, thus avoiding the overhead of saving registers in memory [7].

|    | GLOBAL | LOW |     | LOCA | L   |     | HIGH |     |

|----|--------|-----|-----|------|-----|-----|------|-----|

| R0 | R9     | R10 | R15 | R16  | R25 | R26 |      | R31 |

Figure 1. RISC Register Window

The instructions in the processor can be grouped into four categories [7] such as:

- I. Arithmetic-logical

- II. Memory access

- III. Branch

The execution time of the RISC processor is given by the cycle it takes to read a register, perform an ALU operation, and store the result back into a register [16]. I further present the foundation of MP as a digital system.

### 2.1 Digital System

Digital system is a system that stores data with 0 and 1, this system could be sequential or combinational. There might be combinations of 0s and 1s for a system to be operative in some conditions. The 0 refers to as OFF and 1 as ON. As a result, digital circuits are the foundation for computers and digital communication. It was invented in twenty centuries [20]. The complexity of digital circuits has rendered gate-level test generation impractical [21]. This has led to the development of SBST to reduce test generation complexity for a complex digital system like a processor. The goal is for the new approach to incorporates the benefits of functional (high-level) testing and still retains the accuracy of gate-level fault models.

#### 2.1.1 Development life cycle of a digital system

The developmental approach of the digital system starts with system requirements. What will the system do? Based on that fact, testing is not exceptional. Digital systems undergo three major stages [14]:

- Design

- Production

- Operation

Each stage is prone to error. Hence, each stage needs to undergo review along the design process. Several models have been used, such as vee model, waterfall model and linear model, in order to follow up design specification. This model guides the process. However, it doesn't stop an error to occur. At the design stage, there could be misinterpretation or omission of the specification [14]. Fault in the production stage could be as a result of component defects or defects due to component assembly issues. When the system is operational, the system can suddenly fail due to the undetected defects

during production or due to environmental factors. Testing then remains the main factor to assure us that the system is doing what is supposed to do.

## 2.2 Digital System Testing

Testing a digital system means checking if the system is working according to the specification of its design and production for operational use.

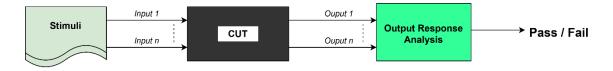

This process starts with passing sets of inputs known as stimuli into the CUT, which at that time is also referred to as a black box. Then the black box is checked to see if it is working in accordance to specifications, by observing its response at the output terminal.

Figure 2: Process of Testing Digital System

The main reason for testing is to find out if the device is free of defects. A defect can lead to faults. Fault can lead to an error. An error can lead to failure.

## **2.3 Faults**

### 2.3.1 Defects, Error, Failure

A defect is a failure mechanism in an electronic system which is the unintended physical difference between the implemented hardware and its intended design [24], [25]. Defects may therefore, cause deviation in system specifications".

A fault is the representation of defects at the abstracted functional level (electrical, Boolean or functional malfunction) [24]".

#### Table 1: Difference between a defect and a fault

| Defect                   | Fault                    |

|--------------------------|--------------------------|

| Imperfection in hardware | Imperfection in function |

Multiple faults (functional deviations) could occur due to a single physical defect (deviation from intended specifications) on a chip and these multiple faults my not been detected by a single test type. An error is an unexpected output signal produced by a defective system".

*Failure* is the result of an error, e.g. A bad processor can usually cause system failure if the processor is not functioning properly.

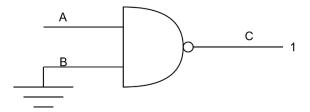

Also, defects, fault and error are examined with *Figure*. 3 below:

Figure 3: A NAND Gate with one input shorted to ground

- A defect, in this case, is the connection of input B to ground, since the output of a NAND gate produces only 0 when its inputs are 1. Therefore, the defect in its specification will facilitate an error. In the presence of the short, we will only have input combination 10 and 00 there will be no 11 to put of the led at the output.

- Fault, in this case, means that input B will always have a stack at 0 because this digit will never change.

- Error is the deviated output result generates by the gate due to the defect in the gate. Note, the error in the NAND gate is not permanent. The reason is that we will have the correct output as 1 whenever we have 00 or 10 as inputs patterns.

- Failure, in this case, is when the NAND gate is not performing as expected.

New technologies bring new defects and must be modelled into faults. According to [17], the presence of fault *F* in a circuit *C* transforms the *C* into a new faulty circuit  $C^F$ . Let y(x) be the logic function of a circuit *C* with perfect functionality. The presence of fault in *C* y(x), changes the circuit and its function to  $C^F y^F(x)$ . However, if a system functionality does not change in the present of faults, we call it redundant faults.

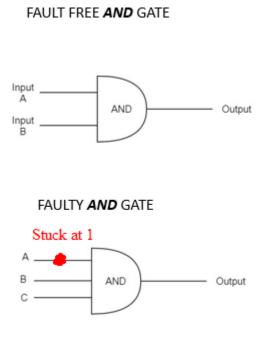

This raises the question of how do we address such faults? A combinational circuit that contains undetectable SAF is said to be redundant [24], [26]. Therefore, a redundant fault could be addressed by removing the unnecessary inputs that cause its occurrence. Let examine this statement with an AND gate of n inputs and n+1 input respectively, where the extra input is redundant and remain always constant. This is depicted in *Figure.4*.

#### AND GATE TRUTH TABLE

| Input A | Input B | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 0      |

| 1       | 0       | 0      |

| 1       | 1       | 1      |

REDUNDANT AND GATE TRUTH TABLE

| A | в | с | Output |

|---|---|---|--------|

| 1 | 0 | 0 | 0      |

| 1 | 0 | 1 | 0      |

| 1 | 1 | 0 | 0      |

| 1 | 1 | 1 | 1      |

Figure 4: Comparison of Fault free and Redundant Faulty gate

In the second table, the presence of the redundant input does not change the result of an AND gate. Hence, the two tables justify the correct output of an AND gate even in the presence of redundant inputs. Therefore, removing the redundant gate input of the faulty AND gate removes the redundancy.

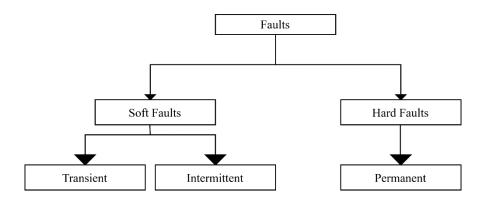

#### **2.3.2 Classification of faults**

A fault can be classified into two types, soft and hard faults. A fault is mostly caused by a defect, this defect could be either shorts, open, improper manufacture, induced by thermal ageing or by environmental influences.

Figure 5: classification of faults

- Transient fault occurs randomly and remains active for a short period. This can be difficult to detect unless the result is seen at the propagation output as incorrect.

- Intermittent fault occurs at irregular intervals due to aging or unexpected environmental factors.

- Permanent faults are always active and will only disappear after the system has been repaired.

## 2.4 Fault models

A fault model is used for fault simulation, analysis and evaluation of the set of test vectors.

Depending on the level at which systems are handled fault models could be different and this type of inconsistency increase CAD system costs as there would be the need for tools available for each level explicitly considered. According to [27], the systems various levels of abstractions need different mathematical tools for each level. Defects must be modelled at the higher abstracted level as faults. Consequently, the main goal of the fault model is to reduce the infinite set of possible defect behaviours into a finite set of faults [24].

## 2.4.1 Stuck-at-faults

The most widely use fault model in digital testing is the single stack at fault model [26]. However, its limitations lie in its capability to model only a single fault. The characteristics of this model are given below:

- Only one circuit line is faulty

- Faulty line is permanently set to 0 or 1

- The fault can be at the input or output of a gate.

For the testing of processor, High-level fault model is adopted in this thesis.

### 2.5 Fault simulation

The ideal of fault simulation is nothing than simulating a digital circuit in the presence of fault [28]. The formula for fault coverage is given below.

$Fault coverage = \frac{Number of detected faults}{Total number of faults}$

Hence, a fault model is required in order to evaluate the fault coverage of the simulated circuit.

# 2.6 Levels of Abstraction in Digital System Testing

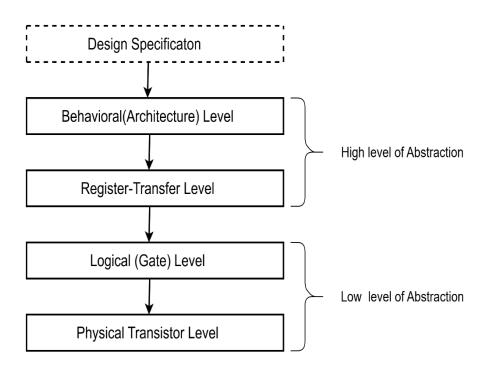

The modern technology advances are imposing new challenges on digital system testing with billions of transistors in a system which can operate at gigahertz frequencies [4]. Hence, design for testability must be considered during the design process, as the key to successful testing lies in the design process. Thus, the level of abstraction is used to manage the design process of the complex digital system [22]. It shows the design stage that should be implemented before the next. A high-level of abstraction focuses on most imperative data like the behavioural specification implementation. Figure 2.4 shows different levels of abstraction.

Figure 6: Level of Abstraction [29]

Before moving to test part let us briefly explain the level of abstraction.

The design specification is the requirements to follow for the design flow. One can say it is the plan for the system execution.

The behavioural level is the highest level of abstraction that describes the system in term of what it does or how it behaves. Hence, the behavioural level is the interpretation of the specification as a computer program.

An example is a circuit that warns car passenger when the door is open, or the seatbelt is not used [29].

As shown in *figure 6* the RTL with structural information only exist once the behavioural level is implemented. The RTL is synthesis to gate-level design in which sequential and combinational logics are represented in the form of interconnects of logic gates such as AND gate, OR gate, XOR gate etc [29], [14].

Finally, the gate-level design is synthesized to the physical level where the gates are represented by interconnections of transistors [14], [29].

Both the logic and physical level are represented as the structural level. The structural level describes a system as a collection of gates or components that are essential for the performance of the system.

The gate-level is the most common level of abstraction through which testing has been targeted. On the other hand, due to the high numbers of gates for the digital system, testing at gate level remains a bottleneck. However, for testing accuracy in VLSI, the physical layer has been targeted because of the direct contact to the layout and routing information of the manufactured system [14], [29].

However, testing a digital system such as the processor requires a very high level of abstraction. Therefore, this work, we will be focusing on testing at a high-level of abstraction.

# 2.7 Importance of Digital System Testing

The reliability of a digital system is enhanced through testing. Thus, testing could detect design errors, fabrication errors, fabrication defects and physical failures such as wearout and environmental factors before the system goes to the operational use. An early test for fault detection before releasing to the operational environment reduces the cost of test, on the other hand, the cost of finding defects after the system has been released for operational use can be overwhelming. Therefore, quality and economy are two vital factors to be considered [5]. Failure cannot be tolerated in such a system since digital systems are widely used in safety-critical systems.

## **3** State-of-the-Art for testing processor

The approaches in the field of processor test can be organized into three major groups [17], [3]: structural, functional and software-based self-test methods. The structural approach is based on applying DFT techniques into a digital design. Hence, this process can change the design implementation of the system under test. Therefore, it is not safe for testing a safety-critical system like a processor.

The functional approach is used for testing chip after manufacturing. However, the functional automatic tester is expensive. Due to high cost of the functional approach, the industry raised interest in the structural approach which on the other hand is not efficient due to over-testing.

The current state-of-the-art is based on testing the processor using the gate-level information for SAF. However, the complexity of today's processor that uses billions of transistors requires more high-level method in testing the processor rather than via gate-level. Due to this reason, a method that gives less overhead in a test budget was proposed by the semiconductor industry that can be incorporated in an established processor test flow [4]. This method is referred to as software-based self-test as mentioned in the background section.

Because of the growing density of integration in the semiconductor industry today's chips are more sensitive to faults while the faults detection mechanisms of the latter become more complex [2]. The complexity of processors, and the limited accessibility of the internal logic, makes them very difficult to test [12], [19], [30], [13]. According to [31], the larger amount of logic for processor is based on the order of hundreds of thousands of gates which makes it very difficult to test using the classical approach of testing digital circuits. Hence, it is not enough to use the existing fault simulation and test generation software to derive tests for processors. One easy approach of solving this problem is to use pseudorandom test patterns [12], but its drawback is the lengthy test result which therefore remains impractical to test complex microprocessors [4]. However, some previous work in testing a complex microprocessor was based on functional models [5], [32], [4], [13], [11], [33], and has shown some method of success also it opens paths for the improvement of test generation for a complex microprocessor.

The result of the test generation method proposed in [34] by Saucier and Robach was not successful due to the results not directly observable. The reason is because of the unavailability of the basic control commands to the user which are necessary during the control state and its operands are not directly available to the functional units (like ALU, etc) of the microprocessor.

In [32] two different fault modules were considered in testing the bit-sliced microprocessor. The methods were based on the combinational and sequential separation of the microprocessor into modules. They altered changes in the truth table for the combinational module and in the state table for the sequential module. Based on these fault model they generate tests to verify the correct functioning of each component modules. The problem in [32] is that the approach tests only the data part and assume that the control part of the MP is fault-free. Also, it would be inefficient to generate tests when the modules are complex.

In [5] a microprocessor is represented by a set of functions such as 1) data transfer path,2) data manipulation functions, 3) register decoding, 4) instruction sequencing.

A functional fault model is then developed for each of these functions, tests are generated as to detect faults in the fault model although the generated test was only able to test correctly the relatively simple functions except the instruction sequencing. The test generation for the instruction sequencing fails because the fault model was not based on the logical analysis of the instruction execution. However, in order to test correctly the instruction sequencing, each instruction is executed, and a test is generated to check for the correct execution of the instruction without any other instruction being executed simultaneously.

The problem in [5] was partly solved in [31], where the researchers created a fault model that treated the presence of faults in each instruction individually. Thus, their result detects some faults not covered in [5], i.e. the instruction sequencing faults and the complexity of their test generation is only  $O(n_I * n_R + n_R^4)$ .

It was proposed in [35] and [10] that the processor can be divided into module under test to ease test data generation using ATPG. ATPG is one of the means of generating test data for SBST [36]. However, the drawback of using ATPG is the run-time for generating

the test data for microprocessor testing [11]. In addition to the drawback, the traditional ATPGs target only single SAF.

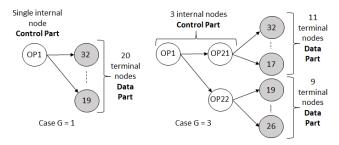

In [13] a novel high-level implementation-independent test generation that covers high multiple SAF and fault simulation that evaluates the high-level fault coverage was proposed. The method is based on separate test generation for the control parts and data parts of the MP at high-level functional units. The control parts are tested with a highlevel control fault model, whereas, they applied a pseudo-exhaustive test for the data parts. The application of the pseudo-exhaustive test to the data part is to keep the implementation-independent property of the proposed method. The approach in [13] can be used for easy identification of redundant gate-level faults in the control parts. Remind that, redundancy occurs when the function of gate or circuits does not change in the presence of a fault. Hence, a combinational circuit that contains undetectable SAF is said to be redundant [24], [26]. The novelties of the method which are based on 1) modelling the UUT by symbolic EDNF and 2) the translation of the traditional fault propagating task ... to achieve full independence of the implementation details in test generation prove to be effective and cover multiple faults in high-level than the well-known traditional ATPGs. However, the drawback of this approach is based on the high numbers of patterns that the method uses for the test generation, which in returns increase computational time but on the other hands aid the fault coverage capability. Thus, optimization is needed.

In [4], [33], [37] a novel high-level functional control fault model was used to cover the high-level and gate-level faults of the MP. The functional fault model support hierarchical test approach, where the test pattern, which activates a low level fault at low level (gate-level), can be consider as the high-level constraint for the functional fault defined at the higher-level (functional or behavioural) [13], [38]. The mentioned functional fault models offer high flexibility in defect modelling beyond single SAF model [38]. The major problem of these approaches is the not sufficient fault coverage achieved when comparing with the gate level faults coverage approach. Perhaps, this is caused by the level of quality of the test data used in test program for testing the microprocessor.

In [2] extension to the class of functional faults model was proposed for the modules of RISC type MP. The goal of this approach is to cover large functional faults together with a large class of structural faults while using a high-level fault model. That is, the fault model implemented without the knowledge of the MP gate-level implementation details.

The research in [2] proves that the functional fault model could as well cover gate-level faults without using the gate-level implementation details.

This approach has a common implementation strategy with the already mentioned method in [32]. However, here both control and data parts were tested without assumptions in the correct functioning of any of its parts. Their method put together the structural faults and functional faults classes as a single measurable high-level functional fault model. Thus, High-Level-Decision Diagram was used for formalization of the high-level test generation. This method of testing enhanced fast testing period and reduce test cost. In *Table 2* experimental result for this approach gives high SAF coverage compared with other implementation-independent and the state-of-the-art approaches for testing microprocessor.

However, this approach has less coverage for the "Forward unit" (see table 2) of the MUT in compare with the ATIG that uses implementation detail. A drop-in fault coverage is one of the major challenges while covering low-level faults using high-level fault model.

### 3.1 Summary of state-of-the-art

Since the traditional low-level test methods for a complex system like MP has lost their importance, due to the complexity of today's sub-micron technologies, other approaches test methods based on the high level functional and behavioural method are gaining more popularity [39] [40]. Hierarchical mixed or multi-level approaches have also been used both for test generation and fault simulation [41] [42] [43].

These varieties of approaches have been used by researchers in order to improve fault coverages during SBST of processor. However, none have been able to generate high fault coverages for the gate level faults tested at high-level of abstraction (i.e. using functional fault model).

Many researchers target both the structural and functional approaches. The structural approaches make use of the processor lower-level details for test generation, whereas functional approaches use the processor high-level details [6].

To increase the speed of test generation, High-level fault model has been chosen, but this approach can be considered as "good" if the test generated using this model provide high SAF coverage or physical defect [4] [38].

In an attempt to improve these method, researchers in [33] have proposed different approaches in testing the MP at high-level, a good example is a proposed novel high-level implementation-independent of test program generation method for RISC processors in [13]. The high-level model of the processor is derived from the instruction set and its architectural features. The experimental result in [13] [33] gave high fault coverage for the given MP without the information about the gate-level implementation details. However, the experiment used high numbers of patterns for test data generation.

Thus, this thesis focuses on test data optimization. The instruction set architecture of the MP is used and a comprehensive functional fault model was developed. The approach is based on topological reasoning of the special SSBDDs that generalize to HLDDs. Hence, HLDD is generated automatically using the instruction set of the MP in order to improve the test data generation, which in return improve the faults coverage for both the high and low-level.

Experimental result obtained in this thesis is compared with the one proposed in [33] which has already been compared with other 3 methods from the state-of-the-art:

| Module/unit | #faults | Gate-level implementation<br>details exploited |        | Gate level implementation<br>independent |                  |  |

|-------------|---------|------------------------------------------------|--------|------------------------------------------|------------------|--|

|             |         | ATIG                                           | SBST   | SBST                                     | Proposed in [33] |  |

| ALU         | 203576  | 98.67%                                         | n.a    | 97.85%                                   | 99.06%           |  |

| PPS_EX      | 21136   | 97.62%                                         | 96.20% | 84.12%                                   | 97.96%           |  |

| Forward     | 3738    | 99.00%                                         | 99.68% | 93.64%                                   | 98.03%           |  |

## **4 High Level Decision Diagrams**

This chapter presents the approaches in the fault model procedure for the SBST to test a given processor (miniMIPS). The usefulness of Decision Diagram and its functionality in the field of SBST is shown. The process for test program generation through the concept of HLDD is analysed. It also, presents the ISA of the given MP and how the HLDD is synthesized for the given MP based on the ISA. The partitioning approach in this work is an optimized version and different from the work done in [2], [4], [13], [37], as a result of the algorithmic partitioning of processor instructions on HLDD for test data generation. Hence, the test program for SBST is generated via the synthesized HLDD.

Thus, the following sections explore the fundamental use of DDs, history of DDs, the transition reason from BDDs to HLDDs, the fault modelling method adopted in this work for test generation, the benefit of the HLDDs as fault model foundation for complex systems and in *chapter 5.4*, I present the algorithm for generating the HLDDs developed during the research of this work.

### **4.1 Overview of Decision Diagrams**

In today's digital system gate-level test generation methods is obsolete as the complexity of the digital systems continue to increase [19], [4], [44], [24], [45], [6]. Promising approaches are high-level, or hierarchical methods that use functional descriptions of a system [24].

Due, to different system level of abstraction, there are no unique models as a uniform approach to generates test at a different level. However, DD has been choosing to serve as a base for uniform test generation, fault simulation and fault location for mixed-level representations of systems and the Boolean algebra as its plain logic level [24], [1]. Therefore, DD serves as manager of hierarchy in diagnostic modelling. Different types of DDs have been adopted and used for testing, such as the BDD, SSBDD and the generalize HLDD that handle the test generation problem at high-level.

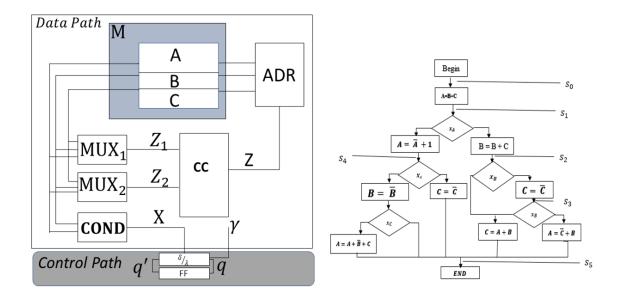

Thus, when the DDs is used for describing the complexity of the digital system, we have to represent the system by a proper set of interconnected components (combinational or sequential sub-circuits) [43]. Then, the components by their corresponding functions which can be represented by DDs [46].

In summary, DDs are used for multi-level and hierarchical diagnostic modelling because of their uniform cover of different levels of abstraction, and because of their capability for uniform graph-based fault analysis and diagnostic reasoning [3], [43], [47], [48]. This means that instructions and faults can be modelled at gate-level, RTL and behaviour level using DD.

Hence, DD can be categorised into two major parts.

- 1) Logic level (BDD)

- 2) Behavioural high-level DD (HLDD)

This work focuses on modelling the MP at the behavioural level using the HLDD.

### 4.1.1 History of Decision Diagram

BDDs have become the state-of-the-art data structure in very-large-scale integration computer-aided design for representation and manipulation of Boolean functions [49], [50].

In 1959, C.Y. Lee introduced a method for representing digital circuits by binary decision programs [51].

The same model was introduced but with a different name as alternative graphs for test generation purposes in 1976 by R. Ubar, [1].

Bryant proposed ROBDDs as a new data structure [43] in 1986.

In [28], [48], [27], [52] SSBDDs was introduced as a special class of BDDs to represent the topology of the gate-level circuit in terms of signal paths. The advantage of SSBDD based approach is that the library of component is not needed for structural path activation and as clearly explained in [24] the, SSBDD based test generation procedures do not depend on whether the circuit is represented on the gate level or the whole circuit. It is a novel fact that the SBDD test generation procedures can be easily generalized for the high-level DDs to handle digital systems represented at higher levels [27], [53], [54].

### **4.2 HLDD**

The most important impact of the HLDD is the possibility of generalization and extension of the methods for test generation, fault simulation and diagnoses [2], [52].

In order to use HLDD to describe complex systems, the system must be partitioned into a suitable set of interconnected components (combinational or sequential sub-circuits) [17]. HLDDs model allows mapping the control functions of systems into non-terminal nodes, and the data manipulation functions into terminal nodes [17].

The non-terminal nodes of the HLDDs represent the control variables [19], [4], [17]. Both terminal and non-terminal nodes of the HLDDs should be tested [10], [55], [24], [37]. We verify the behaviour of the circuit by testing the non-terminal nodes of an HLDD, on the other hand, we verify the working mode of a circuit, when testing the terminal nodes of an HLDD [37], [56].

The main purpose of modelling fault at high-level is to speed up fault coverage evaluation without reasoning about the gate-level implementation details [57] and the main idea of this kind of fault modelling is to obtain from the high-level (functional or behavioural) description of the system an incorrect version by introducing a fault into the description, [37], [24], [57], [26]. This approach is also referred to as **model perturbation** [24].

The traditional gate-level approach has lost their importance since the physical defects that may occur in digital systems often do not manifest themselves as stuck at fault [58]. Hence, high-level faults represent the effect of a physical defect on the system functionality. Therefore, to improve the test quality, there is a need to replace the traditional fault models like SAF with a realistic defect model [58]. That is, the defect model that can handle the defect orientation and the high-level behaviour of the system. Hence, HLDD in combination with a multi-level approach is the appropriate way of resolving this issue. It was proved in [13] and [26] that a high-level fault model can be explicit or implicit. An explicit model identifies each fault individually and every fault in the model is treated as a target for test generation [57], [26].

However, implicit fault identifies faults that belong to the same classes, sharing "similar" properties, so that all fault in the same class can be detected by the same procedure [13], [26], [57], [59].

In [13] different fault models have been developed for digital circuits as to detect its failure mechanisms like transistors stack-open [60], signal line bridges [61], or failure due to delays in circuit [22]. High-level fault model is widely used in the field of SBST

[11], [59] for test generation at high-level of abstraction without resorting to the implementation details of the gate-level.

Its drawback is its low fault coverage for gate-level faults. Thus, the research in SBST focuses on the drawback as to detect high gate-level fault coverage based on test generated from the high-level of abstraction while test data is less. On the other hand, the advantage of high-level fault model cannot be underestimated due to its independent character on the system implementation details. Thus, it can be used not to check physical faults of microprocessor only, but also as a verification tool with which we check whether the implementation is free of design errors [24].

In a general case beyond the Boolean algebra a decision diagram can be defined as a noncyclic directed graph:

### **Definition 4.1:**

$G = (M, \Gamma, X)$  with a set of nodes M, a set of variables X, and a relation  $\Gamma$  in M where  $\Gamma(m) \subseteq M$  denotes the set of successors of the node  $m \in M$  [17], [3], [27].

The nodes  $m \in M$  are labelled by variables  $x(m) \in X$  (constants or algebraic expressions of  $x \in X$ ). For each value e from a set of possible predefined values  $e \in V(x(m))$  of a non-terminal node variable x(m), there exists a corresponding output edge from the node m into a successor node  $m^e \in \Gamma(m)$  [3], [56].

Note, that the SSBDD model can be regarded as a special case of HLDD based on the above-given definition [48]. While the above definition is the *graphical representation of a system* using graph theory, the formal definition of HLDD regarding a system is given below.

#### **Definition 4.2**:

Considered S as a given digital system, consist of different components (subsystems), which is denoted by a function  $z = f(z_1, z_2, z_3, ..., z_n) = f(Z)$  where Z is the set of variables(can be Boolean, vectors or integers) and  $V(z_k)$  is the set of possible values for  $z_k \in Z$  which are finite [3], [14].

The cycle-based modelling concept for analysing the behaviour of a digital circuit is adopted by HLDD. This means that HLDD allows system state determination at a cycle. Thus, since the MP is been modelled at high-level using the ISA, the instruction cyclebased will be considered. However, the following presents the list of faults affecting the operation of MP.

### 4.2.1 List of Faults affecting the Operation of MP

Before, presenting the fault model approaches for this work. It is imperative to list the faults affecting the operation of MP. These faults can be divided into the following classes [24]:

- I. addressing faults affecting the register decoding function;

- II. addressing faults affecting the instruction decoding and instruction sequencing functions;

- III. faults in the data-storage function;

- IV. faults in the data-transfer function;

- V. faults in the data-manipulation function.

### 4.2.2 High-Level Fault Modelling for MP with HLDDs

Knowing which fault model is right to choose is the central problem of test generation in fault simulation. However, many approaches like fault tuple model [62] [3], pattern fault model [63] [3], input pattern fault model [64] [3], and functional fault model [65] have been shown and used by researchers. Thus, in order to generate high-quality test a good fault model should be adopted. Test generation needs high-level fault modelling because of its high complexity [19], [16], [4], [17]. The main and general problem of the fault model is the difficulty of proving that the model covers all the low-level detectable (non-redundant) faults [38]. In this thesis, attempt is made to prove that by generating a separate test for the control and data part of the MP, using high-level fault model.

According to [17], there are two opposite criteria [that] should be followed while developing tools for synthesis of tests:

- 1. Efficiency (the cost of test generation)

- 2. Quality of generated test (fault coverage).

These criteria are highly dependent on the type of fault model used during test generation and fault simulation for test quality ascension. Based on these obvious facts, a good fault model reflects the accurate physical mechanism of the real defect in a system its modelled for, which then support excellent test quality.

#### 4.2.3 Complexity and Accuracy in Fault Model

Complexity and accuracy are other issues that the HL fault model solved while reasoning about test generation at high and low-level with a trade-off in consideration. The multi-level approach should be considered as accuracy requires low-level fault models and fault simulation [33] . On the other hand, high-level fault model solves the issue of complexity in test generation for the CUT and gives high fault coverage. Although the representation of defect with high-level (less complex) fault model hasn't achieved high accuracy in test quality for the low-level fault coverage like the fault coverage by the traditional ATPGs.

However, due to the complexity of today's electronic system, modelling its defect with low-level fault models is obsolete. The continuous research in this area has exposed the trade-off for balancing the accuracy and complexity concepts. The result in *Table 2* above is a good comparison example, where three modules of MP are tested with and without the knowledge of its implementation details and the result from different researchers were tabled and compared.

Therefore, increasing the accuracy of representing defects also increases the complexity of the fault model [30] [17], [66]. Since the new process of semiconductor technology arises in today's digital world, knowledge of know-how will always be needed to understand the new type of defects that could cause a failure mechanism in today's and in future nanoelectronics.

Also, HLDDs support functional fault model where the system architecture is first described at the system level and the system is partitioned into several functional blocks or modules, whereas, structural fault model applies to gates, flip-flops and interconnection between them [17]. HLDD-based high-level fault model is well suitable to support the development of a uniform and straightforward high-level test generation and fault simulation algorithm [58], [3].

Other different high-level models have been presented in [5], [67], [68], but none of these techniques established the relationship between high-level fault coverage and gate-level fault coverage. Thus, these models were only able to contribute to test generation but are not suitable for the gate-level test quality assessments. However, the approach in this thesis is different from these previously mentioned as this work considered both the high-

level and low-level faults coverage while modelling with HLDDs. Hence, this work optimized the work in [2] and [33].

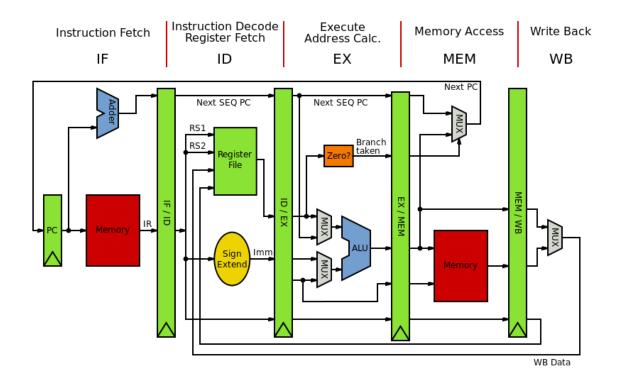

## 4.3 MiniMIPS ISA

The miniMIPS has a 32-bit core based on a von Neumann architecture, with a 5-stage pipeline, instruction extraction, instruction decoding, execution memory access and update registers [69]. The following table shows the full instructions of a miniMIPS processor used for the experiment in this thesis. The description includes flags, list of instructions, general purpose-register, assembly language syntax and their binary representation [7]. The ISA (*Table 3*) serves as an abstract representation of the microprocessor itself. High-level decision diagrams can be constructed from the instruction set architecture of an MP. Therefore, for testing the microprocessor we must test that the instructions are executing correctly. Twenty instructions are chosen for the experiment carried out in this thesis (Table 4).

Table 3: Full miniMIPS instruction set [14], [69].

## MiniMIPS Instruction Set Architecture

| S/N | Instruction | OP1                      | OP2         | Mnemonics             | ISA Level Operation                                     |

|-----|-------------|--------------------------|-------------|-----------------------|---------------------------------------------------------|

|     | ADD         | 000000 (0)               | 100000 (32) | ADD rd rs rt          | rd= rs + rt                                             |

|     | ADDI        | 001000 (8)               | 100000 (32) | ADDI rt rs I          | rt = rs + I                                             |

|     | ADDIU       | 001000 (8)               | -           | ADDIU rt rs I         | rt = rs + I<br>rt = rs + I                              |

| -   | ADDU        | 000000 (0                | 100001 (33) | ADDU rd rs rt         | rd = rs + rt                                            |

|     | ADDO        | 000000 (0)               | 100100 (36) | AND rd rs rt          | rd= rs AND rt                                           |

|     | ANDI        | 001100 (12)              | 100100 (30) | ADDI rt rs I          | rt= rs AND I                                            |

|     | BEQ         | 000100 (4)               | -           | BEQ rs rt offset      | If rs= rt then branch                                   |

|     | BGEZ        | . ,                      | 00001 (1)   | BGEZ rs offset        | If $rs \ge 0$ then branch                               |

|     | BGEZAL      | 000001 (1)<br>000001 (1) | 10001 (17)  | BGEZAL rs offset      |                                                         |

|     | BGEZAL      |                          | 10001 (17)  | BGEZAL IS Offset      | If $rs \ge 0$ then procedure<br>If $rs > 0$ then branch |

|     |             | 000111 (7)               | -           |                       |                                                         |

|     | BLEZ        | 000110 (6)               | -           | BLEZ rs offset        | If rs <=0 then branch                                   |

|     | BLTZ        | 000001 (1)               | 00000 (0)   | BLTZ rs offset        | If $rs < 0$ then branch                                 |

|     | BLTZAL      | 000001 (1)               | 10000 (16)  | BLTZAL rs offset      | If rs < 0 then procedure                                |

|     | BNE         | 000101 (5)               | -           | BNE rs offset         | If rs != rt then branch                                 |

| 15  | J           | 000010 (2)               | -           | J Target              | rd= return_address                                      |

| 16  | JALR        | 000000 (0)               | 001001 (9)  | JALR rs               | rd = return_address                                     |

|     |             |                          |             | JALR rd rs            |                                                         |

| 17  |             | 000000 (0)               | 001000 (8)  | JR rs                 | PC = rs                                                 |

|     | LUI         | 001111 (15)              | -           | LUI rt I              | rt = I                                                  |

|     | LW          | 100011 (35)              | -           | LW rt offset (base)   | rt = memory [base + offset]                             |

| 20  | MFHI        | 000000 (0)               | 010000 (16) | MFHI rd               | rd= HI                                                  |

| 21  | MFLO        | 000000 (0)               | 010010 (18) | MFLO rd               | rd= LO                                                  |

| 22  | MTHI        | 000000 (0                | 010001 (17) | MTHI rs               | HI = rs                                                 |

| 23  | MTLO        | 000000 (0)               | 010011 (19) | MTLO rs               | LO = rs                                                 |

| 24  | MULT        | 000000 (0)               | 011000 (24) | MULT rs rt            | [LO, HI] = rs X rt                                      |

| 25  | MULTU       | 000000 (0)               | 011001 (25) | MULTU rs rt           | [LO, HI] = rs X rt                                      |

| 26  | NOR         | 000000 (0)               | 100111 (39) | NOR rd rs rt          | rd= rs NOR rt                                           |

| 27  | OR          | 000000 (0)               | 100101 (37) | OR rd rs rt           | rd= rs OR rt                                            |

| 28  | ORI         | 001101 (13)              | -           | ORI rt rs I           | rt = rs OR I                                            |

| 29  | SLL         | 000000 (0)               | 000000 (0)  | SLL rd rt sa          | $rd = rt \ll sa$                                        |

| 30  | SLLV        | 000000 (0)               | 000100 (4)  | SLLV rd rt rs         | $rd = rt \ll rs$                                        |

| 31  | SLT         | 000000 (0)               | 101010 (42) | SLT rd rs rt          | rd = rs < rt                                            |

| 32  | SLTI        | 001010 (10)              | -           | SLTI rt rs I          | rt = rs < I                                             |

| 33  | SLTIU       | 001011 (11)              | -           | SLTIU rt rs I         | rt = rs < I                                             |

|     | SLTU        | 000000 (0)               | 101011 (43) | SLTU rd rs rt         | rd = rs < rt                                            |

| 35  | SRA         | 000000 (0)               | 000011 (3)  | SRA rd rt sa          | rd = rt >> sa                                           |

| 36  | SRAV        | 000000 (0)               | 000111 (7)  | SRAV rd rt rs         | rd = rt >> rs                                           |

| 37  | SRL         | 000000 (0)               | 000010 (2)  | SRL rd rt sa          | rd = rt >> sa                                           |

| 38  | SRLV        | 000000 (0)               | 000110 (6)  | SRLV rd rt rs         | rd = rt >>rs                                            |

| 39  | SUB         | 000000 (0)               | 100010 (34) | SUB rd rs rt          | rd= rs - rt                                             |

| 40  | SUBU        | 000000 (0)               | 100011 (35) | SUBU rd rs rt         | rd= rs - rt                                             |

| 41  | SW          | 101011 (43)              | -           | SW rt offset(base)    | Memory[base + offset]=rt                                |

| 42  | SYSCALL     | 000000 (0)               | 001100 (12) | SYSCALL               | System call                                             |

| 43  | XOR         | 000000 (0)               | 100110 (38) | XOR rd rs rt          | rd= rs XOR rt                                           |

| 44  | XORI        | 001110 (14)              |             | XORI rt rs I          | rt = rs XOR I                                           |

| 45  | JAL         | 000011(3)                |             | JAL target            | rd=return_address                                       |

| 46  | LWCO        | 110000                   | -           | LWCO cs, offset(base) | cs=memory[base + offset]                                |

| 47  | MFCO        | 10000                    | 0           | MFCO rt, cs           | rt = cs                                                 |

| 48  | MTCO        | 10000                    | 100         | MTCO rt, cs           | cs = rt                                                 |

The following table shows the set of instructions from the list of miniMIPS instructions partitioned for testing the processor in this thesis.

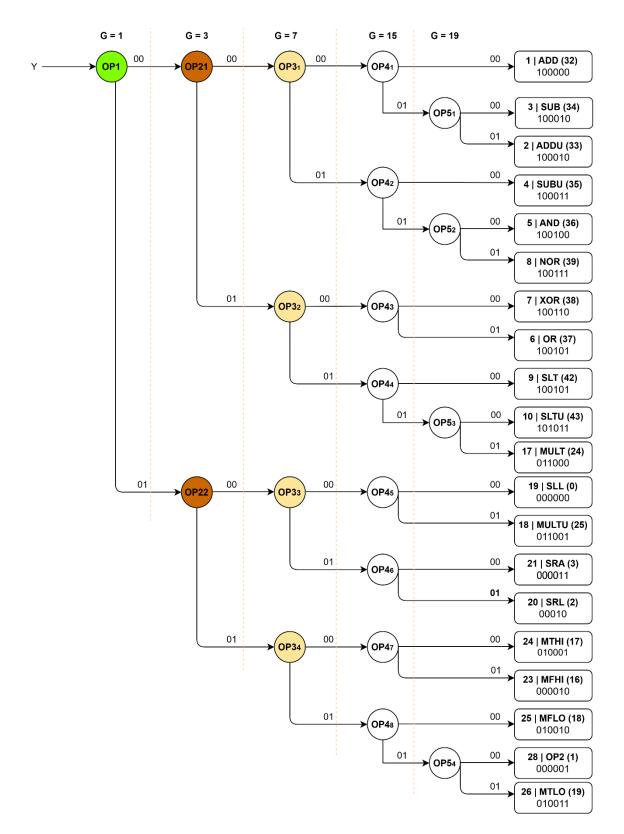

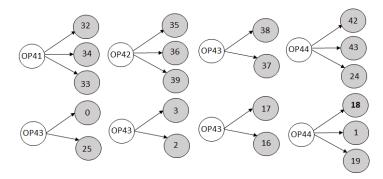

## 4.4 HLDD Generation for MP

Consider the behavioural level structure of a microprocessor in *Figure*. 7, and the HLDD in *Figure*. 8 generated as the source of functional fault model for the MP with a set of instructions in *Table 4*.

Note, the HLDD generation has been optimised in order to achieve high test data generation for SBST. The optimization is based on the logic behind the position of the terminal node and the connection between each function while less test data is used during the test. Hence, the ordering is referred to as "good". Chapter 5 of this thesis will present the test generation approach in detail. However, this section serves as the foundation for the test generation.

| Number | Instruction | Code        |

|--------|-------------|-------------|

| 19     | SLL         | 000000 = 0  |

| 28     | OP2         | 000001 = 1  |

| 24     | MFLO        | 010010 = 18 |

| 26     | MTLO        | 010011= 19  |

| 17     | MULT        | 011000 = 24 |

| 18     | MULTU       | 011001 = 25 |

| 2      | ADDU        | 100001 = 33 |

| 3      | SUB         | 100010 = 34 |

| 1      | ADD         | 100000 = 32 |

| 4      | SUBU        | 100011=35   |

| 5      | AND         | 100100 = 36 |

| 6      | OR          | 100101 = 37 |

| 7      | XOR         | 100110 = 38 |

| 8      | NOR         | 100111 = 39 |

| 9      | SLT         | 101010 = 42 |

| 10     | SLTU        | 101011= 43  |

| 20     | SRL         | 000010 = 2  |

| 21     | SRA         | 000011 = 3  |

| 23     | MFHI        | 010000 = 16 |

| 25     | MTHI        | 010001= 17  |

Table 4: Instructions selected for Experiment

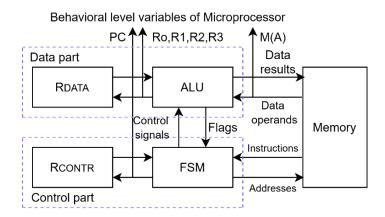

Figure 7: Behavioural Level Structure of the Microprocessor [4]

Consider MP functionality as a set of the following behavioural level functions [4], [14]:

- R<sub>i</sub> = f<sub>i</sub>(I,S(R<sub>i</sub>)) = f<sub>i</sub>(OP, B,S(R<sub>i</sub>) where R<sub>i</sub> ∈ R<sub>DATA</sub>, i=0,1,2,3, ... 19, and S(R<sub>i</sub>) = { R<sub>DATA</sub>, , M(A)} is a set of data arguments for the functions f<sub>i</sub> (a set of the source registers over all the instructions);

- 2) PC =  $f_{pc}$  (*I*, *C*, *PC*) =  $f_i$  (*OP*, *B*, *PC*) where *C* is the flag variable serving as a condition for the branch operation;

- 3)  $M(A) = f_M(I, S(M(A))) = f_i(OP, B, S(M(A)))$  where  $S(M(A)) = \{R_{DATA}, M(A)\}$

The functionality of the MP can now be represented by a set of behavioural level variables  $Z = R_{DATA} \cup R_{CONTR} \cup M(A)$  and by a set of functions  $F = \{f_0, f_1, f_2, f_3, ..., f_{19}, f_{PC}, f_M\}$  [17], [4], [14]. In this work, we are testing the data path and the control path of the MP. Which means we will model the behavioural level variables  $Z = R_{DATA} \cup R_{CONTR}$  and a set of functions  $F = \{f_0, f_1, f_2, f_3, ..., f_{19}\}$ . The behaviour of MP can be modelled by the functional basis F and monitored through the variables Z. For modelling of F the behavioural level HLDD model is used [4].

The following HLDD is automatically generated, by the algorithm developed for HLDD generation in this work. The algorithm is discussed in *section 5.4*.

Figure 8:Generated HLDD for a subset of instructions of MP with 19 decision nodes.

In this thesis, I have developed a program to generate the HLDD which reduces the complexity of the processor for test generation. This type of approach is different from

the manual approach adopted before. Thus, an approach to test data optimization for high fault coverage.

The generation of the HLDD for the selected instruction set allows calculating both the high – and low-level fault coverages. A fault of the nodes causes an incorrect leaving the path activated by a test [24].

The behaviour of the system is described in a specific working mode by each path of the HLDD [17] [3] Each of the non-terminal nodes can be referred to as a superposition(subsystem) of the entire HLDD. The following definition gives a functional meaning of the HLDD graphical representation of a system.

#### **Definition 4.3** [3],[17], [70]:

A DD which represents a digital function z = f(Z) is a directed acyclic graph  $G_z = (M, \Gamma, X)$ , where the set of nodes  $M = M^N \cup M^T$  is partitioned into the subsets of nonterminal nodes  $M^N$  and terminal nodes  $M^T$ , and the set of variables  $X = C \cup D$  is partitioned into the subsets of control variables C (e.g. instruction variables and data variables D (operands). A terminal node  $m_T \in M_T = \{m_{T,0}, m_{T,1}\}$  is labelled by a constant  $e \in \{0,1\}$  and is called a *leaf*, while all the non-terminal nodes  $m \in M_N$  are labelled by variables nodes  $x \in X$  and have successors whose number may be  $2 \leq$  $|\Gamma(m)| \leq |V(x(m))|$ . Let us denote the associated with node m variable as x(m),