**Digital Test in WEB-Based Environment**

EERO IVASK

Faculty of Information Technology Department of Computer Engineering Chair of Computer Engineering and Diagnostics TALLINN UNIVERSITY OF TECHNOLOGY

Dissertation was accepted for the defence of the degree of Doctor of Philosophy in Engineering at Tallinn University of Technology on June 19, 2006.

The commencement of the thesis will take place on July 5, 2006 in Tallinn University of Technology, Ehitajate tee 5, Tallinn, Estonia

Supervisor:

Prof. Raimund Ubar, D.Sc., Academician Department of Computer Engineering, Tallinn University of Technology

**Opponents:**

Helena Krupnova, Ph.D. HPC Functional Verification Group STMicroelectronics, Grenoble, France

Prof. Dr.-Ing. Günter Elst Head of Branch Lab EAS Fraunhofer Institute for Integrated Circuits, Dresden, Germany

Declaration:

Hereby, I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology has not been submitted before for any degree or examination at any other university.

Copyright Eero Ivask 2006

ISSN 06 ISBN 55666 To my family

# Abstract

Current thesis presents an Internet based collaborative framework for digital testing using genetic algorithms for test generation software modules. Genetic algorithms are proposed in order to overcome complexity of the test generation problem for modern digital integrated circuits. Issues of hierarchical fault simulation and defect oriented fault simulation for test quality analysis are discussed as simulation is critical issue in genetic test generation. Digital test design flow begins with behavioral level VHDL description. Suitable flow chart like input format is extracted from source VHDL and fed into academical high-level synthesis tool xTractor. Subsequently generation of decision diagram models for test generation tools follows.

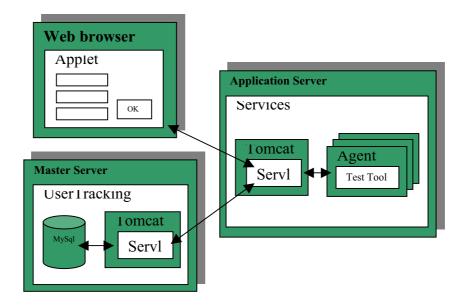

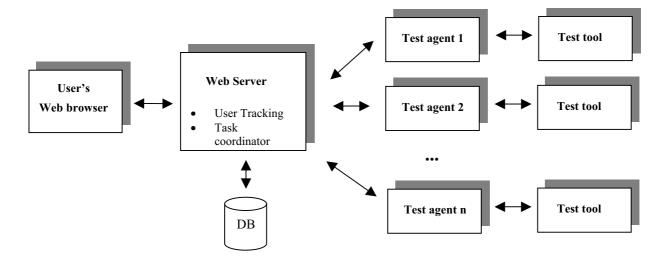

Current thesis also addresses issues of collaborative design and test. Universal state-of-the-art collaborative platform MOSCITO is described and possibilities of its use for digital design and test flow are analyzed and suitable strategies for workflow integration with existing test tools are proposed. In addition, necessary enhancements are proposed in order to use the MOSCITO system in firewall-protected environments. Finally, based on earlier studies and experience, the new completely http protocol based environment for remote tool usage is proposed. New platform has three-tier architecture using mostly Java applets as front-end, servlets on Tomcat as middleware and MySql as physical back end database server.

# Kokkuvõte

Doktoritöö raames on välja pakutud mitu geneetilisel algoritmil põhinevat testigenereerimise meetodit kombinatsioon- ja järjestikskeemide testimiseks. Vastavad realiseeritud tarkvaramoodulid on mõeldud kasutatamiseks ka allpool mainitud internetipõhises keskkonnas. Geneetilised algoritmid on testigenereerimise probleemi lahendamisel valitud selleks, et ületada skeemide testimisel tekkivat NP keerukat lahendi otsimise probleemi, et vähendada otsinguruumi. Käsitletud on ka hierarhilise ja defekt-orienteeritud rikete simuleerimise meetodeid, kuna geneetilise testigenereerimise algoritmi juures mängib rikete simuleerimine olulist rolli- testigeneraatori poolt pakutud testikomplekte tuleb adekvaatselt hinnata igal iteratiivsel sammul. Digitaalseadme testimine võib alata n. käitumusliku taseme VHDL keelsest kirjeldusest. Doktoritöö raames koostatud kompilaatori abiga ekstraheeritakse VHDL lähtekoodist oluline informatsioon ja teisendatakse voodiagrammi sarnasele kujule, mis edasi leiab kasutust akadeemilises kõrgtasemesünteesi süsteemis xTractor. Viimase väljundist on võimalik genereerida omakorda otsustusdiagramide mudelid kasutamiseks n. eelpoolmainitud testitarkvaraga. Testimine võib alata muidugi ka madalamalt, nn. loogikalülide tasemelt, kui vastav skeem olemas on.

Käesolevas doktoritöös on välja töötatud ka internetipõhine virtuaalne keskkond kasutamiseks digitaalseadmete testimise valdkonnas. Keskkond on vajalik selleks, et olemasolevaid, seni ainult lokaalselt installeeritavaid tarkvaraprogramme üle interneti kasutada. Esmalt sai VILAB projekti raames välja töötatud moodus lokaalsete programmide distantskasutamiseks rakendades tarkvasasüsteemi MOSCITO võimalusi. Välja sai pakutud lahendus süsteemi kasutamiseks interneti tulemüüride olemasolu tingimustes ning sai teostatud hulgaliselt testeksperimente, sealhulgas ka tööstusliku disainiga. Kuna MOSCITO süsteemi võimalused on siiski piiratud, sai lõpuks välja pakutud uus, täiuslikum http protokolli põhine e. veebibrauseriga kasutatav kaugtöö keskond digitaalseadmete testi jaoks. Uuel süsteemil on kolmekihiline arhitektuur. Graafilise kasutajaliidesena kasutatakse Java applette, keskmises kihis kasutatakse Tomcat tarkvara ja servlette, andmebaasi serverina on kasutatud vabatarkvara MySQL.

# Acknowledgements

First I would like to thank my supervisor Prof. Raimund Ubar for drawing my attention to testing field, to science, for possibility to do interesting work in his research group, which generally has opened new horizons to me. Thanks for support and valuable guidance in decisive moments.

I would like to thank Margus Kruus, our director of Computer Engineering department for his general administrative support and valuable encouragement towards this thesis.

Many thanks to Prof. Emeritus Leo Võhandu for introducing me to evolutionary algorithms and other innovative techniques in his seminars.

Thanks a lot for inspiring atmosphere and good cooperation and remarks to all colleagues in our research lab, especially to Jaan, Marina, Artur, Elmet, Marek and Peeter.

I am truly grateful to all EAS IIS colleagues and staff in Dresden for wonderful time I have spent there – thanks for all support and hospitality, thanks for providing excellent research conditions and everything. My special thanks to Andre Schneider for his kind attention and fruitful cooperation.

Last, but not least, I would like to thank my family- without you this work would not make sense at all.

# **Table of Contents**

| 1 | INT   | RODUCTION                                                              | 1  |

|---|-------|------------------------------------------------------------------------|----|

| 2 | REV   | /IEW OF STATE-OF-THE-ART                                               | 3  |

|   | 2.1   | TEST OF DIGITAL SYSTEMS                                                | 3  |

|   | 2.2   | WEB-BASED DIGITAL DESIGN                                               |    |

|   | 2.3   | DISCUSSION                                                             |    |

|   |       |                                                                        |    |

| 3 |       | T GENERATION FOR DIGITAL SYSTEMS WITH GENETIC                          |    |

| A | LGOR  | ITHMS                                                                  | 11 |

|   | 3.1   | OVERVIEW OF GENETIC ALGORITHMS                                         | 11 |

|   | 3.1.1 | Representation                                                         | 12 |

|   | 3.1.2 | •                                                                      |    |

|   | 3.1.3 | <i>Fitness function</i>                                                | 12 |

|   | 3.1.4 |                                                                        |    |

|   | 3.1.5 |                                                                        |    |

|   | 3.1.0 | 6 Reproduction                                                         | 13 |

|   | 3.1.2 | 7 Selection                                                            | 13 |

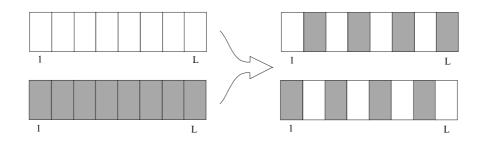

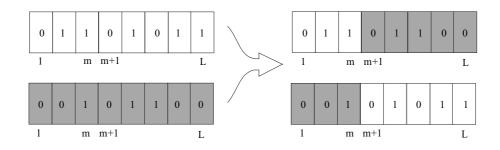

|   | 3.1.8 | 8 Crossover                                                            | 16 |

|   | 3.1.9 | 0 Mutation                                                             | 17 |

|   | 3.1.1 | <i>Parameters for genetic algorithm</i>                                | 17 |

|   | 3.2   | HOW GENETIC ALGORITHMS WORK                                            | 18 |

|   | 3.2.1 | Exploration engine: important similarities                             | 18 |

|   | 3.2.2 | 2 Schema concept                                                       | 19 |

|   | 3.2.3 | S Schema theorem                                                       | 20 |

|   | 3.2.4 | 1 Implicit parallelism                                                 | 25 |

|   | 3.2.5 | 5 Building block hypothesis                                            | 25 |

|   | 3.2.0 | 6 Conclusions                                                          | 26 |

|   | 3.3   | GENETIC ALGORITHM FOR COMBINATIONAL CIRCUIT TESTING                    | 27 |

|   | 3.3.1 | Introduction                                                           | 27 |

|   | 3.3.2 | P Fault model                                                          | 27 |

|   | 3.3.3 | 8 Representation                                                       | 28 |

|   | 3.3.4 | Initialization                                                         | 28 |

|   | 3.3.5 | $\mathcal{J}$                                                          |    |

|   | 3.3.0 | 8                                                                      |    |

|   | 3.3.7 | 5                                                                      |    |

|   | 3.3.8 |                                                                        |    |

|   | 3.3.9 |                                                                        |    |

|   | 3.3.1 | 8 5                                                                    |    |

|   | 3.3.1 | 0 0                                                                    |    |

|   | 3.3.1 | 1                                                                      |    |

|   | 3.3.1 |                                                                        |    |

|   | 3.4   | $Genetic \ \text{algorithm for Finite State Machine testing} \ \ldots$ |    |

|   | 3.4.1 |                                                                        |    |

|   | 3.4.2 | J J J                                                                  |    |

|   | 3.4.3 | B Decision Diagrams for FSM                                            | 38 |

| 3.4.4                                               | Fault classes                                                                                                                                                                                                     |    |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.4.5                                               | Limitations                                                                                                                                                                                                       |    |

| 3.4.6                                               | Test sequence                                                                                                                                                                                                     |    |

| 3.4.7                                               | Problems in FSM testing                                                                                                                                                                                           |    |

| 3.4.8                                               | Representation for genetic algorithm                                                                                                                                                                              | 41 |

| 3.4.9                                               | Initialization                                                                                                                                                                                                    |    |

| 3.4.10                                              | Evaluating test sequences                                                                                                                                                                                         |    |

| 3.4.11                                              | Dynamically increasing test sequence length                                                                                                                                                                       |    |

| 3.4.12                                              | Self-adaptive mutation rate                                                                                                                                                                                       |    |

| 3.4.13                                              | Fault sampling                                                                                                                                                                                                    |    |

| 3.4.14                                              | Selection                                                                                                                                                                                                         |    |

| 3.4.15                                              | Crossover                                                                                                                                                                                                         |    |

| 3.4.16                                              | Mutation                                                                                                                                                                                                          |    |

| 3.4.17                                              | Description of algorithm                                                                                                                                                                                          |    |

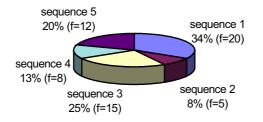

| 3.4.18                                              | Experimental results                                                                                                                                                                                              |    |

| 3.4.19                                              | Conclusion                                                                                                                                                                                                        |    |

|                                                     | ULT ORIENTED GENETIC TEST GENERATION FOR SEQUENTIAL CIRCUITS                                                                                                                                                      |    |

| 3.5.1                                               | Representation                                                                                                                                                                                                    |    |

| 3.5.2                                               | Initialization                                                                                                                                                                                                    |    |

| 3.5.3                                               | Evaluation of test vectors                                                                                                                                                                                        |    |

| 3.5.4                                               | Fitness                                                                                                                                                                                                           |    |

| 3.5.5                                               | Selection of candidate sequences                                                                                                                                                                                  |    |

| 3.5.6                                               | Crossover                                                                                                                                                                                                         |    |

| 3.5.7                                               | Mutation                                                                                                                                                                                                          |    |

| 3.5.8                                               | Working algorithm                                                                                                                                                                                                 |    |

| 3.5.9                                               | Experimental Results                                                                                                                                                                                              |    |

|                                                     | SCUSSION                                                                                                                                                                                                          |    |

| _                                                   | 50055101                                                                                                                                                                                                          |    |

| 4 FAULT                                             | Γ SIMULATION IN DIGITAL SYSTEMS                                                                                                                                                                                   | 57 |

| 4.1 TE                                              | ST COVER CALCULATION IN DIGITAL SYSTEMS WITH MULTI-LEVEL DECISIO                                                                                                                                                  | N  |

|                                                     |                                                                                                                                                                                                                   |    |

| 4.1.1                                               | High Level Decision Diagrams                                                                                                                                                                                      |    |

| 4.1.2                                               | Low-Level Decision Diagrams                                                                                                                                                                                       |    |

| 4.1.3                                               | Hierarchical fault simulation                                                                                                                                                                                     |    |

| 4.1.4                                               | Experimental results                                                                                                                                                                                              |    |

|                                                     | EFECT ORIENTED MIXED-LEVEL FAULT SIMULATION IN DIGITAL SYSTEMS                                                                                                                                                    |    |

| 4.2.1                                               | Mapping Defects onto the Logical Level                                                                                                                                                                            |    |

| 4.2.2                                               | Defect Oriented Hierarchical Fault Simulation                                                                                                                                                                     |    |

| 4.2.3                                               | Defect Oriented Fault Simulation on Decision Diagrams                                                                                                                                                             |    |

| 4.2.3                                               | Experimental results                                                                                                                                                                                              |    |

|                                                     |                                                                                                                                                                                                                   |    |

| 13 DI                                               | 1                                                                                                                                                                                                                 |    |

| 4.3 DI                                              | SCUSSION                                                                                                                                                                                                          |    |

| _                                                   | 1                                                                                                                                                                                                                 | 73 |

| <b>5 DESIG</b><br>5.1 GE                            | SCUSSION<br>N FLOW WITH TEST TOOLS<br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION                                                                                                                 |    |

| <b>5 DESIG</b><br>5.1 GE<br>5.1.1                   | SCUSSION<br><b>N FLOW WITH TEST TOOLS</b><br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION<br>Supported VHDL constructs                                                                             |    |

| <b>5 DESIG</b><br>5.1 GE<br>5.1.1<br>5.1.2          | SCUSSION<br>N FLOW WITH TEST TOOLS<br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION                                                                                                                 |    |

| <b>5 DESIG</b><br>5.1 GE<br>5.1.1<br>5.1.2<br>5.1.3 | SCUSSION<br><b>N FLOW WITH TEST TOOLS</b><br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION<br>Supported VHDL constructs                                                                             |    |

| <b>5 DESIG</b><br>5.1 GE<br>5.1.1<br>5.1.2          | SCUSSION<br><b>PN FLOW WITH TEST TOOLS</b><br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION<br>Supported VHDL constructs<br>Mapping VHDL onto IRSYD<br>Control flow extraction<br>HLS tool xTractor |    |

| <b>5 DESIG</b><br>5.1 GE<br>5.1.1<br>5.1.2<br>5.1.3 | SCUSSION<br>N FLOW WITH TEST TOOLS<br>ENERATING DATA FOR HIGH-LEVEL SYNTHESIS AND TEST GENERATION<br>Supported VHDL constructs<br>Mapping VHDL onto IRSYD<br>Control flow extraction                              |    |

|       | DIGITAL DESIGN FLOW WITH AUTOMATED TEST GENERATION        |    |

|-------|-----------------------------------------------------------|----|

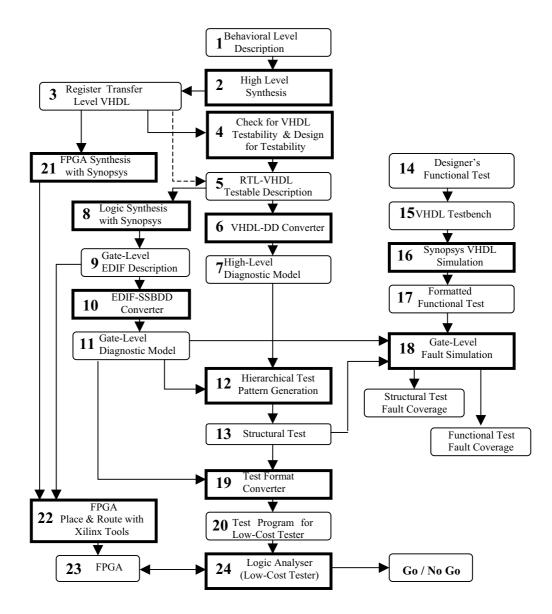

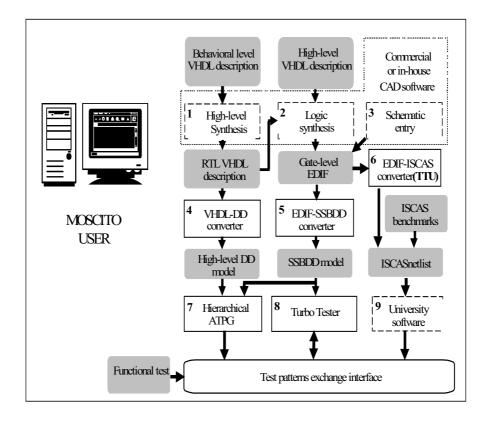

| 5.2.1 | Test generation flow with ATPG                            | 85 |

| 5.2.2 | 5 V                                                       |    |

| 5.2.3 |                                                           |    |

| 5.3   | DISCUSSION                                                |    |

| 6 WEB | B-BASED ENVIRONMENT FOR DIGITAL DESIGN AND TEST           |    |

| 6.1   | INTERNET-BASED COLLABORATIVE DESIGN AND TEST WITH MOSCITO |    |

| 6.1.1 | Overview of MOSCITO                                       |    |

| 6.1.2 | Software architecture                                     |    |

| 6.1.3 | Tool encapsulation                                        |    |

| 6.1.4 | Communication                                             |    |

| 6.1.5 | General concept                                           |    |

| 6.1.6 | Graphical User Interface                                  |    |

| 6.1.7 | Internet-based usage                                      |    |

| 6.1.8 | Enhancements: working with firewall protection            |    |

| 6.1.9 | Integrating test tools into the MOSCITO environment       |    |

| 6.2   | ENHANCED WEB-BASED ENVIRONMENT                            |    |

| 6.2.1 | Motivation                                                |    |

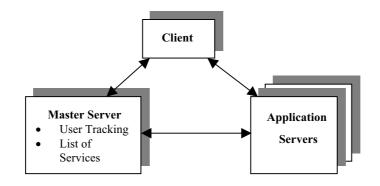

| 6.2.2 | General concept                                           |    |

| 6.2.3 |                                                           |    |

| 6.2.4 | Usage scenario                                            |    |

| 6.2.5 |                                                           |    |

| 6.2.6 | Communication                                             |    |

| 6.2.7 |                                                           |    |

| 6.2.8 |                                                           |    |

| 6.2.9 |                                                           |    |

| 6.3   | DISCUSSION                                                |    |

| 7 SUM | IMARY                                                     |    |

# List of publications

- 1. E.Ivask, J.Raik, R.Ubar. Comparison of Genetic and Random Techniques for Test Pattern Generation. *Proc. Of the 6<sup>th</sup> Baltic Electronics Conference*, Oct. 7-9, 1998, Tallinn, pp. 163-166.

- 2. G.Elst, K-H.Diener, E.Ivask, J.Raik, R.Ubar. FPGA Design Flow with Automated Test Generation. *Proc. Of German 11<sup>th</sup> Workshop on Test Technology and Reliability of Circuits and Systems.* Potsdam, 1999, pp. 120-123.

- E.Ivask, J.Raik, R.Ubar. Fault Oriented Test Pattern Generation for Sequential Circuits Using Genetic Algorithms. IEEE European Test Workshop, Cascais, Portugal, Mai 23-26, 2000, pp. 319-320.

- E.Ivask, J.Raik, R.Ubar. Fault Oriented Test Pattern Generator for Sequential Circuits Using Genetic Algorithms. 7<sup>th</sup> Baltic Electronics Conference, Tallinn, October 8-11, 2000, pp.129-132.

- 5. K.-H.Diener, G.Elst, E.Ivask, G.Jervan, Z.Peng, J.Raik, R.Ubar. Digital Design Flow with Test Activities. VILAB User Forum, Smolenice, April 8, 2000, 11 p.

- E.Ivask, R.Ubar, J.Raik, A.Schneider. Internet Based Test Generation and Fault Simulation. Design and Diagnostics of Electronic Circuits and Systems – DDECS'2001, Györ, Hungary, April 18-20, 2001, pp.57-60.

- A.Schneider, E.Ivask, J.Raik, P.Miklos, K.H. Diener, R.Ubar, W.Kuzmicz, W. Pleskacz, E. Gramatova. VILAB Test Generation Tools Running Under the MOSCITO System. VILAB User Forum Györ, Hungary, April 18-20, 2001, 12 p.

- R.Ubar, J.Raik, E.Ivask, M.Brik. Hierarchical Fault Simulation in Digital Systems. Proceedings of Int. Symp. On Signals, Circuits and Systems SCS'2001, Iasi, Romania, July 10-11, 2001, pp.181-184.

- A.Schneider, E.Ivask, P.Mikloš, J.Raik, K.H.Diener, R.Ubar, T.Cibáková, E.Gramatová. Internet-based Collaborative Test Generation with MOSCITO. IEEE Proc. Of Design Automation and Test in Europe – DATE'02. Paris, March 4-8, 2002, pp. 221-226.

- A.Schneider, K.-H.Diener, E.Ivask, R.Ubar, E.Gramatova, T.Hollstein, W.Pleskacz, W.Kuzmicz, Z.Peng. Integrated Design and Test Generation Under Internet Based Environment MOSCITO. EUROMICRO Conference, September 3-6, 2002, pp. 187-194.

- A.Schneider, K.-H.Diener, E.Ivask, R.Ubar, E.Gramatova, M.Fisherova, W.Pleskacz, W.Kuzmicz. Defect-Oriented Test Generation and Fault Simulation in the Environment of MOSCITO. Proceedings, BEC-2002, Tallinn, October 6-9, 2002, pp.303-306.

- 12. A.Schneider, K.-H.Diener, G.Elst, E.Ivask, J.Raik, R.Ubar. Internet-Based Testability-Driven Test Generation in the Virtual Environment MOSCITO. Proc. IFIP Conference on IP Based SOC Design, Grenoble, France, October 30-31, 2002, pp.357-362.

- R.Ubar, J.Raik, E.Ivask, M.Brik. Multi-Level Fault Simulation of Digital Systems on Decision Diagrams. IEEE Workshop on Electronic Design, Test and Applications – DELTA'02, Christchurch, New Zealand, 29-31 January 2002, pp.86-91.

- R.Ubar, J.Raik, E.Ivask, M.Brik. Mixed-Level Defect Simulation in Data-Paths of Digital Systems. 23<sup>rd</sup> Int. Conf. On Microelectronics. Nis, Yugoslavia, May 12-15 2002, Vol.2, pp.617-620.

- R.Ubar, J.Raik, E.Ivask, M.Brik. Defect-Oriented Mixed-Level Fault Simulation in Digital Systems. Facta Universitatis (Nis), Ser.: Elec. Energ. Vol.15, No.1, April 2002, pp.123-136.

- R.Ubar, J.Raik, E.Ivask, M.Brik. Test Cover Calculation in Digital Systems with Word-Level Decision Diagrams. Proc. Of the International Conference on Computer Dependability, Tomsk, Russia, September 10-13, 2002, pp.315-319. Invited paper.

- A.Schneider, K.-H.Diener, G.Elst, R.Ubar, E.Ivask, J.Raik. Integration of Digital Test Tools to the Internet-Based Environment MOSCITO. Proc. Of 7<sup>th</sup> World Multiconference on Systemics, Cybernetics and Informatics – SCI 2003. Orlando, USA, July 27-30, 2003, pp.136-141.

- M.Aarna, E.Ivask, A.Jutman, E.Orasson, J.Raik, R.Ubar, V.Vislogubov, H.D.Wuttke. Turbo Tester – Diagnostic Package for Research and Training. J. Of Radioelectronics and Informatics, No3 (24), July – September, 2003, pp. 69-73.

- M.Brik, J.Raik, R.Ubar, E.Ivask. GA-based Test Generation for Sequential Circuits. 2<sup>nd</sup> East-West Design & Test Workshop EWDTW-2004, Alushta 23-26, 2004, pp.30-34.

- M.Brik, E.Ivask, J.Raik, R.Ubar. On Using Genetic Algorithm for Test Generation. Proc. Of the 9<sup>th</sup> Biennial Baltic Electronics Conference, Oct. 3-6, 2004, Tallinn, pp.233-236.

- 21. E.Ivask, P.Ellervee. VHDL Front-End for High-Level Synthesis Tool xTractor. Proc. Of the 9<sup>th</sup> Biennial Baltic Electronics Conference, Oct. 3-6, 2004, Tallinn, pp.111-114.

- 22. E. Ivask, J. Raik, R. Ubar, A. Schneider. WEB-Based Environment: Remote Use of Digital Electronics Test Tools. In "Virtual Enterprises and Collaborative Networks", Kluwer Academic Publishers, 2004, pp. 435-442.

# List of Figures

| Figure 1 Pseudo c- code for proportional roulette wheel selection                  | . 14 |

|------------------------------------------------------------------------------------|------|

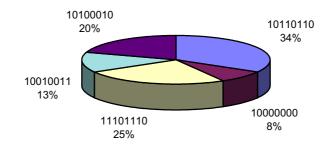

| Figure 2 Roulette wheel. Slots are proportional to individual's fitness            |      |

| Figure 3 Slot ranges corresponding to certain individuals                          |      |

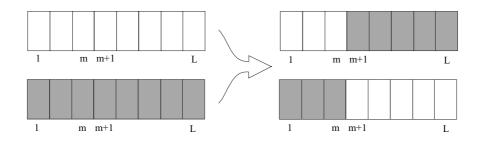

| Figure 4 One-point crossover                                                       |      |

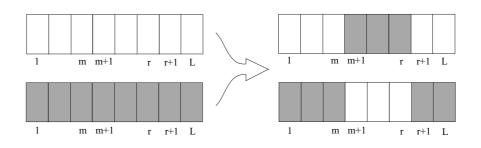

| Figure 5 Two-point crossover                                                       |      |

| Figure 6 Uniform crossover                                                         | 17   |

| Figure 7 Mutation in binary string                                                 | 17   |

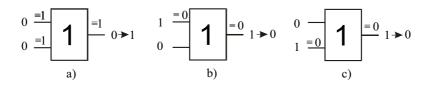

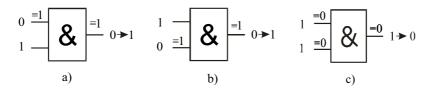

| Figure 8 Stuck-at-faults detected for OR gate                                      |      |

| Figure 9 Stuck-at- faults detected for AND gate                                    |      |

| Figure 10 One – point crossover                                                    |      |

| Figure 11 C code implementation of one-point crossover                             | . 31 |

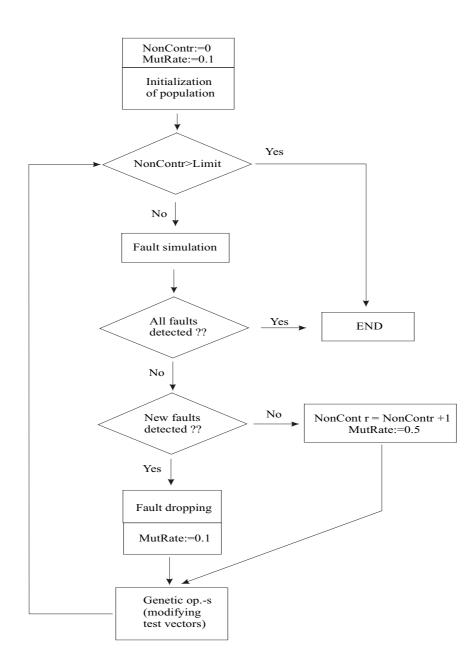

| Figure 12 Genetic test generation for combinational circuits                       | 33   |

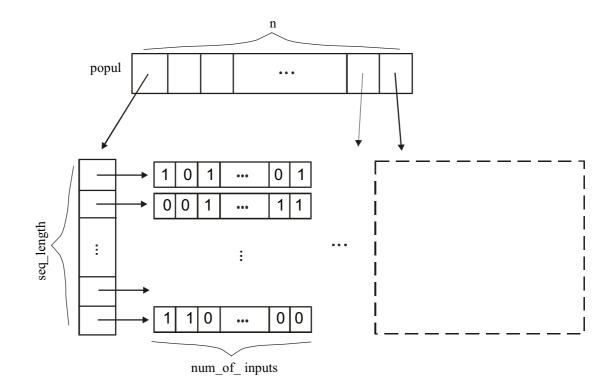

| Figure 13 Fault detection in time. Circuit c2670                                   | 34   |

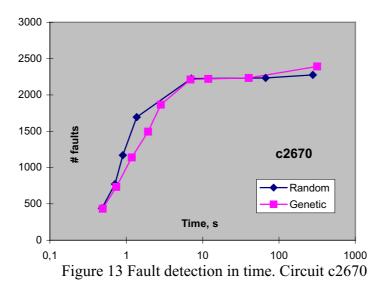

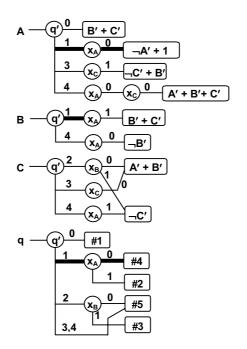

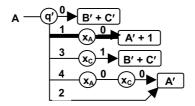

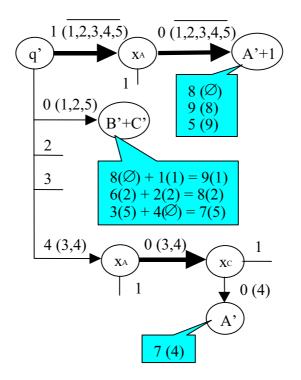

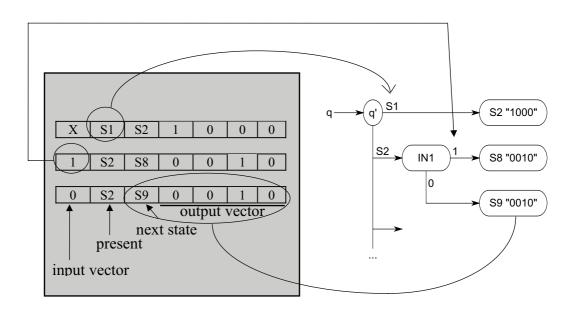

| Figure 14 STD and DD for benchmark circuit dk27                                    | 39   |

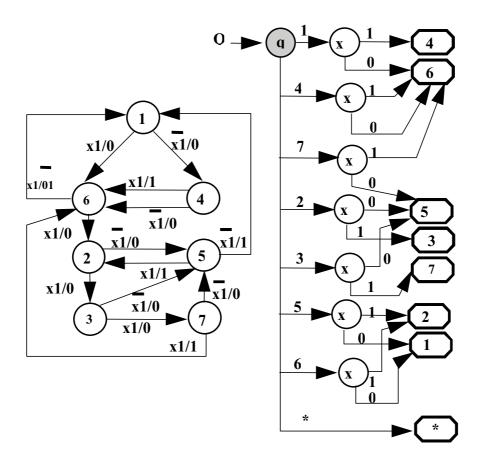

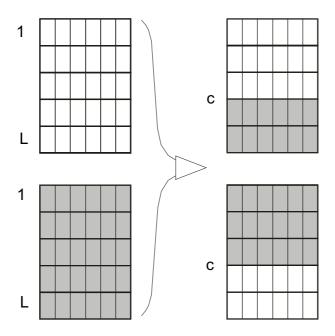

| Figure 15 Memory structure of population                                           |      |

| Figure 16 Crossover of vector sequences                                            | 45   |

| Figure 17 One-point crossover producing two children                               | 46   |

| Figure 18 Roulette wheel selection                                                 |      |

| Figure 19. Vertical one point crossover                                            | . 52 |

| Figure 20. Mutation in test vector.                                                | . 52 |

| Figure 21 A digital system and its behavior                                        | . 59 |

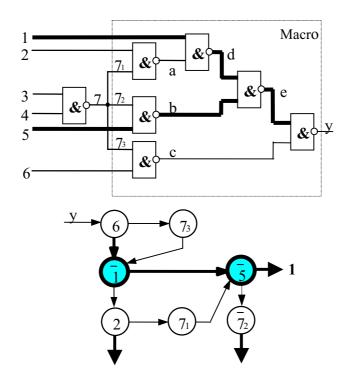

| Figure 22 High Level Decision Diagrams for the system in Figure 21                 | . 60 |

| Figure 23 Low-level decision diagram for a circuit                                 | . 61 |

| Figure 24 Hierarchical simulation of faults                                        | . 62 |

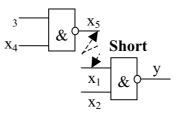

| Figure 25 A short between two signal leads                                         | . 66 |

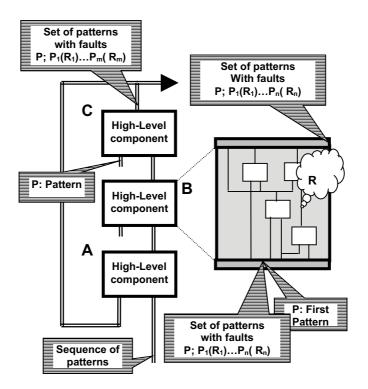

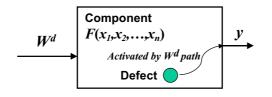

| Figure 26 Functional fault model for a physical defect                             | . 67 |

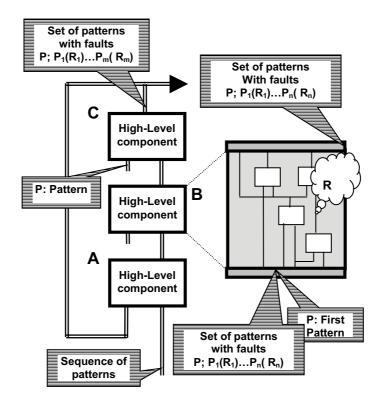

| Figure 27 Hierarchical fault modeling in a digital system                          | . 68 |

| Figure 28 DD for the subcircuit of A in the system in Figure 21                    | . 70 |

| Figure 29 Fault simulation on the graph $G_A$ on Figure 28                         | . 71 |

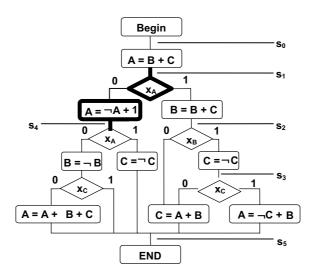

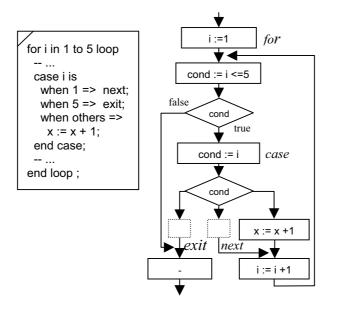

| Figure 30 Control flow mapping example                                             | . 75 |

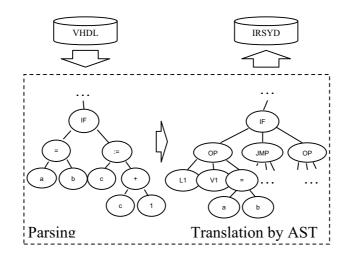

| Figure 31 Compilation flow                                                         | . 78 |

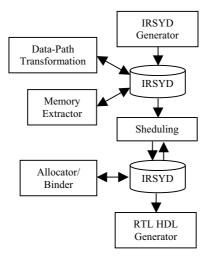

| Figure 32 xTractor synthesis flow                                                  |      |

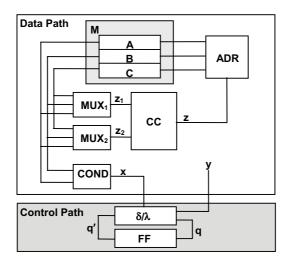

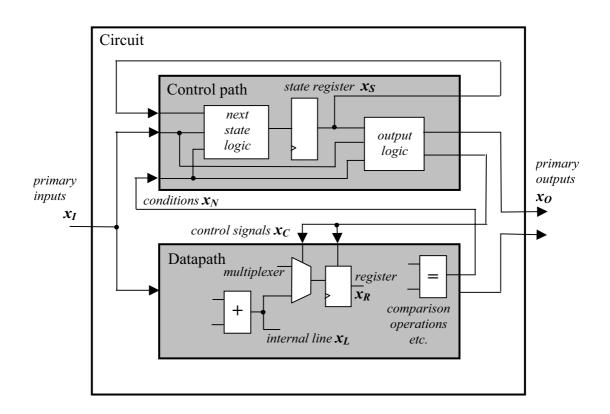

| Figure 33 Register-transfer level view of a digital circuit                        | . 81 |

| Figure 34 Example of FSM description in VHDL                                       |      |

| Figure 35 DD generation from the FSM State Transition Table                        |      |

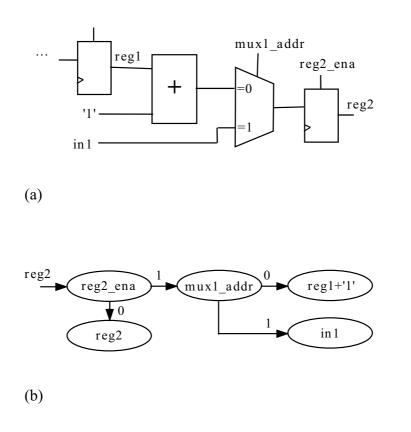

| Figure 36 A data path fragment (a) and its DD representation (b)                   |      |

| Figure 37 Test generation flow                                                     |      |

| Figure 38 The combined FPGA Design and Test Flow                                   |      |

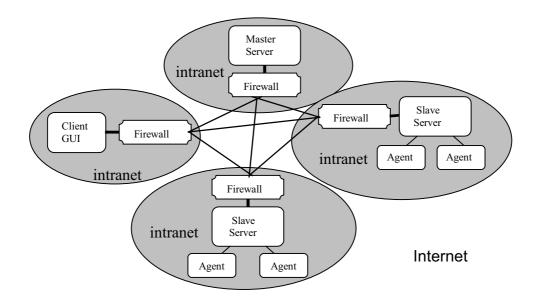

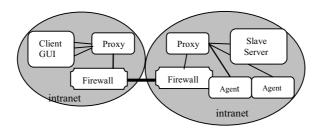

| Figure 39 Communication between firewall protected MOSCITO subsystems: connections |      |

| are allowed only between dedicated communication ports                             |      |

| Figure 40 Communication between client and agents via proxy                        |      |

| Figure 41 Work flows integrated to the MOSCITO environment                         |      |

| Figure 42 General concept of WEB based system                                      |      |

| Figure 43 Implementation details                                                   |      |

| Figure 44 General Web-based grid computing concept                                 | 100  |

# List of Tables

| Table 1 Hypothetical population and its fitness                             | 14 |

|-----------------------------------------------------------------------------|----|

| Table 2 Randomly selected numbers and corresponding individuals             | 15 |

| Table 3 Black box output maximization, inputs and fitness.                  | 19 |

| Table 4 Results for genetic test pattern generator                          |    |

| Table 5 Results for random test pattern generator                           | 35 |

| Table 6 Results for genetic test pattern generator and comparison with CRIS | 35 |

| Table 7 Characteristics of sample circuits                                  |    |

| Table 8 Experimental results for genetic FSM test generation                |    |

| Table 9 Characteristics of the benchmark circuits                           |    |

| Table 10 Test generation results                                            | 54 |

| Table 11 High-level fault simulation efficiency                             |    |

| Table 12 Low-level fault simulation efficiency                              | 64 |

| Table 13 Benchmark circuits for hierarchical simulation                     | 64 |

| Table 14 Hierarchical fault simulation results                              | 64 |

| Table 15 Comparison of Defect and SAF simulation                            | 72 |

| Table 16 Mixed-level fault simulation results                               | 72 |

| Table 17 Synthesis results of OAM module                                    |    |

| Table 18 Test Generation Results of the ATPG                                |    |

|                                                                             |    |

# 1 Introduction

The increasing complexity of VLSI circuits and transition to Systems-on-Chip (SoC) or even Networks-on-Chip (NoC) paradigm has made test generation one of the most complicated and time-consuming problems in the domain of digital design. The more complex are getting electronics systems, the more important become problems of test and design for testability, as costs of verification and testing are getting the major component of design and manufacturing costs of a new product. This fact makes the research in the area of testing and diagnosis of integrated circuits (IC) a very important topic for both the industry and the academy.

Commercial CAD systems for VLSI design and test are both costly and do not provide a good variety of competing or complementary approaches to a given particular problem. They usually have a stiff workflow of standard integrated tools bound together and should be executed accordingly to a certain scenario. It may be not good for a designers and researcher whose goal is the search for new efficient solutions. In order to come up with innovative electronic systems in time and with competitive cost, lot of EDA problems should be solved: HW/SW co-design, high-level synthesis, testability evaluation, test pattern generation. During the last decade, many different low-cost tools running on PCs have been developed to fill this gap. They usually include the major basic tools needed for IC design: schematics capture, layout editors, simulators, and place and route tools. However, low-cost systems for solving a large class of tasks from the dependability and diagnostics area: test synthesis and analysis, fault diagnosis, testability analysis, built-in self-test (BIST), especially for research and educational purposes, are still missing. For this reason, a diagnostic software Turbo Tester [54] is being developed in Tallinn University of Technology. Genetic test tools presented in this thesis and belonging to Turbo Tester toolset contribute to solving digital test problems.

Turbo Tester toolset was long time just a set of command line tools. There was strong need for user friendly graphical interface and even more – the need to make the tools available over the internet to avoid the installation overhead, simplify the maintenance and finally, to offer the computational power of fast application servers to end users. Another issue generally is that usually all the needed design and test tools are not available at persons working site. Therefore, current thesis partially addresses the issue of remote use of existing work tools.

At the same time recent development trends show increasing use of various hardware description languages (HDL) among hardware designers because of the advantages they offer over traditional schematic techniques. The main advantage is the possibility to use the same description both to model the behavior and as a starting point for schematic synthesis. Another important feature of most of the HDL-s (e.g. VHDL) is the possibility to describe an algorithm at higher abstraction levels thus hiding target technology dependent hardware implementation details. The introduction of high-level synthesis (HLS), also known as behavioral synthesis, promised to automate the transformation of a design from system/behavioral level to register-transfer level as efficiently as the introduction of logic synthesis automated transformation from logic to physical level. Most of the HLS tools (methodologies) make use of HDL-s as the language of input and output data. Also fast and efficient hierarchical test generators need both high level (RTL) and low level (gate level) descriptions in order to work. Extracting high level information from VHDL for hierarchical test generator DECIDER and generating input for synthesis system xTractor has great

importance. Current thesis addresses the issue of extracting the suitable information from behavioral level VHDL description for synthesis tool xTractor and decision diagram synthesis.

In current thesis chapter 2 gives overview of previous work in the field of test generation and Internet based collaborative design and test. Chapter 3 concentrates on test generation using genetic algorithms. Chapter 4 describes simulation algorithms. In chapter 5 is explained how data is extracted from VHDL for high-level synthesis and test generation. Complete digital design and test flow is presented. In chapter 6 state-of-the-art collaboration platform MOSCITO is described and possibilities of its use for digital design and test flow and suitable workflow integration strategies for existing test tools are discussed. Finally, enhanced web based system using HTTP protocol and MySQL database is proposed.

# 2 Review of State-of-the-Art

# 2.1 Test of digital systems

Sequential circuit test generation using deterministic algorithms is highly complex and time consuming. Classical deterministic (topological) test generators like HITEC [1,2] attain high fault coverage and are able to find test sequences for "hard" faults. Each target fault must be activated and then propagated to a primary output. The activation state must be justified using reverse time processing. During test generation, the large number of backtracking must be handled. In order to decrease the number of faults to be modeled, fault simulation (fault dropping) is used. Nevertheless, test sets can be long. The major drawback of such generators is that they are too time consuming while working through search space.

Functional level test generators like [3,4] use functional description of a circuit and exploit functional fault model. Test generation time is reduced. However, estimating fault coverage at the functional level is difficult because the accuracy of functional fault models is unproven and gate level models better characterize physical faults. Functional test based on FSM is used in [5]. The limitation of such functional method is also that a fault does not increase the number of states of machine and therefore does not help distinguish correct and faulty behavior.

As a solution, hierarchical approaches [6,7] have been proposed which take advantage of high-level information during generating tests for gate level faults. While hierarchical test pattern generation still remains the fastest method for solving the problem, it is not applicable for designs that do not have an appropriate modularity or where the higher-level information is not known.

On the other hand, simulation-based techniques have proven their efficiency, being able to obtain high fault coverage using less time than classical topological Automatic Test Pattern Generation (ATPGs). Fault simulation based test generators have the advantage that they can be adapted to new fault models or different circuit descriptions with minimal effort by using a fault simulator suitable for the new fault model. The drawback of simulation-based test generators generally consists in that they do not identify undetectable faults due to absence of any deterministic test generation procedure. In addition, simulation based approaches are fast only for smaller circuit and become ineffective when number of primary inputs and sequential depth of the circuit increase. The first simulation-based test generators was proposed by Seshu and Freeman [8]. Since then, several simulation-based test generators have been developed ([9], etc.).

Simulation-based technique is also used by Genetic Algorithm (GA) based test generators. There are several GA based test generators now. Fitness functions were used to guide the GA in finding a test vector or sequence that maximizes given objectives for a single fault or group of faults. In GATEST [10] the fitness function is biased toward maximizing the number of faults detected and the number of fault-effects propagated to flip-flops; increasing the circuit activity is a major objective in CRIS [11] and GATTO [12]. Maximizing propagation of fault effects to flip-flops and increasing circuit activity were shown to increase the probability of

detecting faults at the primary outputs. Activity means the change of the logic values in different circuit points. It is assumed that the more the input vector causes the circuit activity, the more likely the fault effect is carried to primary outputs. Although the fault-detection probability improves, activating a hard fault and propagating fault-effects from flip-flops to a primary output remain difficult problems. Increasing circuit activity may be ineffective in activating a hard fault or propagating fault effects. DIGATE [13] tackles the problem of fault-effect propagation by intelligent use of distinguishing sequences. However, also here faults must be activated in order to apply that technique effectively.

## 2.2 Web-based digital design

Over the last years, with advancements in the networking technology, several solutions are worked out in order to ease the collaboration in digital design field, to share the software tools, reuse the IP blocks, etc. Subsequently most interesting ones are described, classified by use case.

#### **Collaboration support (groupware)**

The design of complex hard- and software systems is a collaborative task and is typically solved in a workgroup. Despite of the interest in the field of groupware (computer-supported cooperative work) it is still the case that few systems have been adopted for widespread use. It is especially true for widely dispersed, cross-organizational design teams where problems of heterogeneity in computing hardware and software environments inhibit the deployment of groupware. Research in groupware field focuses on developing new theories and technologies for coordination of groups of people who work together. Key issues are group awareness, multi-user interfaces, concurrency control, communication and coordination within the group, shared information space and support of a heterogeneous, open environment which integrates existing single-user applications.

Feature rich solution for collaboration support is proposed in [15]. Concept of shared workspace for asynchronous cooperation was developed based on the idea of a private workspace. The workspace of single person comprises his personal work context. Workspace is used to store and retrieve documents, which can be stored into different container objects, like folders, also work tools are accessed from this workspace. Additional information about the work process can be stored there, as well the notes and tools needed. Work processes in the group can be organized synchronously or asynchronously. In first case direct response to one's activities is estimated, in second case response is usually delayed. The shared workspace is the central access point for common data and information of the state of the work process. Support of asynchronous aspects is of greater interest in teleworking of small and big companies. Participants may access and exchange documents at any time and all workgroup members are aware of the overall work progress. Proposed system has autonomously managed shared workspace, which the members of the working group install and use for the organization and coordination of their tasks. It is possible to upload documents from local computer to shared workspace and process documents in the workspace. Different type of objects can be in the workspace: folders, documents, tables, graphics, and links to www pages. There is notification of activities. Ordinary web browser is required only. Standard client-server architectural model is used. CGI (Common Gateway Interface)

technique is used in order to extend the web server functionality. Unix and Windows NT are supported. Apache web server and Microsoft IIS web server is supported. There is multilanguage support for user interface. Members can set access rights to control the visibility of the information or operations what can be done by others. HTML pages show the information and are refreshed when activities (buttons pressed etc.) are carried out. System permanently registers events i.e. what is going on, offers some version management. System supports building communities of interest- knowledge co production, support. Communities gather and develop existing information on the web and collaborate in synchronous or asynchronous manner. Developing means structuring and organizing the information. Different roles and different access rights are necessary. Java based user interfaces and role concept, document locking mechanism, moderated workspaces were added to system finally.

Only major drawback of described system is use of old-fashioned CGI technique, which is slow. Interesting is that in final stadium Java based interfaces were introduced to system. This shows the tendency in favor of Java.

#### **IP Reuse Paradigm**

In paper [14] a virtual electronic component (Intellectual Property – IP) exchange infrastructure is presented, whose main components are: 1) XML based well structured IP catalog builder responsible for management and e-publishing IPs and 2) XML IP profiler extracting IP files from design directories, transferring files to the used site via IP distribution server. Both applications use Java servlets and have client-server architecture. XML files are used instead of database.

#### Remote tool usage

Paper [18] presents the concept of a distributed, web-based electronic design framework. System has client-server architecture with multiple tiers. Web server is serving client requests whilst acting as client to the tool servers. In the sample application of the framework, developed in Java, any of the servers can be based on Linux, MS Windows or Sun-SPARC server. The web server has been used to demonstrate the framework for on-line access to VAMS (a VHDL-AMS parser) and Avant!

The multi-user nature of such framework requires the web server to have some 'memory' of what actions users have already been undertaken so that it can prompt for the next stage. HTTP is by definition a stateless protocol and therefore maintains no such 'memory'. Session tracking API provided by Java language is used here. It makes use of the facilities available (allowed) in user's web browser, such as cookies, URL rewriting or hidden fields to maintain this session 'memory'. Simple Java servlet code was written to implement this session tracking. Web server is responsible to maintain a collection of these session objects, which are created while different users make requests allowing to store relevant information and maintain information about current state. Usage of Java session object is sufficient in case of simple system, otherwise real database backend offers much more flexibility and reliability.

The nature of the framework also requires that files (e.g. design netlists) can be uploaded from a user's computer to the web server for processing. The files can be streamed through Java

StreamReader classes in order to write out to the file system. This is job of second servlet. The two servlets form a system, which will uniquely record a user's identification when writing the uploaded files to the web server file system. A system can store data about when files were written and last accessed in order to allow the web server to recover in the event of the crash and delete expired files. The Java RMI (Remote Method Invocation) was used as the communication method between web server and the tool servers. RMI provides a programming method that allows code development as if the remote Java classes are resident locally. This level of transparency is clearly excellent. For example, on the web server side it will look like as if the work tools reside on the web server itself. However, it is necessary to register the remote Java services with a Java RMI registry on the remote machine. When connection is made to a TCP socket, the correct service can be invoked to handle the connection. Java RMI is very elegant solution for distributed network programming indeed, only it has drawback that in presence of firefalls such solution will need opening additional communication ports and configuring firewall rules. Most probably, this will fail in case of big corporate firewalls with strict security policy.

Graphical user interface is here Java based. Java provides a number of built-in classes that enable graphics programming. These are the abstract window toolkit AWT and the swing class that provides a number of reusable graphics components. A simple method of graphing data in Java is available, and indeed this should not be overlooked as a method to visualize numerical data.

Simple name/password authentication provided by the HTTP protocol – called basic authentication was used in order to restrict access to preset domains within a web server. With this technique, the web server maintains a database of usernames and passwords and identifies certain resources as protected. When a user requests access to a protected resource, the server responds with a request for the client's username and password. At this point, the browser usually pops up a dialog box where the user enters the information. Basic authentication is very weak. It provides no confidentiality, no integrity, and only the most basic authentication. The problem is that passwords are transmitted over the network, thinly disguised by a well known and easily reversed Base64 encoding. Great amount of web server configuration is needed by simple authentication. Custom authentication technique, to which up-to-date security techniques may easily be applied, has been chosen for this application. This is a method where a servlet handles the access restriction, governing which servlets may then be accessed.

Paper [17] presents approach for dynamic and secure resource integration and administration, i.e., TRMS (Tool Registration and Management Services). TRMS allows the dynamic discovery of a tool using semantics descriptions of the desired tool behavior. A tool is described by a set of significant properties based on which it can be discovered in the network. Variant of that approach based on SNMP (Simple Network Management Protocol), which is a widely accepted standard for general network administration was presented. The implementation gives the context for an illustrating example in the area of a realistic PCB design flow based on the Zuken Hot-Stage tool suite. Presented approach was intended for intranet only.

Paper [19] uses web services as means to integrate remote tools in a workflow-driven design process for embedded systems. It is of course questionable if "providing a service" may offer

a greater market-potential than "supplying a tool". Problem is that design environments must be highly cooperative.

On the one side, definition and implementation on object level is still the adequate design style for tightly coupled components, on the other side when targeting Internet scenarios the concept of interacting services is now the state-of-the-art specification method. This servicebased programming paradigm is backed by new Internet protocols and languages like SOAP [21] and WSDL [22], which serve exactly the purpose of defining and describing services and their intercommunications. New applications or services can rely on services from other service-providers. Since the client of a service is not defined at the time the service is provided the deployment and publication are a most important part during its life cycle. With UDDI [23], a "dictionary" with a standardized access mechanism has been defined to alleviate this problem. This progress affects the traditional tool-centered engineering domains as well, since issues like time-to-market and distributed development and design are common factors in the affected processes. Moreover, the sophistication of tools gains a new level as the design technology for new products evolves rapidly. Therefore, they are valuable assets for a company forming an important part of their intellectual property (IP). Using the servicecentered approach, such companies have the chance to offer using their knowledge without having to externalize programs or algorithms. For the user of such services one important question is how to integrate such a service into their work environment. Usually integration focuses on the principle of coupling existing applications or components tightly together to ensure smooth and reliable operation. The resulting (and available) integration environments therefore use proprietary integration mechanisms on top of existing base-technologies like CORBA [20], JAVA [24], and JAVABEANS [25] or similar middleware components. In fact, CORBA-Services for instance constitute conceptually the same idea as web services with WSDL: to enable their use through a common interface by different applications. The important difference of this approach is that web services are build on top of a foundation that is centered on the Internet platform. Which means the common denominator for running such services is standard web server technology, TCP/IP networks and the HTTP protocol accompanied by the flexible XML meta-format.

With web services there is no firewall traversal problem, however there will be problem with consuming these services. Question is about the granularity of the service pieces. Fine grain services are interesting for system integrators mainly. Average chip designer who wants to get a specific task done, will obviously not benefit from that. He needs complete tool not pieces of it. Complete tool must be made available, which falls out bit of the initial meaning of web services.

#### Remote access of reconfigurable hardware

Paper [16] presented an approach for the integration of reconfigurable hardware and computer applications based on the concept of ubiquitous computing. A set of reconfigurable hardware modules can be plugged in a network and be transparently accessed by client software applications. The client applications must not have any information about the network location or the internal implementation of the reconfigurable modules. The connection between client and reconfigurable hardware is based in a lookup mechanism. The reconfigurable hardware is encapsulated by a service interface, and all the communication with the client is done in the API level, through method calls.

Jini – based technology was used here. This is a relatively new Java-based technology for distributed computing, publicly debuted by Sun Microsystems in January 1999. It claims to address the fundamental difficulties of distributed computing. These difficulties center around the fact that distributed systems are vulnerable to network latency and concurrency problems, complexities in memory management, and inevitable partial failures. Jini technology addresses the difficulties of distributed computing with a simple set of interfaces that are claimed to be well specified and open to implementation by any member of the Java community. Jini technology is built on top of the Java 2 platform. It uses core Java functionality to provide a reliable, portable, distributed computing model. In terms of the Java platform, Jini technology takes advantage of the following:

- The inherent security provided by the Java technology's robust and publicly tested security model

- The portability of Java technology byte code, provided by the widespread availability of Java virtual machines (JVMs)

- The mobility of Java objects, provided by object serialization and remote method invocation (RMI)

Jini technology enables spontaneous networks of devices and software services to assemble themselves into working groups known as federations of clients and services, without the need for intervention by system administrators. The Java language's ability (RMI) to move entire objects, both data and code, allows Jini technology-based systems to deal reliably with partial failures and network issues. Distributed memory management is taken care of using underlying RMI functionality, and concurrency and latency issues become tractable with Jini technology's distributed event support, leasing, and transaction capabilities. Participants in one network can directly access and use the services provided by participants in another network by using objects that move around the network, the Jini architecture makes each service, as well as the entire network of services, adaptable to changes in the network. The Jini architecture specifies a way for clients and services to find each other on the network and to work together to get a task accomplished. Service providers supply clients with portable Java technology-based objects that give the client access to the service. This network interaction can use any type of networking technology such as RMI, CORBA, or SOAP, because the client only sees the Java technology-based object provided by the service and, subsequently, all network communication is confined to that Java object and the service from whence it came. When a service joins a network of Jini technology-enabled services and/or devices, it advertises itself by publishing a Java technology-based object that implements the service API. This object's implementation can work in any way the service chooses. The client finds services by looking for an object that supports the API. When it gets the service's published object, it will download any code it needs in order to talk to the service, thereby learning how to talk to the particular service implementation via the API. The programmer who implements the service chooses how to translate an API request into bits on the wire using RMI, CORBA, XML, or a private protocol.

Jini technology is promising, especially when truly distributed spontaneous and robust systems must be designed. However, firewall traversal can be problematic again – dedicated communication ports are needed. Another issue is the bandwidth required for communication, especially in case of mobile devices.

# 2.3 Discussion

Considering implementation approaches used above for web-based design activities, it is clear that most popular development platform is Java environment and that's for reason – Java is portable, mature, fast enough nowadays, it is free and what's most important – it is meant for network programming from start.

There exist at least alternatives like Microsoft ASP .NET platform, PHP for web-based software development, but none of them was surprisingly considered in papers found. Development of web applications with .NET could be rapid, actually faster than in case of Java or PHP since GUI development and data access to Microsoft SQL server is well automated, manual coding is much less, web services development is supported as well. However, developer has to stick to Windows platform. Even change of back end database to something else (for example to open source db MySQL) will slow down the development process considerable since data access functions must be mastered by designer itself again. PHP in turn is essentially scripting language engine running as web server extension. PHP language is used much for building web sites. Therefore, it is suitable for development of user interfaces. If information polling strategy can be used then it is obviously possible to use also PHP for simpler remote tool usage system development.

Considering further Java based implementations, RMI based solutions dominated. As it was stated earlier, RMI (Remote Method Invocation) is elegant programming solution for distributed computing were one program can remotely invoke methods physically residing in other machine. However, firewall traversal can be problematic, as dedicated communication ports are needed. Strict security policy might not allow that.

It seems that approaches based on the eXtensible Markup Language (XML) are widely suggested. The W3C [26] defines a set of XML-based languages that are the foundation for the current notion of web services. The Web Service Description Language (WSDL) is used to describe the interfaces of a web service. These interfaces can be accessed using the Simple Object Access Protocol (SOAP). WSDL descriptions can be made available via a central UDDI registration (Universal Description, Discovery, and Integration), e.g., in order to implement resource discovery.

However, currently there are some serious reservations using such web services for industrial applications. The related standards like SOAP are currently evolving fast with the side effect of introducing compatibility issues and general uncertainty. Since these technologies are not stable yet, it is undesirable to apply them today in a true industrial context. Integration technology for WSDL must change and hopefully become as transparent as accessing other content in the Internet in order to be successful in the future. The usage of this technology for embedded system design is of high interest, because it offers on one side more freedom for the user of such systems and on the other side for the tool vendor new business concepts or licensing models.

The ordinary integration technologies still have their merits. Because web services represent a weak coupling and require more dynamic processing for the protocols a certain overhead is generated which slows down the interaction. Especially "popular" web services may have

long latencies that reflect the same behavior as visiting heavy-loaded web servers. In the intranet the common integration techniques are to be preferred because the location of tools and applications is known and under direct administration. Additionally this technique of integration allows an efficient adoption to the clients requirements, whereas changing a web service depends on the cooperation of the service provider. Usually there are different clients with contradicting requirements, which are not easy to meet by the provider.

For site-spanning tool integration, one has to consider open and known security problems in order to highly protect the exchanged IP-s. Due to those problems, SNMP-based solutions seem to be less applicable for open networks. Nevertheless, also XML-based alternatives with SOAP servers currently have significant unsolved security problems. We see that network-based solutions for non-secure environments still require significant investigations in authentication and encryption when exchanging control and highly sensitive (i.e., IP-protected) design data [17].

One problem is that XML-based messages are larger and require more processing than those from existing protocols: data is represented inefficiently and binding requires more computation. It has been shown that an RMI service can perform up to an order of magnitude faster than an equivalent Web Service due to the processing required to parse and bind XML data into programmatic objects [27].

We see, there are many possibilities, which makes cooperation harder. For example, WSDL and CORBA are similar approaches, but technically different. This means that it is harder to cooperate between enterprises to come up with virtual laboratories for example. The hope is that interfaces will eventually be standardized allowing seamless operation.

Jini based solution is not attractive alternative either because it is also based on RMI (Remote Methods Invocation). Such approach will not work well in firewall-protected environments. Considerable effort has to be made to configure enterprise firewalls. In some cases, this might not be possible at all.

In conclusion, plain HTTP protocol based solutions seem to be still best choice, since HTTP is well established and such solutions are more flexible in firewall-protected environments. Communication port 80, used by ordinary web browsers is always available on the client side of the system. It is also possible to add SSL (Secure Socket Layer) encryption to communication between two endpoints. This is big advantage when exchanging possibly sensitive design and test information. Choosing Java as development platform gives us portability and rich and widely accepted development environment for network programming. Java has also powerful classes to simplify HTTP communication. Data can be simply sent over the network as objects i.e. data bundles.

As a final remark, all the papers found and discussed above were dealing design issues, there was no evidence of using web-based environment for testing or digital test tools implicitly.

# **3** Test Generation for Digital Systems with Genetic Algorithms

Several techniques for solving the problem of generating tests for structural faults in sequential circuits have been proposed over the years. On the gate-level, a number of deterministic test generation algorithms have been implemented. However, the execution times are extremely long and for medium and large circuits mostly rather low fault coverage has been achieved. Better performance has been reported of simulation-based approaches. The above approaches are fast for smaller circuits only and become ineffective when number of primary inputs and sequential depth of the circuit increase.

Test generation approaches that rely on functional fault models only do not guarantee satisfactory structural level fault coverage. As a solution, hierarchical approaches have been proposed which take advantage of high-level information during generating tests for gate level faults. While hierarchical test pattern generation still remains the fastest method for solving the problem, it is not applicable for designs that do not have an appropriate modularity or where the higher-level information is not known.

Genetic algorithm based test generation overcomes the difficulties when deterministic generators are too slow and fast approaches, like hierarchical test generation, are not applicable to circuit due to lack of proper information; when fault coverage is too low or amount of generated test vectors is too large. In current chapter three different test generators are presented: for combinational circuit, for circuits represented as FSM and finally fault oriented TPG for gate level sequential circuit.

# 3.1 Overview of genetic algorithms

John Holland, the founder of the field of genetic algorithms points out in [28] the ability of simple representations (bit strings) to encode complicated structures and the power of simple transformations to improve such structures. Holland showed that with the proper control structure, rapid improvements of bit strings could occur (under certain transformations). Population of bit strings "evolves" as populations of animals do. An important formal result stressed by Holland was that even in large and complicated search spaces, given certain conditions on the problem domain, genetic algorithms would tend to converge on solutions that were globally optimal or nearly so.

In order to solve a problem genetic algorithm must have following components:

- 1) A chromosomal representation of solution to the problem,

- 2) A way to create an initial population of solutions,

- 3) An evaluation function that plays the role of the environment, quality rating for solutions in terms of their "fitness"

- 4) Genetic operators that alter the structure of "children" during reproduction

- 5) Values for the parameters that genetic algorithm uses (population size, probabilities of applying genetic operators)

#### 3.1.1 Representation

In genetic framework, one possible solution to the problem is called individual. As we have different persons in society, we also have different solutions to the problem (one is more optimal than other is). All individuals together form population (society).

We use binary representation for individuals (bit strings of 1's and 0's). Bit strings have been shown to be capable of usefully code variety of information, and they have been shown to be effective representations in unexpected domains. The properties of bit string representations for genetic algorithms have been extensively studied, and a good deal is known about genetic operators and parameter values that work well with them [28].

## 3.1.2 Initialization

For research purpose, random initializing a population is suitable. Moving from a randomly created population to a well-adapted population is a good test of algorithm. Critical features of final solution will have been produced by the search and recombination mechanisms of the algorithm rather than the initialization procedures. To maximize the speed and quality of the final solution it is usually good to use direct methods for initializations. For example, output of another algorithm can be used or human solution to the problem.

## 3.1.3 Fitness function

It is used to evaluate the fitness of the individuals in population (quality of the solutions). Better solutions will get higher score. Evaluation function directs population towards progress because good solutions (with high score) will be selected during selection process and pour solutions will be rejected.

#### 3.1.4 Fitness scaling

Many properties of evaluation function enhance or degrade a genetic algorithm's performance. One is normalization process used. Normalization is *fitness scaling* (increasing the difference between the fitness values). As a population converges on a definitive solution, the difference between fitness values may become very small. Best solutions can't have significant advantage in reproductive selection. For example, let us have scores 2 and 3. If these scores are used without any change as measures of each individual's fitness for reproduction, it will take some time before the descendants of good individual will gain the majority in the population. Fitness scaling solves this problem by adjusting the fitness values to the advantage of the most-fit solutions. For example, we can use squared values of fitness scores. Then, continuing example above we receive new scores 4 and 9 which are much more different now.

The performance of a genetic algorithm is highly sensitive to normalization technique used. If it stresses improvements to much it will lead to driving out of alternative genetic material in the population, and will promote the rapid dominance of a single strain. When this happens, crossover becomes of little value, and the algorithm ands up intensively searching the solution space in the region of the last good individual found. If the normalization process does not stress good performance, the algorithm may fail to converge on good results in a reasonable time and will more likely to lose the best members of its population.

#### 3.1.5 Fitness function and noise

In some cases, there will be no known fitness function that can accurately assess an individual's fitness, so an approximate (noisy) fitness function must be used. The noise inherent from noisy fitness function causes the selection process for reproduction to also be noisy [29]. We assume that a noisy fitness function returns a fitness score for an individual equal to the sum of real fitness of the individual plus some noise. Noisy information may come from a variety of sources, including noisy data, knowledge uncertainty, etc. To improve run – time performance some genetic algorithms use fast but noisier fitness function instead of more accurate, but slower, fitness function that may also be available. Sampling fitness functions are a good example of this phenomena: fitness function uses smaller (reduced) sampler size to increase run – time speed, at the expense of decreased accuracy of the fitness evaluation.

#### 3.1.6 Reproduction

During reproductive phase of genetic algorithm, individuals are selected from population and recombined, producing child (individual), which will be added into next generation. Parents are selected randomly from the population using a scheme, which favors the more fit individuals. Good individuals will probably be selected several times in a generation, poor ones may not be at all. Having selected two parents, their genes are combined, typically using the mechanisms of crossover and mutation. Next, we take a closer look on genetic operators.

## 3.1.7 Selection