#### TALLINN UNIVERSITY OF TECHNOLOGY

Faculty of Information Technology

### IEE70LT

Apneet Kaur 132094IVEM

# Online Fault Detection Methodology for Control and Data Path of IP Cores: Case Study on Bonfire Network-On-Chip

Master's Thesis

| Supervisor    | : Dr. Paul Annus              |

|---------------|-------------------------------|

|               | (PhD, Sr. Research Scientist) |

| Co-Supervisor | : Prof. Jaan Raik             |

|               | (PhD, Professor)              |

|               | Er. Siavoosh Payandeh Azad    |

|               | (MSc, Early Stage Researcher) |

|               | Er. Behrad Niazmand           |

|               | (MSc, Early Stage Researcher) |

#### TALLINNA TEHNIKAÜLIKOOL

Infotehnoloogia Teaduskond

### IEE70LT

Apneet Kaur 132094IVEM

# Metodoloogia tuumade juht- ja andmeosa rikete avastamiseks töörezhiimis: juhtumiuuring Bonfire kiipvõrgul

Magistritöö

Juhendaja : Dr. Paul Annus (PhD, Vanemteadur) Kaasjuhendaja : Prof. Jaan Raik (PhD, Professor) Er. Siavoosh Payandeh Azad (MSc, Nooremteadur) Er. Behrad Niazmand (MSc, Nooremteadur)

## Author's Declaration

I hereby certify that I am the sole author of this thesis. All the used materials, references to the literature and the work of others have been referred to. This thesis has not been presented for examination anywhere else.

Name:Apneet Kaur Date: June 7, 2016

### Acknowledgement

I would first like to sincerely thank my advisor and Co-Supervisor, Prof. Jaan Raik for his guidance, patience and support. He gave me much freedom to explore interesting problems of NoC, while providing invaluable insights and comments on my thoughts. My research has been benefited greatly from his knowledge. His high standards played a key role to build up my confidence in both the normal and research life, which is the most precious achievement I am gaining during the study. I would like to thank my Supervisor, Dr. Paul Annus for availing me with the great opportunity of carrying out my research thesis work at department of Computer Engineering at Tallinn University of Technology.

Special thanks to my third and fourth Co-supervisors Siavoosh Payandeh Azad (Jr. Researcher, TTU) and Behrad Niazmand (Jr. Researcher, TTU) for their patience and valuable guidance. Thanks for considering me capable for the position of IEEE-WIE Chairperson. They have lead the whole team of 12, working on the Bastion and Immortal Project through weekly meetings and intensive brainstormings. Thanks for continuous feedback and correcting me at every step of thesis that motivate me to aim for perfection. A special thanks to my colleagues in Computer Engineering department Vineeth Govind (Sr. Researcher, TTU, Estonia) who taught me initially about the designing of Network Interface. Thanks to Karl (Jr. Researcher, TTU), Hardi (Masters, TTU), Tsotne (Masters, TTU), Martin (Masters, TTU) and Nevin (Masters, TTU) for the support and enjoyable working environment.Thanks to Erasmus-Mundus Heritage (2013-2015) and Estonian Science Foundation Grant 9429(2015-2016) for funding my studies.

A Special thanks to my Family, Guneet Kaur (Mother, creative home maker), Baljinder Singh(Father, Retd. Bank Manager) for their support through phone and skype calls and to my siblings Dapinder Singh (Brother, Chief Engg. MMS) and Tanzeer Kaur (Sister, Assistant Prof. PU) for they are my great role models and motivating to be like them.

Finally, I would like to thank my fiancée Deepak Pal, (Jr. Researcher/Software Developer Elvior) for the support, encouragement and patience provided during my research. Thanks for cheering me up in my hard times.

### Abstract

The continuous scaling in technology has caused the components of a networkon-chip to be more vulnerable to faults; therefore, there is a need for methods to maintain circuit performance. This dissertation propose a methodology to partition design into control and data parts, each to be protected by different circuitry. An increasing number of faults appear during the run-time of the system caused by temperature-time dependent degradation and environmental effects like radiation or electromagnetic noise. Thus, online fault monitors are required for detecting faults during circuit's life-time. The concurrent checkers monitor the control part and error control code checks the data-path of the NoC. A new method and tool framework is developed for checker efficiency index with minimum area overhead. Concurrent checkers and error control codes are implemented for a case study on a TUT design project Bonfire NoC evaluating different error control mechanisms and strategies.

### Annotatsioon

Kiibitehnoloogiate pidev miniaturiseerimine on muutnud kiipvõrgud rikete suhtes tundlikumaks. Seega on vajadus uute meetodite järgi, mis säilitaksid kiipide jõudluse. Käesolev dissertatsioon pakub välja metodoloogia skeemi tükeldamiseks juht- ja andmeosaks, milledest kumbki oleks kaitstud erineva arhitektuurse lahendusega. Üha kasvav hulk rikkeid toimub süsteemi eluajal põhjustatuna temperatuurist tulenevast degradeerumisest ning keskkonnast tulenevast kiirgusest ja elektromagneetilistest häiretest. Seega on tarvis rikkemonitore ja veakodeerimisel põhinevaid lahendusi skeemi eluajal tekkivate vigade avastamiseks. Monitorid jälgivad kiipvõrgu juhtosa ning veakodeerimisel põhinevad skeemid jälgivad selle andmeosa. Dissertatsioonis töötati välja uus meetod ja programne keskkond rikkemonitoride kvantitatiivseks analüüsiks ning nende hulga minimiseerimiseks, mille eesmärgiks on piisava rikete katte saavutamine minimaalse lisakuluga. Rikkemonitore ja veakodeerimisel põhinevaid mehanisme rakendati TTÜ Bonfire kiipvõrgu projektis toimunud juhtumiuuringus, et hinnata erinevaid tõrkekindlaid strateegiaid.

## Abbreviations

| NOC                  | -Network on Chip                                   |

|----------------------|----------------------------------------------------|

| IC                   | -Integrated Chips                                  |

| SoC                  | -Semiconductor on Chip                             |

| MPSoc                | -Multiple processors on system on chip             |

| ECC                  | -Error Control Code                                |

| SECDED               | -Single Error Correction Double Error Detection    |

| NI                   | -Network Interface                                 |

| SP                   | -Single Parity                                     |

| CRC                  | -Cyclic Redundancy Code                            |

| DAP                  | -Duplicate Add-Parity                              |

| BCH                  | -Bose-Chaudhuri-Hocquenghem Codes                  |

| RS                   | -Reed-Solomon                                      |

| DMR                  | -Double-Modular-Redundancy                         |

| TMR                  | -Triple-Modular-Redundancy                         |

| SEU                  | -Single Event Upset                                |

| BICST                | -Built-In Concurrent Self-Test                     |

| ROWR                 | -Reduced Observation Width Replication             |

| LBDR                 | -Logic Based Distributed Routing                   |

| IIR                  | -Inherent Information Redundancy                   |

| ForEVeR              | -Formally Enhanced Verication at Runtime for NoCs  |

| VCs                  | -Virtual Channels                                  |

| CTS                  | -Clear To Send                                     |

| RTS                  | -Ready To Send                                     |

| EMI                  | -Electro-Magnetic-interference                     |

| SER                  | -Soft Error Rate                                   |

| FCC                  | -Forward error correction                          |

| CEI                  | -Checkers Efficiency Index                         |

| $\mathbf{FC}$        | -Fault Coverage                                    |

| $\operatorname{FPR}$ | -False Positives Ratio                             |

| TT                   | -Turbo Tester                                      |

| SSBDD                | -Structurally Synthesized Binary Decision Diagrams |

| BDD                  | - Binary Decision Diagrams                         |

| $\operatorname{FFR}$ | - fan-out free regions                             |

| SAF                  | -Stuck-At-Fault                                    |

| LFSR                 | -Linear Feedback Shift Registers                   |

| B-M                  | -Berlekamp-Massey                                  |

| FCS                  | -Frame Check Sequence                              |

| $\mathbf{FF}$        | -Flip-Flop                                         |

| FSM                  | -Finite State Machine                              |

| RR                   | -Round-Robin                                       |

| DRTS                 | -Detect Ready To Send                              |

| Read en              | -Read Enable                                       |

| empty out            | - Empty signal                                     |

|                      |                                                    |

# Contents

| List | of Figu                                                                            | 1res                                                                                                                                                                                                                            | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List | of Tab                                                                             | les                                                                                                                                                                                                                             | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Intr | oducti                                                                             | ion                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1  | Motiv                                                                              | ation                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2  | Relate                                                                             | ed work                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 1.2.1                                                                              | Data Error correction and Detection                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 1.2.2                                                                              | Concurrent Online Testing                                                                                                                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3  | Contr                                                                              | ibution                                                                                                                                                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.4  | Outlin                                                                             | ne of Thesis                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Net  | work (                                                                             | On Chip Architechture                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.0.1                                                                              | Topologies                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.0.2                                                                              | Routing                                                                                                                                                                                                                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 2.0.3                                                                              | Switching                                                                                                                                                                                                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fau  | lts and                                                                            | d Fault Tolerance                                                                                                                                                                                                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1  | Fault                                                                              | sources and classification                                                                                                                                                                                                      | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.1.1                                                                              | Transient faults                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.1.2                                                                              | Intermittent faults                                                                                                                                                                                                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.1.3                                                                              | Permanent faults                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2  | Fault                                                                              | Tolerance Techniques                                                                                                                                                                                                            | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.1                                                                              | Static Fault Tolerance                                                                                                                                                                                                          | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 3.2.2                                                                              | Dynamic Fault Tolerance                                                                                                                                                                                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | List<br><b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4<br><b>Net</b><br><b>Fau</b><br>3.1 | List of Tab<br>List of Tab<br>Introduct:<br>1.1 Motiv<br>1.2 Relate<br>1.2.1<br>1.2.2<br>1.3 Contr<br>1.4 Outlin<br>Network 0<br>2.0.1<br>2.0.2<br>2.0.3<br>Fault<br>3.1 Fault<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2 Fault<br>3.2.1 | 1.2 Related work       1.2.1 Data Error correction and Detection         1.2.1 Data Error correction and Detection       1.2.1         1.2.2 Concurrent Online Testing       1.2.2         1.3 Contribution       1.3         1.4 Outline of Thesis       1.4         1.4 Outline of Thesis       1.4         Network On Chip Architechture       2.0.1         2.0.2 Routing       2.0.2         2.0.3 Switching       2.0.3         Switching       1.4         Suit sources and classification       3.1.1         Transient faults       3.1.2         3.1.1 Transient faults       3.1.3         9ermanent faults       3.1.3         3.2 Fault Tolerance Techniques       3.2.1         Static Fault Tolerance       3.2.1 |

| 4        | Cor | ncurrent Online Checkers                                     | 18 |  |  |

|----------|-----|--------------------------------------------------------------|----|--|--|

|          | 4.1 | Structurally Synthesized Binary Decision Diagrams (SSBDD) 19 |    |  |  |

|          |     | 4.1.1 SSBDD Structure                                        |    |  |  |

|          |     | 4.1.2 SSBDD Simulation                                       | 20 |  |  |

|          | 4.2 | Enhanced analyze tool outputs                                | 22 |  |  |

|          |     | 4.2.1 Fault Table                                            | 22 |  |  |

|          |     | 4.2.2 Nodes Detection Information                            | 23 |  |  |

|          |     | 4.2.3 Checkers Detection Information                         | 23 |  |  |

|          |     | 4.2.4 Checkers Detection Absolute Weights                    | 23 |  |  |

|          |     | 4.2.5 Fault Free Checker Firing Information                  | 24 |  |  |

|          |     | 4.2.6 Input Patterns True Misses Count                       | 24 |  |  |

| <b>5</b> | Er  | ror Control Codes                                            | 25 |  |  |

|          | 5.1 | Single Parity                                                | 25 |  |  |

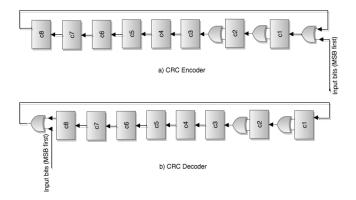

|          | 5.2 | Cyclic Redundancy Codes                                      | 26 |  |  |

|          | 5.3 | B Hamming Codes                                              |    |  |  |

|          | 5.4 | Bose-Chaudhuri-Hocquenghem Codes                             | 27 |  |  |

|          | 5.5 | Reed-Solomon Codes                                           | 27 |  |  |

| 6        | Imp | plementation of ECC                                          | 29 |  |  |

|          | 6.1 | Hamming Codes Implementation                                 |    |  |  |

|          | 6.2 | CRC Implementation                                           | 31 |  |  |

|          | 6.3 | Single Parity Implementation                                 | 32 |  |  |

| 7        | Imp | plementation of Checkers                                     | 34 |  |  |

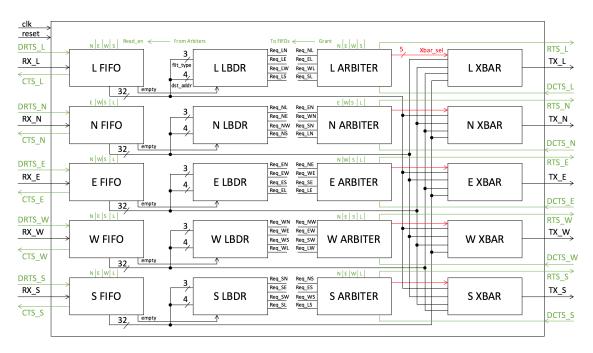

|          | 7.1 | Online fault detection in NoC Router                         | 34 |  |  |

|          | 7.2 | Pseudo-combinational version of FIFO control part            | 36 |  |  |

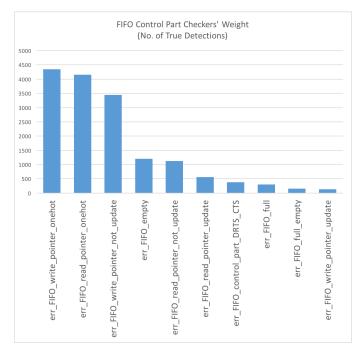

|          |     | 7.2.1 FIFO control part checkers                             | 38 |  |  |

|          | 7.3 | Pseudo-combinational version of LBDR                         | 39 |  |  |

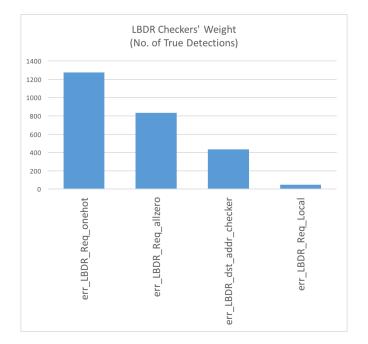

|          |     | 7.3.1 LBDR checkers                                          | 40 |  |  |

|          | 7.4 | Pseudo-combinational version of Arbiter                      | 41 |  |  |

|          |     | 7.4.1 Arbiter checkers                                       | 42 |  |  |

|          | 7.5 | Experiment Results                                           | 43 |  |  |

|              | 7.6 Result Analysis                        | 46        |

|--------------|--------------------------------------------|-----------|

| 8            | Conclusion                                 | 47        |

| A            | PPENDICES                                  | <b>54</b> |

| A            | Simulation Results for SP, Hamming and CRC | 55        |

| В            | Definitions                                | 56        |

| $\mathbf{C}$ | Evaluation Results for LBDR                | 57        |

# List of Figures

| 2.1 | A 4x4 NoC example in 2D mesh topology.                           | 7  |

|-----|------------------------------------------------------------------|----|

| 2.2 | Direct topologies.                                               | 9  |

| 2.3 | Indirect topologies                                              | 9  |

| 2.4 | An example of XY routing algorithm                               | 11 |

| 2.5 | Packet structure for NoC                                         | 12 |

| 2.6 | Architecture of router for NoC                                   | 12 |

| 4.1 | Concurrent checker logic                                         | 18 |

| 6.1 | CRC encoder and decoder block diagram.                           | 32 |

| 7.1 | HIgh level NoC router architecture for control part              | 35 |

| 7.2 | FIFO control part checkers detection absolute weights            | 39 |

| 7.3 | LBDR checkers detection absolute weights                         | 41 |

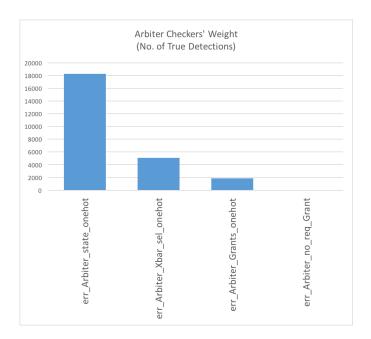

| 7.4 | Arbiter checkers' detection absolute weights                     | 43 |

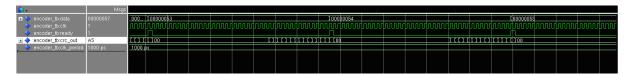

| A.1 | Simulation report for Hamming encoder and decoder.               | 55 |

| A.2 | Simulation Report for CRC encoder.                               | 55 |

| A.3 | Simulation Report for CRC decoder.                               | 55 |

| A.4 | Simulation Report for Single Parity                              | 55 |

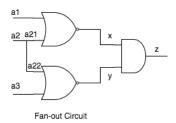

| B.1 | Concept of Fan-out                                               | 56 |

| B.2 | Fan-out Free Regions Constructed using Superposition Algorithm . | 56 |

| C.1 | Input test pattern                                               | 57 |

| C.2 | Checkers output                                                  | 57 |

| C.3 | SSBDD representation file                                        | 57 |

# List of Tables

| 6.1 | 32 bit data combination for parity calculation                                                 | 30 |

|-----|------------------------------------------------------------------------------------------------|----|

| 6.2 | Syndrome values for error detection.                                                           | 31 |

| 7.1 | FIFO Control Part checkers' Detection Absolute Weight                                          | 39 |

| 7.2 | LBDR checkers detection absolute weights                                                       | 41 |

| 7.3 | Arbiter checkers detection absolute weights                                                    | 43 |

| 7.4 | Area report for NoC router modules                                                             | 44 |

| 7.5 | Area report for error control codes.                                                           | 44 |

| 7.6 | Area report for pseudo-combinational circuits                                                  | 45 |

| 7.7 | Area report for checkers                                                                       | 45 |

| 7.8 | checkers efficiency index (CEI) and fault $\operatorname{coverage}(\operatorname{FC})$ results | 45 |

# Chapter 1

# Introduction

### 1.1 Motivation

The continuous scaling in semiconductor technology enables the amount of transistors on a single chip to be doubled in every 18 months as theorized in Moore's Law. Today IC's have a high capacity of transistors and capable of connecting various components onto a single chip forming a system on chip. Conventionally, SoC had a single processor connected to peripherals using bus or crossbar architecture. Now, SoC also provides possibility to connect multiple processors system on chip MPSoC.

As semiconductor technology scales down further, the SoC design problem focus shifts from data processing towards effective communication which is now a major contributor for SoC performance and implementation cost. Traditionally, the interconnection between multiple cores in SoC followed conventional bus or crossbar structures. However, with the increasing number of processing cores, the conventional communication media become the system's bottleneck due to their low scalability. Though, to enable concurrent data transmission, busses can be segmented [1] at the expense of higher arbitration complexity or replaced with crossbars at the expense of a significantly larger number of wires. However, segmented buses and crossbars are not fully scalable and thus can provide only an intermediate solution. The Network-on-Chip NoC model [2] has been proposed and is widely accepted as a scalable and reliable communication infrastructure replacement of buses and crossbars[5]. NoC is not just more scalable, can also operate at much higher clock frequency and has lower power consumption [8]. However, further scaling of integrated circuits makes the NoC design more vulnerable to different kinds of faults, thus, making design's reliability a real challenge. For correct behavior of the system, data integrity is important. Different error control codes are implemented and analysed in terms of area in this work. Also, an increasing number of faults appear during the run-time of the system caused by temperature-time dependent degradation and environmental effects like radiation or electromagnetic noise. Thus, concurrent fault monitors for detecting faults during circuit's lifetime are needed. These checkers would report errors within routers and would allow reconfiguration of the routing infrastructure, that operate during the lifetime of system and parallel with its normal operations. The thesis proposes a new methodology of partitioning systems into control and datapath with the former to be covered by online checkers and the latter with error correcting codes. In addition methods for automated checker qualification and minimization are presented. In this chapter a brief overview of related work about the error control codes techniques and on-line testing is detailed.

### 1.2 Related work

The related work is divided into two parts one for fault detection and correction in data and other for designing concurrent online-checkers for faults in control logic.

#### **1.2.1** Data Error correction and Detection

Error detection and correction techniques help to maintain the data integrity of the system. There are two well-known schemes namely, end-to-end encoding that work at network level and switch-to-switch encoding at link level. A hybrid of both schemes can also be used along with retransmission [10]. The error control schemes are not efficient in case of intermittent errors. For instance, for intermittent errors a system get stuck at retransmissions of a single piece of data due to continuous error. The error detection and correction scheme fails in case of permanent error, and it takes a large area overhead to develop strong error control schemes for permanent and intermittent errors. This literature survey provides a large amount of useful data in order to select a suitable error control scheme for a given NoC design. The end-to-end encoding strategy is applied in the network interface on the entire packet at the source and destination points. The power consumption of end-to-end error control is less than that of hop-to-hop error control at low error rate, route length and small number of retransmissions [21]. More errors can appear in data because of no error recovery at hops in the router. Retransmission causes increase in latency, if it occurs frequently. In end-to-end, ECC require strong error control scheme to meet the same reliability level of hop-to-hop ECC, possibly requiring a larger codec in NI in case of high noise conditions. A simple end-to-end ECC technique combined with a timeout retransmission mechanism has been proposed to reduce the latency caused by packet corruption or loss [23].

In [25] author proposed a method that makes use of the extended Hamming code known as a Single Error Correction Double Error Detection (SECDED) code in the NI. The method is able to improve energy efficiency for a variety of design parameters with area overhead as the main limitation. In [26], the author compares different error detection and correction schemes to find the most efficient error control technique from energy viewpoint, that includes Hamming codes, extended Hamming codes, parity check codes, and CRC codes.

The number of simultaneous permanent, transient, intermittent or burst errors are expected to increase in future with the continuous scaling of the IC's. A multipleerror correction code is constructed by combining Hamming codes with Duplicate-Add-Parity (DAP) codes [29]. In this method, the outputs of a hamming encoder are duplicated and an extra parity bit generated from the original hamming code is added. This method requires a large number of additional interconnect wires that greatly increases the energy consumption and link area overhead. Bose-Chaudhuri-Hocquenghem Codes (BCH) codes are considered as an important class of linear block codes for multiple error correction. The BCH encoder follows approach similar to cyclic codes. Reed-Solomon (RS) codes are a subclass of BCH codes good at correcting multiple symbol errors. The BCH and RS codes are implemented in NoC links, that can correct multiple errors with limitation of large codec area, power consumption and decoding time[27].

#### **1.2.2** Concurrent Online Testing

The faults in logic circuits and its online detection is a thoroughly studied research area. Techniques like Double-Modular-Redundancy (DMR) or Triple-Modular-Redundancy (TMR) are most simple way to implement online detection with redundancy and are costly in terms of area overhead and increase in power consumption. To minimize this overhead, selective TMR can be used to identify Single Event Upset (SEU) in the circuits [35]. The Built-In Concurrent Self-Test (BICST) technique[36] and Reduced Observation Width Replication (ROWR) technique [37] achieve high fault coverage at low area overhead with limited pre-computed test vectors. Though, these approaches are susceptible to miss faults during normal operation of the circuit.

Checkers can be extracted from the functional logic of the design [38], but it has limitation of low fault coverage and large area overhead, higher than DMR scheme. On the other hand, an approach based only on functional assertions or reuse of verification assertions suffers from low fault coverage of structural faults, and the obtained functional coverage is difficult to relate with the structural one [39].

A number of previous works propose error control methods for reducing faults in a router of a NoC. Fault tolerance was added in NoC topologies for detecting errors in routing logic using Logic Based Distributed Routing mechanism [42] and its extension was used for high-radix topologies, i.e LBDRhr [43]. This method utilizes the Inherent Information Redundancy (IIR) to reduce the area overhead, but it did not had full fault coverage. Authors of [44] have presented a method for online error detection and diagnosis of NoC switches. This method addresses routing faults caused by packet corruption in such a way that it forwarded to a wrong destination port. A high-level fault model has been proposed that has fault coverage only at the functional level and lacks generality with area overhead. In [45], ForEVeR (Formally Enhanced Verification at Runtime for NoCs) method proposes a network-level detection and recovery solution. It provides a solution to detect functional errors in NoCs. This approach detects only 30 percent of the faults in first clock cycle and has large latency. The work in [46] ensures network functional correctness by implementing checkers based on using set of 32 invariance. The unexpected behavior is captured by any one of the 32 assertion checkers. However, it is not clear how injection of faults, fault simulation and evaluation of coverage are accomplished by this method. Moreover the approach is not automated and lacks the completeness and minimization aspects. An automated framework is proposed which provides a minimized list of online checkers for checking the control part of on-chip routers. This method is closest to the idea of concurrent online detection which is considered in this dissertation. It makes use of 5 checkers from set of 31 and with covering only the control part of NoC with large area overhead. In this dissertation LBDR considered for designing checkers are more generic i.e considering all 4 ports (E, W, S, N), whereas in [40] it considers East - LBDR. The Checkers design for this dissertation are inspired by the work of [40] and same method and filtering approach is used for the input stimuli (environment).

### **1.3** Contribution

This dissertation propose a methodology to partition design into control and data parts, each part to be protected by checkers and error control code respectively. As background information fault types, its sources, classification and a survey of fault tolerance methods are studied and presented in this dissertation. For reliable on-chip communication different types of error control codes are studied out of which hamming, cyclic redundancy codes and single parity are implemented and compared in terms of area. The thesis proposes a new methodology of partitioning systems into control and data-path with the former to be covered by online checkers and the latter with error correcting codes. In addition, new method and tool framework for checker qualification and minimization is developed.

The case study Bonfire NoC includes implementation of the ECC and Checkers which is shown in Chapter 6 and Chapter 7. This case study is a part of a "EU's Horizon 2020 Research and Innovation Action IMMORTAL" and "EU's FP7 Collaborative Research Project BASTION". The design decisions made in the case study will be used in the real manufacturing of the fault tolerant IC by the team members of projects from TTÜ.

### 1.4 Outline of Thesis

The introduction chapter has given an overview of the thesis. The rest of thesis is organized as follows: chapter 2 provides the basis for better understanding of Network on Chip (NoC) describing its basic building blocks, network topologies, routing algorithms and switching techniques. Chapter 3 classifies the types of faults, most common fault sources are discussed. It gives basis for understanding of fault tolerance methods divided under two categories namely static and dynamic. In chapter 4 the basics of concurrent checkers and the new metrics used in fault evaluation are explained. Chapter 5 explains about the ECC techniques concept in theory. In chapter 6 selected ECC are implemented and its area is compared. Chapter 7 discuss about the checkers devised to deal with the control faults and its experimental results are presented with discussion. Chapter 8 Concludes about the results and explains the possible future work.

# Chapter 2

# Network On Chip Architechture

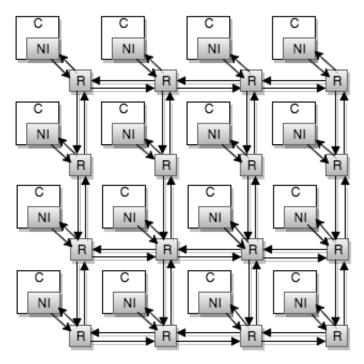

The main components of NoC are routers, network interface and physical links that provide communication between multiple processors on chip. The figure 2.1 shows A 4x4 NoC example in 2D mesh topology.

C - Core, NI - Network Interface, R- Router

Figure 2.1: A 4x4 NoC example in 2D mesh topology.

• Network interfaces act as an interface between the cores and the routers. It accepts data in form of packets from router and de-packetize it to send it into core. For this purpose it has a packetizer and a de-packetizer and a buffer to store data.

- Routers are considered to be the backbone of the NoC. It has five output ports out of which four ports are connected to the four neighboring routers and fifth port is connected to network interface. The routing algorithm, flow control and switching techniques play a very important role in routers. A NoC router contains of a number of input and output ports, a switching matrix connecting the input ports to the output ports, and a local port to access the IP resource connected to the same router.

- Links connect adjacent routers. The interconnect between two adjacent routers are usually composed of two unidirectional links which in charge of the outgoing or incoming traffic, respectively. It is possible to replace. The cores in NoC can be any processing or memory units.

The factors that influence the performance of a NoC are *topology* that determine the arrangement of channels and routers, *routing technique* defines the way a message is transmitted from the source to the destination, *flow control* that tells how are network resources allocated when packets travel through the network, *router architecture* with various components such as buffers and switches, and *traffic pattern*.

#### 2.0.1 Topologies

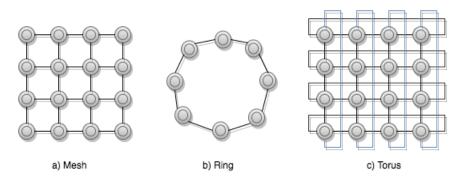

Topology defines the way routers are connected to each other to form a network. The routers can be connected in a direct or an indirect form. NoC with direct topologies are where every node in the network is both a terminal and a switch for example *mesh*, *torus*, *hypercube*, *octagon* topologies. The Indirect topology are where nodes are either switches or terminal for example *fat-tree and three-stage butterfly*. The mixed topology are application specific. All the topologies are illustrated in figures 2.2 and 2.3 below for better understanding. All circular nodes in the figures are represented as routers and black squares are resources.

The well known basic topologies are the *ring* where the routers connect forming a ring and star, where all routers in network are connected to main central router. *Mesh* topology is the most common form of direct topology in network-on-chip.

Figure 2.2: Direct topologies.

In this, each cores is connected to one router via network interface. The router is connected to its four neighboring routers in four different directions, viz. east, west, north, south except routers in corners which are connected to two. The major drawback of this topology is the long distance between the edge routers. This drawback was overcome in *torus* topology, where routers on edges are connected to each other directly. This topology have problem of uneven link length which could be controlled by *folded torus*. The *tree topology* and its variations are part of indirect topology, the two common tree topologies are *binary tree and fat tree*. In the binary tree topology the top most router is the parent router or resource and nodes below it are its descendants. Fat tree structure shows more balance and has less traffic congestion even with more nodes added to it. However, its major drawback is the complexity in design for real implementation.

Figure 2.3: Indirect topologies

#### 2.0.2 Routing

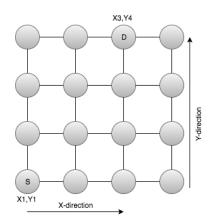

Routing algorithms establish the path to travel by packets from its source to destination. There are many routing algorithms available and discussion of all is out of scope of this dissertation. In this section we will introduce some common routing algorithms terms with main focus on XY routing which is used in our case study. The selection of the route for a packet through the network is defined by its routing algorithm. Based on routing decisions the algorithm can be Distributed, Source, Hybrid or Centralized. In distributed routing, the function is calculated as the the packet travels through the network, While in Source routing, the algorithm is decided prior to the packet entry in the network. Hybrid is a multiphase routing where the address can be calculated at the source but paths are decided by the routers like in distributed routing. Centralized routing has a main router as controller where all decisions are made for routing. The routing decisions are not only limited to the address information but on the basis of adaptivity the routing is categorized as *oblivious*, *deterministic and adaptive*. In oblivious routing any change encountered during the travel of the packet through the network does not change the routing function. An oblivious routing can be deterministic but vice versa is not true. In adaptive routing any change observed in path can alter the route of packet. For example, packet can bypass the congested path with another route to reach the destination. It offers better reliability at the cost of complex routing function. The deterministic routing algorithms have fixed predetermined route. The common form of deterministic routing function is source routing and XY routing. In XY routing a packet is first traveled along the x-dimension up to correct column and then along the y-dimension up to the row. Deterministic and oblivious routing algorithms are minimal as they provide shortest path from source to destination. For example, let (X1, Y1) and (X3, Y4) be the source and destination coordinates respectively. Consider a 2D mesh topology, for the X-Y routing first the packet travel in X direction until X1 reach to X3 and then it travel in Y direction until Y1 becomes equal to Y4 as shown in figure 2.4. Routing algorithms with complex functions can create a situation where a packet stay in network without reaching the destination. This state is known as *livelock*. Another critical situation is of *deadlock and starvation. Deadlock* is a situation, where two or more packets wait for a busy resource and at the same time also reserve a resource meant for another packet. Therefore, the network comes to halt because of no packet movement. Starvation is a condition in which a low priority packet may have to wait for its

Figure 2.4: An example of XY routing algorithm.

turn forever. XY routing is best example of a deadlock-free routing algorithm with no cyclic dependencies in packets routing.

#### 2.0.3 Switching

Switching is a technique that decides the transmission of data from source to destination nodes. Switching is broadly classified as Circuit and Packet switching. In *circuit switching* approach the whole path is pre-established and reserved between source and node before the actual transmission of data. The other switching technique is *packet based*, in which the flits of packets are ready for transmission once the header makes connection between routers, this can be done again in two ways, either by storing the flits and forwarding them when there is successful connection between routers or making the flits transmission in a pipeline fashion. The former method is called as the *store-and-forward*, sufficient buffer size is necessary to store the whole packet before transmission permission is granted. In latter method of *wormhole switching*, the flits are send over transmission path as soon as header is encountered at the node. Wormhole switching is also a variant of *virtual-cutthrough mechanism*. This method require buffers for storage of packets which are passed only upon confirmation to next node. In this dissertation, wormhole switching is used in the Noc.

As per the architectural parameters discussed above the case study use 2x2 mesh topology with XY-Routing and Wormhole switching. The message is divided into packets of maximum length  $2^{12}$  with each flit of 32 bit. The Packet format chosen for the case study is shown in the figure 2.5. In figure 2.5 Type = Type of the packet

| Header |           |   |             |        |          |

|--------|-----------|---|-------------|--------|----------|

| 1      | 8 4 4 12  |   |             |        | 3        |

| Р      | ID source |   | destination | length | Туре     |

| Payloa | d         | i |             |        |          |

| 1      | 28        |   |             |        | 3        |

| Р      | Data      |   |             |        | Туре     |

| •      |           |   |             |        |          |

| Tail   |           | • |             |        | <u> </u> |

| 4      | 28        |   |             | 3      |          |

| Р      | Data T    |   |             | Туре   |          |

Figure 2.5: Packet structure for NoC

(one-hot), length= Length of the packet in number of flits = Header+Body+Tail, Destination = Address of the destination Node, Source = Address of the source Node, ID = One-hot Counter that is generated by NI and keeps track of the order of sent packets, Data = The DATA (Payload). In this work we have used router design that utilize a simple architecture without Virtual Channels (VCs) with 4 pipeline stages. It is written in VHDL with simple design (without Virtual Channels (VCs)) and with CTS/RTS handshaking for flow control.The high level NoC router architecture is shown below in figure.2.6. With the knowledge of above flit

| reset  |                 |               |                               |        |        |

|--------|-----------------|---------------|-------------------------------|--------|--------|

| DRTS_L | N E W S Read_en |               | To REOs Crant N E W S 5, Xbar | sel    | RTS L  |

| RX_L   | L FIFO          | fit_type<br>4 |                               | L XBAR |        |

|        | 32 empty        | dst_addr      |                               |        | DCTS_L |

| DRTS_N | EWSL            | 3             | Req_NL Req_EN                 | →      | RTS_N  |

| RX_N   | N FIFO          | 4 N LBDR      |                               | N XBAR | TX_N   |

| CTS_N  | 32 empty        |               |                               |        | DCTS_N |

| DRTS_E | N WS L          | 3             | Reg_EN Reg_NE NWSL            |        | RTS_E  |

| RX_E   | E FIFO          | 4 E LBDR      |                               | E XBAR | TX_E   |

| CTS_E  | 32 empty        |               |                               |        | DCTS_E |

| DRTS_W | NESL            | •             | Reg_WN Reg_NW                 |        | RTS_W  |

| RX_W   | W FIFO          | 4 W LBDR      |                               | W XBAR | TX_W   |

| CTS_W  | 32 empty        |               | Req_WL Req_LW                 | -      | DCTS_W |

| DRTS S | 32 empty        | •             | Reg_SN Reg_NS                 |        | RTS_S  |

| RX_S   | S FIFO          | 4. S LBDR     |                               | S XBAR | TX_S   |

| CTS_S  | 32, empty       |               | Req_SL Req_LS                 | =      | DCTS_S |

|        |                 | •             |                               |        |        |

Figure 2.6: Architecture of router for NoC.

structure and NoC router architecture the ECC techniques and Checkers design is decided.

# Chapter 3

## **Faults and Fault Tolerance**

In electronics a fault is defined as a flaw that occur in a hardware or software component. A fault not necessarily causes an error in the system, whereas failure can occur due to an error [48]. In this chapter the fault types are classified and the most common fault sources are discussed and different techniques for fault tolerance are explained from which we can choose for the target NoC [6].

### 3.1 Fault sources and classification

Faults are broadly classified into transient, intermittent and permanent faults depending upon the duration and location of their occurrence. The source of faults generally depends on the phenomenon causing it, for example, It can occur during a manufacturing process due to lithography variation, resulting in spot or bridging defects, which are permanent in nature. Also other sources include physical changes in the circuit during operation due to electro-migration or increased power consumption. Among other sources are the internal noise in the circuit that can be caused by high frequency, timing uncertainty, crosstalk or due to other parts in the circuit whereas external noise, which is not considered as severe noise is due to the medium radiations in which chip is to be used for e.g. space, nuclear plants etc. These fault types are described briefly in the following subsections.

#### 3.1.1 Transient faults

Transient faults (soft errors) are temporary faults also known as Single Event Upset (SEU). The term SEU explains the fact that soft errors are caused by single events such as absorbed radiation, etc. Such errors occur for a short duration of time due to various factors such as process and temperature variations [14], capacitive and inductive crosstalk noise [15], alpha particles, neutrons or other radiations [16], other noise sources such as Electro-Magnetic-interference (EMI), voltage fluctuation, and electrostatic discharge[17]. The most common example of transient fault is flip of single bit. It is difficult to detect its occurrence because of its random nature. It is generally measured in terms of soft error rate (SER), that tells the probability of error occurrence. Transient faults are the most frequently occurring fault in NoC; up to 80% of all the system failures are associated with transient faults[13].

#### 3.1.2 Intermittent faults

Intermittent faults are periodic in nature but not continuous like permanent faults. It can occur at any time due to temporary environmental change, certain input combinations or conditions making it hard to detect in system. For example, It can be caused by change in certain parameters of the environment such as temperature or voltage change, that alter the normal behavior of the chip. In some cases it can be a considered prior stage to the permanent faults. For instance, due to repeated increase in the resistance wire, it can in turn cause permanent breakdown of wire. The general way to recover from it is to either replace or bypass the faulty circuit in the system [3],[4].

#### 3.1.3 Permanent faults

Permanent faults once occurred cannot disappear from the system. It usually results from manufacturing defect or due to electro-migration, aging of components or due to broken components. Intermittent faults when occur repeatedly for longer duration can lead to the occurrence of permanent errors. Generally, chips are tested during manufacturing in order to detect the permanent faults and rejecting the faulty circuits. If fault is observed during the operation of a circuit, it either has to be replaced or provided with very strong fault tolerance techniques[3], [4].

### **3.2** Fault Tolerance Techniques

Fault tolerance strategy is broadly divided in two categories. *static fault tolerance*, and dynamic fault tolerance. [48], [52], [6].

#### 3.2.1 Static Fault Tolerance

The Static fault tolerance methodology is built into the system to counter the effect of faults. This method usually make use of some type of redundancy which is categorized into hardware, information and time redundancy. The type of redundancy to be used depends upon the particular requirement of the system, sometimes a combination of these can also be used.

**Hardware Redundancy**: This methodology makes use of a physical redundant module with a verifier circuit. The size of module can vary from complete physical circuit to a certain part of the circuit or a logic gate. The most common example of this methodology is triple-modular-redundancy(TMR) that has three redundant modules with a verifier. n-modular redundancy is a more generalized form, with N number of redundancy. In case a module fails to give correct output, the verifier compares the result with other redundant modules output, deciding correct output for the system. The major drawback of TMR is if there is an error in voter circuit, it can result in complete failure of the system. Online testing of the verifier circuit could solve the purpose of internal faults detection, but crosstalk between the module output and verifier input has severe impact resulting in the wrong verifier decision [48].

**Time Redundancy** : In this methodology the redundancy is in terms of time where the system is made to perform same operation for certain time and later the results are compared. This method does not have any extra copy of circuit resulting in no area overhead but huge latency.

**Information Redundancy** : The redundancy in this methodology is added as additional bits to the information bits, based on ECC techniques. These techniques are described in detail later in chapter 5. The forward error correction (FCC) is a technique that makes use of ECC to detect errors and correct at its location.

#### 3.2.2 Dynamic Fault Tolerance

Dynamic fault tolerance is a methodology implemented on active operations of the system. This method follows a set of sequences in its operation as shown below: [13], [6].

Fault detection  $\rightarrow$  Fault Location $\rightarrow$  Fault Containment  $\rightarrow$  Fault Recovery

This method requires special control circuitry and elements to be built for the system, which are usually very complex in its design, but offers better reliability in terms of detecting simultaneous permanent and multiple errors with small area overhead as compared to static fault tolerance approach. It is considered as a promising method for networks-on-chip. Each step of the sequence is explained below.

**Fault Detection** : The fault detection can be implemented in any one of the following forms [52].

- periodic tests : Tests are performed occasionally and output is verified.

- self-checking circuits: Duplication in terms of circuit or time with comparison for output verification.

- watchdog timers : It checks the timer value and resets when its value has exceeded. It is commonly used in multiple processor systems.

The fault tolerance mechanism is decided depending upon the type of error being addressed. Error can be unidirectional, bi-directional, single or burst and various codes for error detection are discussed here. A code with total n number of bits will have m ones and n-m zeros. These code are useful in single and multiple unidirectional errors detection, for example in an online error detecting adder a code of 1-out-of-3 has been used [28]. The berger code is another way to detect all the possible unidirectional errors. This code count the number of 1's in the word and append a complement of the count to the word. For this code the number of check bits are calculated as  $[log_2(k+1)]$  which is least as compared to all available separable codes for detecting unidirectional errors [52]. In order to have much less check bits codes for e.g. the modified berger code, borden code and bose-lin codes were formulated [52].

Error control codes are widely used to detect errors in data. The most common form of ECC is single parity where one bit is appended to the data based on even or odd parity. There are many more sophisticated ECC available which will be discussed later in this section [52].

*Checkers* are special circuits with robust design used to determine error by comparison of the two values which are generated as per the concept of fault-secure or self-testing design methods. These method ensures that a valid input generates a valid output through the circuit. An invalid result is easily observed by this method as they do not fulfill the codeword requirement of this method. A self-testing circuit, indicates fault for certain combination of inputs. In this dissertation the concept of checkers are used and implemented in the case study and is described in more detail in this chapter [52].

**Fault Location**: This step is necessary for error correction and recovery. Sometimes fault location can be found during detection or using self diagnostic methods after detection [52]. ECC can also be used in different combination in NoC for locating the faults.

Fault Recovery : There are three common ways to accomplish fault recovery namely, ARQ, FEC and Hybrid ARQ. ARQ is a method that request for a retransmission upon an error detection. ARQ is suitable for error recovery from transient and intermittent errors but not permanent error because it will give same error no matter how many times it is repeated. FEC techniques are used to recover from error by its correction. FEC schemes cause area overhead because of complex encoder and decoder designs whereas, ARQ method result in huge latency. However, third type of error recovery is popular but costly where Combinations of FEC schemes can be used with timeout ARQ [52], [28]. In the following chapters the concept of error control codes and checkers for NoC is explained.

# Chapter 4

# **Concurrent Online Checkers**

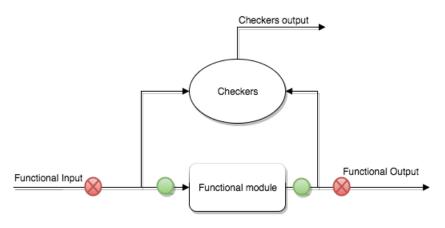

This chapter provides basics for the understanding of checkers. Its implementation with the functional module and role in fault detection is explained. In figure 4.1 checkers are connected with the functional module through its input and output ports. Checkers contain logical assertions based on the input and output ports of the functional module [40].

Figure 4.1: Concurrent checker logic.

In figure 4.1 the logic checks for fault at input or output of each gate of the functional logic, as shown in green circle. On the other hand it do not check faults occurring in functional inputs and output. The terminology for the possible scenarios of fault detection of the injected faults [40] are describes as follows:

- True Detection : The fault is detected both by circuit and checkers.

- True Miss: The fault is detected only by circuit but not by checkers.

- False Positive : The fault is detected only by checkers but not by circuit.

- Benign Miss : The fault is detected neither by circuit nor by the checkers

The faults detected by the circuit is a case, in which for a given fault and input test pattern the fault is propagated to functional outputs of the circuit. In order to check the effective behavior of the checkers model, indices used in this work are taken from the work of [40], [53] denoted as, CEI - Checkers Efficiency Index, FC -Fault Coverage, FPR - False Positives Ratio. If we denote D as true detections by checker for a set of input pattern. F is the fault positive, W and X as true misses and benign misses. Based on these notations, mathematically the indices are given as follows:

$$CEI = \frac{D}{(D+W)}, FC = \frac{D+X}{(D+X+W)}, FRP = \frac{F}{(F+X)}$$

These indices values are obtained in form of outputs from the evaluation tools Turbo Tester (TT) and set of tools used in this work. TT is a software package with low cost approach used for testing and diagnostic purposes. In this work, TT is used to analyze the set of input test patterns using 'analyze' command and to perform fault simulations on the design circuit-under-test. TT can read the schematic from various VLSI tools (in this work synopsis). It present the circuit design in terms of Structurally Synthesized Binary Decision Diagrams (SSBDD). The concept of SSBDD is explained in following section [55], [32]. To learn more about the tool, please refer to [51].

# 4.1 Structurally Synthesized Binary Decision Diagrams (SSBDD)

#### 4.1.1 SSBDD Structure

SSBDD is an extended class of Binary Decision Diagrams (BDD). Unlike BDD, it is not canonical, but provides the complete structural information necessary to identify any problem in circuit and it do not suffer from memory explosion. SSBDD representation is best suitable for complex designed circuits, and it guarantees improved test generation and fault simulation efficiency. It is based on the concept of macros i.e sub-circuits with fan-out free regions (FFR). This model is suitable for Logic level simulations, unlike gate level simulations done in conventional BDD. A SSBDD is constructed using a graph superposition procedure. For this a circuit with gate level description is divided into sub-circuits with FFR. Each sub-circuit has its own SSBDD, thus the final circuit is set of SSBDD's [55]. Explanation of FFR is given in appendix B.

### 4.1.2 SSBDD Simulation

The baseline TT suite provides a tool named analyze, to perform fault simulation for combinational circuits. This is done using Algorithm 1 [55] as explained below:

The enhanced analyze is used in order to identify the presence of online checkers

| Algorithm 1 Fault Simulation                                 |                      |

|--------------------------------------------------------------|----------------------|

| 1: Perform fault-free Logic Simulation (Alg.2)               |                      |

| 2: for each SSBDD in the model do                            |                      |

| 3: take the first node of current SSBDD                      |                      |

| 4: while current node is not a terminal node <b>do</b>       |                      |

| 5: evaluate the current node                                 |                      |

| 6: inject corresponding fault                                |                      |

| 7: perform logic simulation to evaluate output (to ev        | valuate fault prop.) |

| 8: If current output differs from fault-free output <b>t</b> | hen                  |

| 9: mark currently considered fault as detected               |                      |

| 10: <b>end if</b>                                            |                      |

| 11: remove currently considered fault                        |                      |

| 12: move to next node                                        |                      |

| 13: end <b>while</b>                                         |                      |

| 14: end for                                                  |                      |

| Alg | gorithm 2 Logic Simulation                   |

|-----|----------------------------------------------|

| 1:  | for each SSBDD in the model do               |

| 2:  | take the first node of current SSBDD         |

| 3:  | while current node is not a terminal node do |

| 4:  | evaluate the current node                    |

| 5:  | move to proper next node                     |

| 6:  | end <b>while</b>                             |

| 7:  | save output value of current SSBDD           |

| 8:  | end for                                      |

logic in the considered design, and thus produces new statistics and information